中央处理器及其制造方法与流程

1.本发明涉及半导体技术领域,尤其涉及一种中央处理器(cpu,central processing unit)及其制造方法。

背景技术:

2.为了解决cpu运算速度与内存读写速度不匹配的矛盾,出现了cpu缓存器。cpu缓存器是位于cpu内核与内存之间的临时数据交换器,它的容量比内存小,但交换速度比内存快。cpu缓存器的容量大小和cpu缓存器距离cpu内核的距离影响了cpu的性能。

3.相关技术中,cpu缓存器一般包括多级,多级cpu缓存器一般均采用静态随机存取存储器(sram,static random

‑

access memory)。然而,受限于sram的容量和体积,cpu的性能不佳。同时,提高cpu的性能和尺寸集成度成为一种挑战。

技术实现要素:

4.为解决相关技术问题,本发明实施例提出一种cpu及其制造方法,能够提供较高性能的cpu以及较好的尺寸集成度。

5.本发明实施例提供了一种cpu,包括:

6.第一半导体结构,所述第一半导体结构至少包括一个内核以及包含有第一导电触点的第一键合层;

7.第二半导体结构,所述第二半导体结构包括第一级至第n级缓存器中部分级或全部级缓存器和包含有第二导电触点的第二键合层;所述部分级或全部级缓存器中不同级的缓存器包括相变存储器中不同层的存储单元层;所述相变存储器包括多层堆叠的存储单元层;所述存储单元层包括多个存储单元;其中,所述n为大于一的正整数;

8.键合结合层,位于所述第一半导体结构和所述第二半导体结构之间;其中,所述第一导电触点在所述键合结合层处与所述第二导电触点电性连接。

9.上述方案中,所述第一半导体结构包括一个内核、与所述内核信号连接的第一级缓存器、以及包含有第一导电触点的第一键合层;

10.所述第二半导体结构包括第二级至第n级缓存器和包含有第二导电触点的第二键合层;所述第二级至第n级缓存器中不同级的缓存器包括相变存储器中不同层的存储单元层;其中,所述n为大于二的正整数。

11.上述方案中,所述n等于四,所述第二半导体结构包括第二级至第四级缓存器和包含有第二导电触点的第二键合层;

12.其中,所述cpu断电时的运行状态和数据快照存储于所述第四级缓存器中。

13.上述方案中,所述第二半导体结构包括:

14.第二衬底;

15.位于所述第二衬底上的所述第二级至第n级缓存器;

16.位于所述第二级至第n级缓存器上的所述第二键合层;

17.所述第一半导体结构包括:

18.位于所述第二键合层上的所述第一键合层;

19.位于所述第一键合层上的所述内核以及所述第一级缓存器;

20.位于所述内核以及所述第一级缓存器上的第一衬底。

21.上述方案中,所述第一半导体结构包括:

22.第一衬底;

23.位于所述第一衬底上的所述内核以及所述第一级缓存器;

24.位于所述内核以及所述第一级缓存器上的所述第一键合层;

25.所述第二半导体结构包括:

26.位于所述第一键合层上的所述第二键合层;

27.位于所述第二键合层上的所述第二级至第n级缓存器;

28.位于所述第二级至第n级缓存器上的第二衬底。

29.本发明实施例又提供一种cpu的制造方法,包括:

30.形成第一半导体结构;所述第一半导体结构至少包括一个内核以及包含有第一导电触点的第一键合层;

31.形成第二半导体结构;所述第二半导体结构包括第一级至第n级缓存器中部分级或全部级缓存器和包含有第二导电触点的第二键合层;所述部分级或全部级缓存器中不同级的缓存器包括相变存储器中不同层的存储单元层;所述相变存储器包括多层堆叠的存储单元层;所述存储单元层包括多个存储单元;其中,所述n为大于一的正整数;

32.在所述第一半导体结构和所述第二半导体结构之间形成键合结合层;其中,所述第一导电触点在所述键合结合层处与所述第二导电触点电性连接。

33.上述方案中,形成的第一半导体结构包括一个内核、与所述内核信号连接的第一级缓存器、以及包含有第一导电触点的第一键合层;

34.形成的第二半导体结构包括第二级至第n级缓存器和包含有第二导电触点的第二键合层;所述第二级至第n级缓存器中不同级的缓存器包括相变存储器中不同层的存储单元层;所述相变存储器包括多层堆叠的存储单元层;所述存储单元层包括多个存储单元;其中,所述n为大于二的正整数。

35.上述方案中,当所述n等于四时,形成的所述第二半导体结构包括第二级至第四级缓存器和包含有第二导电触点的第二键合层;

36.其中,所述cpu断电时的运行状态和数据快照存储于所述第四级缓存器中。

37.上述方案中,所述形成第一半导体结构,包括:

38.提供第一衬底;

39.在所述第一衬底上形成所述内核以及所述第一级缓存器;

40.在所述内核以及所述第一级缓存器上形成所述第一键合层;

41.所述形成第二半导体结构,包括:

42.提供第二衬底;

43.在所述第二衬底上形成所述相变存储器,以形成所述第二级至第n级缓存器;

44.在所述第二级至第n级缓存器上形成所述第二键合层。

45.上述方案中,在形成所述键合结合层后,

46.所述第一半导体结构形成在所述第二半导体结构的上方;

47.或者,

48.所述第一半导体结构形成在所述第二半导体结构的下方。

49.本发明实施例提供了一种cpu及其制造方法,其中,所述cpu包括:第一半导体结构,所述第一半导体结构至少包括一个内核以及包含有第一导电触点的第一键合层;第二半导体结构,所述第二半导体结构包括第一级至第n级缓存器中部分级或全部级缓存器和包含有第二导电触点的第二键合层;所述部分级或全部级缓存器中不同级的缓存器包括相变存储器中不同层的存储单元层;所述相变存储器包括多层堆叠的存储单元层;所述存储单元层包括多个存储单元;其中,所述n为大于一的正整数。键合结合层,位于所述第一半导体结构和所述第二半导体结构之间;其中,所述第一导电触点在所述键合结合层处与所述第二导电触点电性连接。本发明实施例中,采用相变存储器中不同层的存储单元层作为cpu的多级缓存器中的部分级或全部级缓存器,并且cpu的部分级或全部级缓存器与内核之间是通过键合的方式连接在一起的。本领域技术人员可以理解的是,相变存储器具有较高的位密度,即具有较高的容量和较小体积,基于此,在cpu运行的过程中,较高的容量可以使得更多的数据通过cpu的缓存器来进行交换,从而提高缓存数据的使用量;同时,较小体积也可以缩短cpu中各级缓存器之间的距离,从而减少cpu内核到各级缓存器的延迟,而将cpu的多级缓存器集中在同一个相变存储器中,可以极大的缩小各级缓存器之间的距离,从而进一步减小cpu内核到各级缓存器之间的延迟;并且,集中在同一个相变存储器中的多级缓存器所在的第二半导体结构,与cpu内核所在的第一半导体结构之间,通过键合的方式连接在一起,可以进一步节省cpu的尺寸,提高cpu的尺寸集成度。如此,本发明实施例提供的cpu具有较佳的性能以及较好的尺寸集成度。

附图说明

50.图1a为本发明实施例提供的一种计算机的存储系统的结构示意图;

51.图1b为本发明实施例提供的一种cpu的组成结构布局示意图;

52.图2为本发明实施例提供的一种存储单元阵列的架构的结构示意图;

53.图3为本发明实施例提供的一种存储单元阵列与多级缓存器的对应结构示例图;

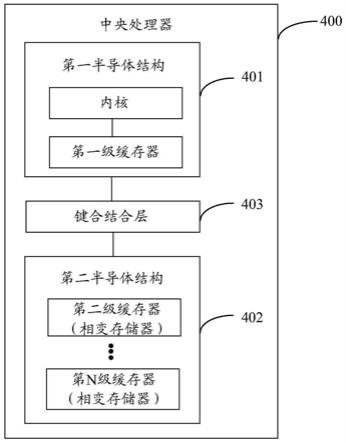

54.图4为本发明实施例提供的又一种cpu的组成结构示意图;

55.图5a为本发明实施例提供的又一种计算机的存储系统的结构示意图;

56.图5b为本发明实施例提供的又一种计算机的存储系统断电状态下数据存储示意图;

57.图5c为本发明实施例提供的又一种计算机的存储系统运行状态下数据存储示意图;

58.图6a为本发明实施例提供的又一种cpu的组成结构示意图;

59.图6b为图6a虚线框中的结构示意放大图;

60.图6c为本发明实施例提供的另一种cpu的组成结构示意图;

61.图7为本发明实施例提供的又一种cpu的制造方法的实现流程示意图;

62.图8为本发明实施例提供的另一种cpu的制造方法的实现流程示意图;

63.图9a

‑

图9j为本发明实施例提供的又一种cpu的制造过程的剖视示意图;

64.图10为本发明实施例cpu的控制方法的实现流程示意图。

具体实施方式

65.为使本发明实施例的技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对发明的具体技术方案做进一步详细描述。

66.由于不同的存储技术在存储速度和造价上相差巨大,为了高效的访问数据,计算机的存储系统中将最常用的数据放在读存速度快的存储设备上,而将不常用的数据放在读存速度慢的存储设备上。存储器系统是一个具有不同容量、成本和访问时间的存储设备的层级结构。如图1a所示,从左向右设置的cpu的缓存器、主存储器、磁盘存储器的容量越来越大,但访问速度越来越慢。比如,cpu访问自身的多级缓存器(图1a中的l1、l2、l3)的速度大概在0.1纳秒(ns);cpu的缓存器与主存储器之间的交互速度在ns级,主存储器与磁盘存储器的交互速度在微秒(us)级。左边的存储器作为右边存储器的缓冲区域来存储访问频率更高的数据。靠近cpu内核的多级缓存器是内存上一部分数据和指令的缓冲区域。主存储器缓存磁盘存储器上的数据,而这些磁盘存储器又常常作为存储在通过网络连接的其他机器的磁盘或磁带上的数据的缓冲区域。

67.基于存储器系统的上述架构,cpu的多级缓存器的配置在很大程度上影响着cpu的性能,甚至影响着计算机的性能。相关技术中,如图1b所示,cpu的多级缓存器(l1、l2、l3)均由密集的高速sram组成。由于sram本身的低位密度特征,在一些情况下,采用sram的缓存器占用cpu芯片中硅衬底一半甚至更多的尺寸。sram的大尺寸,导致多级缓存器间的距离较远、互连线rc延迟较大。此外,嵌入的sram的良率也会影响cpu的良率。

68.实际应用中,相变存储器是一种使用硫族化合物作为存储介质的存储技术,利用材料在不同状态下的电阻差异来保存数据。相变存储器具有可按位寻址、断电后数据不丢失、存储密度高、读写速度快等优势,被认为是最有前景的下一代存储器。

69.基于此,在本发明实施例中,采用相变存储器中不同层的存储单元层作为cpu的多级缓存器中的部分级或全部级缓存器,并且cpu的部分级或全部级缓存器与内核之间是通过键合的方式连接在一起的。本领域技术人员可以理解的是,相变存储器具有较高的位密度,即具有较高的容量和较小体积,基于此,在cpu运行的过程中,较高的容量可以使得更多的数据通过cpu的缓存器来进行交换,从而提高缓存数据的使用量;同时,较小体积也可以缩短cpu中各级缓存器之间的距离,从而减少cpu内核到各级缓存器的延迟,而将cpu的多级缓存器集中在同一个相变存储器中,可以极大的缩小各级缓存器之间的距离,从而进一步减小cpu内核到各级缓存器之间的延迟;并且,集中在同一个相变存储器中的多级缓存器所在的第二半导体结构,与cpu内核所在的第一半导体结构之间,通过键合的方式连接在一起,可以进一步节省cpu的尺寸,提高cpu的尺寸集成度。如此,本发明实施例提供的cpu具有较佳的性能以及较好的尺寸集成度。

70.将非易失性相变存储器作为cpu的第二级至第n级缓存器的方案的优势可以包括:

71.1、基于多级缓存器(可以是第一级至第n级缓存器,也可以是第二级至第n级缓存器)中的不同级缓存器采用同一相变存储器的不同层存储单元层,cpu内核与多级缓存器之间的数据传输速度显著提高,cpu逻辑电路的rc延迟时间更短;

72.2、提高cpu缓存效率并减小密集型多级缓存的尺寸和缓存数据的使用量;

73.3、在cpu内核与第一级缓存器所在的第一半导体结构,与第二级至第n级缓存器所在的第二半导体结构之间,通过键合的方式连接在一起的情况下,可以进一步减少cpu的尺寸,提高cpu的尺寸集成度;

74.4、由同一相变存储器的不同层存储单元层形成的多级缓存器,可以单独调整相变存储器,以平衡cpu性能和cpu数据保留时间;

75.5、相变存储器作为非易失性存储器可以合并纠错功能以确保数据准确性;

76.6、相变存储器作为密度更高的存储器,可以使cpu内核效率更高,系统速度更快,同时印制电路板(pcb,printed circuit board)尺寸更小、管芯尺寸更小;

77.7、可以在断电之前快速存储cpu状态和数据的快照,以使断电前的cpu状态和数据能够快速恢复;

78.8、cpu芯片的成本更低,可以推动cpu芯片在人工智能(ai,artificial intelligence)应用上的潜力迸发。

79.本发明实施例提供一种cpu。所述cpu,包括:

80.至少一个内核;

81.与所述内核信号连接的多级缓存器;其中,所述多级缓存器中不同级的缓存器包括相变存储器中不同层的存储单元层;所述相变存储器包括多层堆叠的存储单元层;所述存储单元层包括多个存储单元。

82.这里,cpu可以包括一个内核,也可以包括多个内核。所述多级缓存器可以理解为两级及两级以上的缓存器,实际应用中,多级缓存器可以包含三级或四级缓存器。多级缓存器依次相连,下一级缓存器作为上一次缓存器的缓存,即内核与第一级缓存器相连,第一级缓存器作为内核的缓存;第一级缓存器与第二级缓存器相连,第二级缓存器作为第一级缓存器的缓存;第二级缓存器与第三级缓存器相连,第三级缓存器作为第二级缓存器的缓存,以此类推。

83.这里,所述相变存储器包括存储单元阵列和外围电路;其中,所述存储单元阵列可以与所述外围电路集成在相同管芯上,这允许更宽的总线和更高的操作速度。

84.所述相变存储器的存储单元阵列包括多层堆叠的存储单元模块;多层堆叠的存储单元模块中的每一存储单元模块包括堆叠设置的第一地址线层、存储单元层以及第二地址线层;其中,所述第一地址线层和所述第二地址线层平行;所述第一地址线层的地址线与第二地址线层的地址线互相垂直;所述存储单元层中的每一存储单元与所述第一地址线层的地址线和第二地址线层的地址线均垂直。

85.实际应用中,所述第一地址线层可以包括字线层,对应地所述第二地址线层可以包括位线层;或者,第一地址线层可以包括位线层,对应地第二地址线层可以包括字线层。第一地址线层可以包括多条字线或者位线;第二地址线层可以包括多条位线或者字线;多个存储单元中的每个存储单元可以包括一个相变存储元件、一个选通元件及多个电极。

86.示例性的,如图2所示,所述存储单元模块的架构包括:位线层、存储单元层以及字线层;其中,存储单元层中的每个存储单元20可以包括堆叠的相变存储元件202、选通元件204以及多个电极201、203及205。通过选通元件204的导通实现电极对相变存储元件202的加热或淬火,以实现相变存储元件202的晶态与非晶态之间的切换;通过相变存储元件202的晶态与非晶态之间的切换实现数据的存储。

87.所述相变存储器的外围电路包括用于便于相变存储器操作的任何合适的数字、模拟和/或混合信号电路。例如,外围电路可以包括控制逻辑、数据缓冲器、解码器(解码器也可以称为译码器)、驱动器及读写电路等。当控制逻辑收到读写操作命令及地址数据时,在控制逻辑的作用下,解码器可以基于解码的地址将从驱动器产生的相应电压施加到相应的位线、字线上,以实现数据的读取操作或者写操作,并通过数据缓冲器与外部进行数据交互。

88.本发明实施例中,所述多级缓存器可以包括多级具有不同缓存速度的缓存器;所述相变存储器可以包括多层堆叠结构设置的存储单元层。所述多级缓存器中不同级的缓存器包括所述相变存储器中不同层的存储单元层可以理解为:多级缓存器中的部分或全部不同级的缓存器可以对应相变存储器中的多层存储单元层中不同层的存储单元层,具体地,可以是多级缓存器中的某几级缓存器一一对应于相变存储器中的多层存储单元层中各层存储单元层,也可以是多级缓存器中的全部级缓存器一一对应于相变存储器中的多层存储单元层中各层存储单元层;还可以是多级缓存器中的不同级缓存器对应于相变存储器中的多层存储单元层中不同层存储单元层,且多级缓存器中的某一级缓存器对应于相变存储器中的多层存储单元层中的某多层。也就是说,多级缓存器与多层存储单元层之间既可以是一一对应的关系,也可以是一对多的对应关系,并且,多级缓存器既可以是全部级缓存器对应同一相变存储器,也可以是部分级缓存器对应同一相变存储器。

89.考虑到cpu不同级缓存器的缓存速度不同,为了匹配不同的缓存速度,相变存储器中对应不同级缓存器的不同层的相变存储单元层的存储速度必需不同。实际应用中,该不同层的相变存储单元层可以通过使用不同的相变材料、或者设置不同厚度的相变存储元件、或者使用不同的介电材料、或者设置不同厚度的地址线层等来达到存储速度不同的目的。

90.考虑到实现的便利性,下面以相变存储器中不同级缓存器对应的不同层的存储单元层采用不同的相变材料为例,来解释说明如何实现对应不同级缓存器的不同层存储单元层的存储速度不同,以响应不同级缓存器的速度要求。

91.本领域技术人员可以理解的是,相变存储器是通过相变材料的非晶态与晶态之间的可逆转变实现数据的存储,而不同相变材料的非晶态与晶态之间的转换速度不同,因此,相变存储器的不同层的存储单元层采用不同的相变材料,可以使得相变存储器中的不同层的存储单元层具有不同的存储速度。

92.实际应用中,在一些实施例中,所述相变存储器中对应不同级缓存器的不同层的存储单元层采用具有不同的转换速度的相变材料;所述转换速度包括所述相变材料的第一状态与第二状态之间转换的速度。

93.这里,转换速度可以理解为某层存储单元层采用的相变材料的非晶态与晶态之间的转换速度。为了使所述相变存储器中对应不同级缓存器的不同层的存储单元层的缓存速度不同,各存储单元层采用了具有不同转换速度的相变材料。这样,多级缓存器中的各级缓存器的存储速度可根据相变材料的不同而不同,从而可以实现多级缓存器的缓存速度和存储能力逐级变化。

94.下面将进一步详细介绍多级缓存器与所述相变存储器中多层相变存储层之间的对应关系。

95.在一些实施例中,所述相变存储器包括m层堆叠的存储单元层;所述多级缓存器包括n级缓存器;其中,所述m为大于一的正整数;所述n为大于一的正整数;

96.若m等于n,所述相变存储器中m个不同层的存储单元层分别对应所述n级缓存器中n个不同级的缓存器;

97.若m大于n,所述相变存储器中j个不同层的存储单元层对应所述n级缓存器中第n级的缓存器;其中,j=m

‑

n+1;

98.若m小于n,所述相变存储器中m个不同层的存储单元层分别对应所述n级缓存器中第k级至第n级的缓存器;其中,k=n

‑

m+1。

99.实际应用中,针对m等于n的情况:

100.所述相变存储器中m个不同层的存储单元层分别与所述n级缓存器中n个不同级的缓存器一一对应。也就是说,所述相变存储器中的第一存储单元层用于作为第一级缓存器;所述相变存储器中的第二存储单元层用于作为第二级缓存器,以此类推,所述相变存储器中的第m层存储单元层用于作为第n级缓存器。

101.示例性的,m=n=2时,多级缓存器为二级缓存器,相变存储器包括两层堆叠的存储单元层,此时,所述相变存储器中位于底部的第一存储单元层用于作为二级缓存器中的第一级缓存器;所述相变存储器中位于所述第一存储单元层上的第二存储单元层用于作为二级缓存器中的第二级缓存器。

102.示例性的,m=n=4时,多级缓存器为四级缓存器,相变存储器包括四层堆叠的存储单元层,此时,所述相变存储器中位于底部的第一存储单元层用于作为四级缓存器中的第一级缓存器;所述相变存储器中位于所述第一存储单元层上的第二存储单元层用于作为四级缓存器中的第二级缓存器;所述相变存储器中位于第二存储单元层上的第三存储单元层用于作为四级缓存器中的第三级缓存器;所述相变存储器中位于第三存储单元层上的第四存储单元层用于作为四级缓存器中的第四级缓存器。

103.实际应用中,针对m大于n的情况:

104.所述相变存储器中m个不同层的存储单元层对应所述n级缓存器中n个不同级的缓存器。此时,所述相变存储器中的第一存储单元层用于作为n级缓存器中的第一级缓存器;所述相变存储器中的第二存储单元层用于作为n级缓存器中的第二级缓存器,以此类推,所述相变存储器中剩余的m

‑

n+1个层存储单元层用于作为n级缓存器中的第n级缓存器;也就是说,n级缓存器中的第一级缓存器至第n

‑

1级缓存器,分别与所述相变存储器中n

‑

1个不同层的存储单元层一一对应,所述n级缓存器中第n级的缓存器对应所述相变存储器中m

‑

n+1个不同层的存储单元层。

105.示例性的,如图3所示,m=4,n=3时,多级缓存器为三级缓存器,相变存储器包括四层堆叠的存储单元层,那么,所述相变存储器中位于底部的第一存储单元层用于作为三级缓存器中的第一级缓存器;所述相变存储器中位于所述第一存储单元层上的第二存储单元层用于作为三级缓存器中的第二级缓存器;所述相变存储器中位于第二存储单元层上的第三存储单元层及第四存储单元层用于作为三级缓存器中的第三级缓存器。

106.实际应用中,在一些实施例中,所述第一存储单元层中存储单元的相变材料包括二元相变材料;所述第二存储单元层中存储单元的相变材料包括未掺杂的三元相变材料;所述第三存储单元层中存储单元的相变材料包括具有掺杂元素的三元相变材料。

107.这里,所述二元相变材料可以包括ga

‑

sb、in

‑

sb、ge

‑

te、ge

‑

sb、sb

‑

te等系列合金材料,基于二元相变材料制作的薄膜,其特点是电学性能较为优异,晶化温度低,晶化速率快,基于此,采用二元相变材料制作的第一存储单元层读写操作速度较快。所述三元相变材料主要包括ge

‑

sb

‑

te合金材料,基于未掺杂的三元相变材料制作的薄膜,相较于二元相变材料其特点是热稳定性增强,非晶态与晶态之间的可逆转变的操作次数增多,也就意味着,采用三元相变材料制作的第二存储单元层读写操作的速度减慢,而可重复擦写的次数增多,存储能力增强。通过对未掺杂的三元相变材料进行掺杂n、sn、bi、si、c和in等元素,其结果显示,掺杂后的三元相变材料不仅可以在原有(未掺杂的三元相变材料)的基础上改善薄膜的热稳定性、降低器件的功耗、还可以提高晶态电阻或者降低熔点等;但同时,采用具有掺杂元素的三元相变材料制作的第三存储单元层相较于采用未掺杂的三元相变材料制作的第二存储单元层而言,读写操作速度减慢,而存储能力增强。

108.因此,采用二元相变材料、未掺杂的三元相变材料以及具有掺杂元素的三元相变材料分别作为所述相变存储器的不同存储单元层的制作材料,可以使得所述相变存储器的缓存速度逐层递减,存储能力逐层递增,以达到多级缓存器的存储速度逐级递减,存储能力逐级递增的目的。

109.示例性的,所述第一存储单元层中存储单元采用的相变材料包括锑碲(sb

‑

te);所述第二存储单元层中存储单元采用的相变材料包括锗锑碲(ge

‑

sb

‑

te);所述第三存储单元层及第四存储单元层中存储单元采用的相变材料包括掺杂氮元素(n)的锗锑碲(ge

‑

sb

‑

te)。

110.实际应用中,二元合金sb

‑

te因其具有更高的晶化速率被广泛用于光学存储的相变材料,这是由于sb

‑

te相变材料的结晶机制是生长型,生长型机制有利于加快结晶;三元相变材料ge

‑

sb

‑

te系列合金中,综合性能比较优异的是ge2sb2te5和gesb2te4,基于这两种材料制作的薄膜晶化速率快(纳秒量级),非晶态和晶态之间的电阻率差异大,且非晶态与晶态之间具有较好的可逆性;而通过对ge

‑

sb

‑

te系列相变材料中进行掺杂n、sn、bi、si、c和in等元素,使得掺杂后的ge

‑

sb

‑

te相变材料的热稳定性增强,例如掺杂n元素,可以使ge2sb2te5薄膜的晶格发生畸变,掺杂的n元素与ge键合,生成gen,对晶粒有明显的细化作用,可以提高晶化速率;而且从对掺杂材料性能测试的结果中还可以反映出掺杂后的三元相变材料可以提高结晶温度。

111.实际应用中,可以根据实际情况对掺杂元素的掺杂量进行调整,本领域技术人员可以理解的是掺杂元素的掺杂量越高,相变材料的稳定性以及电阻率的提高效果越显著。

112.这里,sb

‑

te、ge

‑

sb

‑

te以及掺杂n元素的ge

‑

sb

‑

te相变材料的非晶态与晶态之间的转换速率是逐渐递减的,热稳定性逐渐增强,因此,采用上述三者作为所述相变存储器的不同层存储单元层的相变材料,可以匹配所述相变存储器中各存储单元层的不同的存储速度的需求。

113.实际应用中,针对m小于n的情况:

114.所述相变存储器中m个不同层的存储单元层对应所述n级缓存器中部分个不同级的缓存器。此时,所述相变存储器中的第一存储单元层用于作为n级缓存器中的第k级缓存器;所述相变存储器中的第二存储单元层用于作为n级缓存器中的第k+1级缓存器;以此类推,所述相变存储器中第m层存储单元层用于作为n级缓存器中第k+m

‑

1级缓存器;其中,第k

+m

‑

1级缓存器即为第n级缓存器,也即k=n

‑

m+1。

115.示例性的,m=2,n=3,多级缓存器为三级缓存器,所述相变存储器包括两层堆叠的存储单元层,即第五存储单元层和第六存储单元层;那么,所述相变存储器中位于底部的第五存储单元层用于作为所述三级缓存器中的第二级缓存器;所述相变存储器中位于所述第五存储单元层上的第六存储单元层用于作为所述三级缓存器中的第三级缓存器。

116.本发明实施例提供了一种cpu,包括:至少一个内核;与所述内核信号连接的多级缓存器;其中,所述多级缓存器中不同级的缓存器包括相变存储器中不同层的存储单元层;所述相变存储器包括多层堆叠的存储单元层;所述存储单元层包括多个存储单元。本发明实施例中,cpu中多级缓存器中不同级的缓存器采用同一相变存储器中不同层的存储单元层。本领域技术人员可以理解的是,将cpu的多级缓存集中在一个相变存储器中可以极大的缩小各级缓存器之间的距离,从而减小cpu内核到各级缓存器之间的延迟。同时,相变存储器本身具有较高的位密度,即具有较小体积和较高的容量;相变存储器较小的体积可以使cpu最终尺寸明显的减小,从而进一步减少cpu内核到多级缓存器的延迟;在cpu运行的过程中,相变存储器较高的容量可以使得更多的数据通过多级缓存器来进行交换,从而提高缓存数据的使用量,如此,本发明实施例提供的cpu具有较佳的性能。

117.将同一非易失性相变存储器的多层的存储单元层作为cpu的多级缓存器的方案的优势可以包括:

118.1、基于多级缓存器采用同一相变存储器的不同层存储单元层,cpu内核与多级缓存器之间的数据传输速度显著提高,rc延迟时间更短;

119.2、利用改变相变材料的方式易于实现不同级缓存器存储速度的匹配;

120.3、提高cpu缓存效率并减小密集型多级缓存的尺寸和提高缓存数据的使用量;

121.4、相变存储器作为非易失性存储器可以合并纠错功能以确保数据准确性;

122.5、相变存储器作为密度更高的存储器,可以使cpu内核效率更高,系统速度更快,同时pcb板尺寸更小、管芯尺寸更小;

123.6、cpu芯片的成本更低,可以推动cpu芯片在ai应用上的潜力迸发。

124.本发明实施例又提供一种cpu。图4为本发明实施例又提供的cpu 400的组成结构示意图。如图4所示,所述cpu 400,包括:

125.第一半导体结构401,所述第一半导体结构401至少包括一个内核以及包含有第一导电触点的第一键合层;

126.第二半导体结构402,所述第二半导体结构402包括第一级至第n级缓存器中部分级或全部级缓存器和包含有第二导电触点的第二键合层;所述部分级或全部级缓存器中不同级的缓存器包括相变存储器中不同层的存储单元层;所述相变存储器包括多层堆叠的存储单元层;所述存储单元层包括多个存储单元;其中,所述n为大于一的正整数;

127.键合结合层403,位于所述第一半导体结构401和所述第二半导体结构402之间;其中,所述第一导电触点在所述键合结合层处与所述第二导电触点电性连接。

128.这里,所述cpu包括堆叠设置的第一半导体结构401和第二半导体结构402。第一半导体结构中至少包括一个内核。实际应用中,当cpu包括多个内核时,第一半导体结构中还可以包括多个内核。同时,除内核以外,第一半导体结构中还可以包括多级缓存器中的部分级缓存器。

129.具体地,当cpu的第一级至第n级缓存器中全部级缓存器均对应于同一个相变存储器,即全部级缓存器中的不同级缓存器均对应于同一相变存储器中的不同层存储单元层时,则该全部级缓存器设置在第二半导体结构中;此时,第一半导体结构中不包括缓存器,仅包括内核。

130.当cpu的第一级至第n级缓存器中部分级缓存器均对应于同一个相变存储器,而存在剩余的部分级缓存器未对应在该相变存储器中,则该部分级缓存器设置在第二半导体结构中;而未对应在该相变存储器的剩余的部分级缓存器设置在第一半导体结构中。此时,第一半导体结构中既包括内核,也包括部分级缓存器。

131.示例性地,多级缓存器中第一级缓存器对应于其他存储器(例如sram),第二级至第n级缓存器对应于同一个相变存储器,即多级缓存器中的第二级至第n级缓存器均对应于同一相变存储器中的不同层存储单元层时,多级缓存器中的第二级至第n级缓存器设置在第二半导体结构中;此时,内核和第一级缓存器设置在第一半导体结构中。

132.示例性地,当多级缓存器中第一级至第二级缓存器对应于其他存储器(例如sram),第三级至第n级缓存器对应于同一个相变存储器,即多级缓存器中的第三级至第n级缓存器均对应于同一相变存储器中的不同层存储单元层时,多级缓存器中的第三级至第n级缓存器设置在第二半导体结构中;此时,内核、第一级缓存器和第二级缓存器设置在第一半导体结构中。

133.基于此,在一些实施例中,所述第一半导体结构401包括一个内核、与所述内核信号连接的第一级缓存器、以及包含有第一导电触点的第一键合层;

134.所述第二半导体结构402包括第二级至第n级缓存器和包含有第二导电触点的第二键合层;所述第二级至第n级缓存器中不同级的缓存器包括相变存储器中不同层的存储单元层;其中,所述n为大于二的正整数。

135.可以理解的是,为了实现两个半导体结构键合,在第一半导体结构401中还设置有第一键合层,在第二半导体结构402中还设置有第二键合层。所述第一键合层可以包括:第一介质层,贯穿第一介质层的多个第一沟槽,位于第一沟槽中的第一导电触点。所述第二键合层可以包括:第二介质层,贯穿第二介质层的第二沟槽,位于第二沟槽中第三阻挡层表面的第二导电触点。这里,第一键合层和第二键合层中的对应结构的形貌可以相同也可以不同,具体的,第一导电触点的径宽(这里,径宽可以理解为沿第一沟槽宽度方向的截面的宽度)与第二导电触点的径宽可以相等也可以不同。实际应用中,所述第一沟槽及第二沟槽的截面可以是圆形、椭圆形或长条形等;所述第一介质层及所述第二介质层的材料包括但不限于氧化硅、氮化硅、氮氧化硅、低k电介质或其任何组合;所述第一导电触点及所述第二导电触点的材料可以包括导电材料,包括但不限于钨(w)、钴(co)、铜(cu)、铝(al)、硅化物或其任何组合。

136.这里,第一键合层与第二键合层之间键合界面既存在金属(导电触点)又存在电介质物质的键合。在一些具体的实施例中,第一导电触点和第二导电触点通过接触的方式导电连接;当第一介质层和第二介质层的材料均包括氧化硅时,第一介质层和第二介质层通过二者表面的si

‑

oh键反应形成si

‑

o

‑

si键而结合在一起。第一介质层和第二介质层结合在一起形成的结合层即为键合结合层。

137.实际应用中,所述第二级至第n级缓存器中不同级的缓存器包括相变存储器中不

同层的存储单元层;所述相变存储器包括存储单元阵列;所述存储单元阵列包括多层堆叠的存储单元层;所述存储单元层包括多个存储单元;其中,所述n为大于二的正整数;

138.可以理解的是,上述第二级至第n级缓存器中不同级的缓存器可以对应相变存储器中的多层存储单元层中不同层的存储单元层,其中,可以是第二级至第n级缓存器中不同级的缓存器一一对应于相变存储器中的多层存储单元层中各层存储单元层,也可以是第二级至第n级缓存器中的每一级缓存器对应于相变存储器中的多层存储单元层;也就是说,第二级至第n级缓存器中不同级的缓存器与多层存储单元层之间既可以是一一对应的关系,也可以是一对多的对应关系。

139.这里,所述相变存储器包括存储单元阵列和外围电路;其中,所述存储单元阵列可以与所述外围电路集成在相同管芯上,这允许更宽的总线和更高的操作速度。

140.实际应用中,所述n等于四,所述第二半导体结构包括第二级至第四级缓存器和包含有第二导电触点的第二键合层;

141.其中,所述cpu断电(英文可表达为power off)时的运行状态和数据快照存储于所述第四级缓存器中。

142.这里,如图5a所示,在cpu运行状态下,对于cpu的四级缓存器:l1,l2,l3,l4而言,级别越小越接近cpu,所以速度也更快。就像数据库缓存一样,获取数据时首先会在最快的缓存中找数据,如果缓存没有命中,则往下一级找,直到四级缓存器中都找不到时,那只有向内存索要数据了。随着未命中次数的增加,代表获取数据消耗的时长增长。

143.实际应用中,如图5b所示,将cpu的运行状态和数据存储在第四级缓存器即相变存储器中,由于相变存储器为非易失性存储器,所以在cpu断电后,cpu的运行状态和数据仍存储在其中。cpu在供电恢复后,如图5c所示,不需要从磁盘中将cpu的运行状态和数据复制到主存储器中,而是直接读取保留在第四级缓存器中的cpu的运行状态和数据快照,由于不需要启动磁盘的载入程序,cpu快速恢复正常运行得到了很大的提升。

144.实际应用中,所述第一半导体结构401可以设置在第二半导体结构402的上方。

145.基于此,在一些实施例中,

146.所述第二半导体结构402包括:

147.第二衬底4021;

148.位于所述第二衬底4021上的所述第二级至第n级缓存器4022;

149.位于所述第二级至第n级缓存器4022上的所述第二键合层4023;

150.所述第一半导体结构401包括:

151.位于所述第二键合层4023上的所述第一键合层4014;

152.位于所述第一键合层4014上的所述内核4012以及所述第一级缓存器4013;

153.位于所述内核以及所述第一级缓存器上的第一衬底4011。

154.示例性地,如图6a所示,所述第一半导体结构401包括:第一衬底4011、内核4012以及第一级缓存器4013。其中,所述第一衬底4011的材料包括但不限于硅。

155.所述第二半导体结构402包括:第二衬底4021和第二级至第n级缓存器4022。其中,所述第二衬底4021的材料包括但不限于硅,实际应用中,第二衬底4021可以根据实际需求进行掺杂。

156.所述键合结合层403包括:第一键合层4014和第二键合层4023。

157.为了便于更清楚的理解多级缓存器与相变存储单元层之间的对应关系,图6b示出了图6a中虚线框部分的放大图。这里,第二级至第n级缓存器4022中不同级的缓存器对应于相变存储器中不同层的存储单元层;其中,相变存储器包括存储单元阵列和外围电路;存储单元阵列包括多层堆叠的存储单元层;存储单元层包括多个存储单元。

158.实际应用中,所述第二半导体结构402还包括地址线互连层,所述地址线互连层包括图6a中示出的连接结构(英文可以表达为contact),通过所述地址线互连层中的连接结构将相变存储器的字线或者位线与相变存储器的外围电路连接。

159.实际应用中,所述第一半导体结构401可以设置在第二半导体结构402的下方。

160.基于此,在一些实施例中,

161.所述第一半导体结构401包括:

162.第一衬底4011;

163.位于所述第一衬底4011上的所述内核4012以及所述第一级缓存器4013;

164.位于所述内核4012以及所述第一级缓存器4013上的所述第一键合层4014;

165.所述第二半导体结构402包括:

166.位于所述第一键合层4014上的所述第二键合层4023;

167.位于所述第二键合层4023上的所述第二级至第n级缓存器4022;

168.位于所述第二级至第n级缓存器4022上的第二衬底4021。

169.示例性的,如图6c所示,将cpu的至少一个内核与第一级缓存器设置于第一半导体中,第二级至第四级缓存器设置于第二半导体中,第一半导体结构可以设置在第二半导体结构的下方;与图6a中的结构细节类似,这里不再赘述。

170.在一些实施例中,所述cpu还包括位于顶部衬底上的电引出结构404;所述cpu通过所述电引出结构404与外部器件连接;所述顶部衬底为第一衬底4011和第二衬底4021中位置处于上方的衬底;

171.所述电引出结构404包括:位于所述顶部衬底中的通孔4041;位于所述通孔中的导电柱塞4042;位于所述顶部衬底上的再布线层4043;以及位于所述再布线层上的焊垫4044。

172.实际应用中,所述电引出结构404可以设置在cpu的顶部,用于将cpu中需要与外部器件连接的部件引出,以便于与外部器件连接。这里,所述外部器件是指该cpu在使用时需要与该cpu连接的外界电路、外界装置、或外界系统等。电引出结构404具体可以参考图6a中所示。

173.这里,顶部衬底为设置在cpu的顶部的衬底。示例性地,当第二半导体结构402设置在第一半导体结构401的上方时,顶部衬底可以指第二衬底4021。示例性地,当第一半导体结构401设置在第二半导体结构402的上方时,顶部衬底可以指第一衬底4011。

174.实际应用中,导电柱塞4042一般包括导电材料,包括但不限于铜。最终可以通过焊垫4044与外部器件实现电连接。

175.在一些实施例中,所述第一半导体结构401还包括第一互连层4015;所述内核以及所述第一级缓存器通过所述第一互连层4015与所述第一导电触点连接;

176.所述第二半导体结构402还包括第二互连层4025;所述第二级至第四级缓存器通过所述第二互连层4025与所述第二导电触点连接。

177.实际应用中,第一互连层4015和第二互连层4025具体可以参考图6a所示。图6a中

还展示出了相应互连层中部分进行连接的连接线。

178.本发明实施例又提供了一种cpu,包括:第一半导体结构,所述第一半导体结构至少包括一个内核以及包含有第一导电触点的第一键合层;第二半导体结构,所述第二半导体结构包括第一级至第n级缓存器中部分级或全部级缓存器和包含有第二导电触点的第二键合层;所述部分级或全部级缓存器中不同级的缓存器包括相变存储器中不同层的存储单元层;所述相变存储器包括多层堆叠的存储单元层;所述存储单元层包括多个存储单元;其中,所述n为大于一的正整数;键合结合层,位于所述第一半导体结构和所述第二半导体结构之间;其中,所述第一导电触点在所述键合结合层处与所述第二导电触点电性连接。本发明实施例中,第二级至第n级缓存器所在的第二半导体结构,与cpu内核和第一级缓存器所在的第一半导体结构之间,通过键合的方式连接在一起,可以进一步减少cpu的尺寸,提高cpu的集成度。

179.本发明实施例又提供一种cpu的制造方法,以得到前述的cpu。图7为本发明实施例cpu的制造方法的实现流程示意图。如图7所示,所述方法包括以下步骤:

180.步骤701:形成第一半导体结构;所述第一半导体结构至少包括一个内核以及包含有第一导电触点的第一键合层;

181.步骤702:形成第二半导体结构;所述第二半导体结构包括第一级至第n级缓存器中部分级或全部级缓存器和包含有第二导电触点的第二键合层;所述部分级或全部级缓存器中不同级的缓存器包括相变存储器中不同层的存储单元层;所述相变存储器包括多层堆叠的存储单元层;所述存储单元层包括多个存储单元;其中,所述n为大于一的正整数;

182.步骤703:在所述第一半导体结构和所述第二半导体结构之间形成键合结合层;其中,所述第一导电触点在所述键合结合层处与所述第二导电触点电性连接。

183.这里,所述cpu包括堆叠设置的第一半导体结构和第二半导体结构。第一半导体结构中至少包括一个内核。实际应用中,当cpu包括多个内核时,第一半导体结构中还可以包括多个内核。同时,除内核以外,第一半导体结构中还可以包括多级缓存器中的部分级缓存器。

184.前已述及,为便于更清楚简洁的理解本发明的立意,本实施例中,将cpu的至少一个内核以及第一级缓存器设置在第一半导体结构中,而将cpu的第二级至第n级缓存器设置在第二半导体结构中,该两个半导体结构通过键合后形成cpu。

185.图8为本发明另一实施例cpu的制造方法的实现流程示意图。如图8所示,所述方法包括以下步骤:

186.步骤801:形成第一半导体结构;所述第一半导体结构包括一个内核、与所述内核信号连接的第一级缓存器、以及包含有第一导电触点的第一键合层;

187.步骤802:形成第二半导体结构;所述第二半导体结构包括第二级至第n级缓存器和包含有第二导电触点的第二键合层;所述第二级至第n级缓存器中不同级的缓存器包括相变存储器中不同层的存储单元层;所述相变存储器包括多层堆叠的存储单元层;所述存储单元层包括多个存储单元;其中,所述n为大于二的正整数;

188.步骤803:在所述第一半导体结构和所述第二半导体结构之间形成键合结合层;其中,所述第一导电触点在所述键合结合层处与所述第二导电触点电性连接。

189.需要说明的是,步骤803与步骤703相同。步骤701、702、703与步骤801、802、803中

的形成方法相同,这里以步骤801、802、803为例进行说明。应当理解,图8中所示的操作并非排他的,也可以在所示操作中的任何操作之前、之后或之间执行其他操作。图9a

‑

图9j为本发明实施例提供的一种cpu的制造过程的剖视图的示例。下面结合图8、图9a

‑

图9j描述本实施例的cpu的形成方法。

190.其中,在步骤801中,主要形成cpu的内核、cpu的第一级缓存器。

191.在一些实施例中,所述形成第一半导体结构401,包括:

192.提供第一衬底4011;

193.在所述第一衬底4011上形成所述内核4012以及所述第一级缓存器4013;

194.在所述内核4012以及所述第一级缓存器4013上形成所述第一键合层4014;

195.其中,在一些实施例中,在所述第一衬底4011上形成所述内核4012以及所述第一级缓存器4013之后,在所述内核4012以及所述第一级缓存器4013上形成第一互连层4015;

196.相应地,在所述第一互连层上形成所述第一键合层,以使所述内核以及所述第一级缓存器通过所述第一互连层与所述第一导电触点连接。

197.实际应用中,上述过程可以参考图9a

‑

图9c,形成内核用于实现运算器功能的运算功能元件以及用于实现控制器功能的控制功能元件;同时形成多级缓存器中第一级缓存器。相关技术中对于内核以及第一级缓存器的制造比较成熟,这里不再赘述。

198.实际应用中,形成第一互连层4015的方法包括:形成介质层;在所述介质层中形成贯穿介质层且延伸至待连接结构中的孔或沟槽;在所述孔或沟槽中填充导电材料,以形成第一互连层。这里,所述介质层可以包括氧化硅,所述导电材料可以包括铜或钨。

199.实际应用中,形成第一键合层4014的过程可以包括:形成第一介质层;在所述第一介质层中形成第一沟槽;向所述第一沟槽中填充金属材料,形成导电触点。这里,形成第一介质层的方式可以是热氧化法或沉积法;例如,热氧化法的氧化气氛可以是干氧氧化、水汽氧化及湿氧氧化;沉积法可以是物理气相沉积、化学气相沉积及溅射等方式。形成沟槽的方式可以包括刻蚀,例如,干法刻蚀。填充金属材料方式可以是常用的金属沉积方法。

200.在步骤802中,主要形成cpu的第二级至第n级缓存器。这里,所述第二级至第n级缓存器中不同级的缓存器包括相变存储器中不同层的存储单元层。

201.在一些实施例中,所述形成第二半导体结构402,包括:

202.提供第二衬底4021;

203.在所述第二衬底4021上形成所述相变存储器,以形成所述第二级至第n级缓存器4022;

204.在所述第二级至第n级缓存器4022上形成所述第二键合层4023。

205.其中,在一些实施例中,在所述第二级至第n级缓存器4022后,在所述存储单元阵列上形成第二互连层4025;

206.相应地,在所述第二互连层4025上形成所述第二键合层4023,以使所述相变存储器通过所述第二互连层4025与所述第二导电触点连接。

207.这里,第二级至第n级缓存器4022对应同一相变存储器。

208.实际应用中,如图9d所示,形成相变存储器的外围电路4024。外围电路4024可以包括互补金属氧化物半导体(cmos,complementary metal oxide semiconductor)晶体管及该晶体管的控制电路。形成所述相变存储器的外围电路4024的晶体管及相关控制电路的具

体过程可以包括:先在衬底(如硅衬底)上形成p型阱区(pwell)和n型阱区(nwell),分别在pwell进行n掺杂,在nwell进行p掺杂,形成所需半导体掺杂区;然后,在衬底表面以上形成金属栅极,得到包含晶体管的外围电路及相关控制电路。

209.接下来,如图9e所示,形成地址线互连层,以通过地址线互连层中的连接结构将相变存储器的存储单元阵列与外围电路4024连接。

210.接下来,如图9f所示,形成所述相变存储器的存储单元阵列。实际应用中,形成存储单元阵列的方法可以包括:

211.采用逐层堆叠的方式依次形成多层堆叠的存储单元模块;其中,每一层存储单元模块的制造方法包括:

212.形成第一地址线层;

213.在所述第一地址线层上形成存储单元层;

214.在所述存储单元层上形成第二地址线层;其中,所述第一地址线层和所述第二地址线层平行;所述第一地址线层的地址线与所述第二地址线层的地址线互相垂直;所述存储单元层中的每一存储单元与所述第一地址线层的地址线和第二地址线层的地址线均垂直。实际应用中,所述第一地址线层可以包括字线层,对应地所述第二地址线层可以包括位线层;或者,第一地址线层可以包括位线层,对应地第二地址线层可以包括字线层。第一地址线层可以包括多条字线或者位线;第二地址线层可以包括多条位线或者字线。实际应用中,所述字线或位线的材料可以包括钨。第一地址线层与第二地址线层平行,并且第一地址线层的地址线(字线或位线)与第二地址线层的地址线(位线或字线)垂直;多个存储单元中的每一存储单元与所述第一地址线层和第二地址线层均垂直。所述每个存储单元包括:依次层叠设置的第一电极层、选通层、第二电极层、相变存储层和第三电极层。这里,字线层、位线层以及存储单元之间的相对位置关系以及存储单元的结构均可以参考图2。

215.实际应用中,形成相应第一地址线层的地址线或相应第二地址线层的地址线的步骤,包括:沉积导体层;对所述导体层进行图案化处理;对进行图案化处理后的导体层进行刻蚀,形成相应第一地址线层的地址线或相应第二地址线层的地址线。

216.实际应用中,可以采用逐层堆叠的方式依次形成多层堆叠的存储单元模块。例如,具有四层堆叠的存储单元层的相变存储器可以采用逐层堆叠的方式依次形成四层堆叠的存储单元模块,在一些实施例中,相邻接触的地址线可以合并为一个地址线。实际应用中,形成相应存储单元的步骤包括:在相应的第一地址线层上依次沉积第一电极层、选通层、第二电极层、相变材料层及第三电极层;对所述第一电极层、选通层、第二电极层、相变材料层及第三电极层进行图案化处理;对进行图案化处理后的所述第一电极层、选通层、第二电极层、相变材料层及第三电极层进行刻蚀,形成相应存储单元。

217.可以理解的是,形成相应的存储单元,即为形成第二级至第n级缓存器4022。

218.接下来,如图9g所示,形成第二级至第n级缓存器的第二互连层4025。实际应用中,形成第二互连层4025的具体方式与前述形成第一互连层4015的具体方式类似,这里不再赘述。

219.接下来,如图9h所示,形成第二级至第n级缓存器的第二键合层4023。实际应用中,形成第二键合层4023的具体方式与前述形成第一键合层4014的具体方式类似,这里不再赘述。

220.需要说明的是,步骤801和步骤802的执行顺序不受限制,二者可以并行。只要在步骤803前完成即可。

221.在步骤803中,主要是将形成的第一半导体结构401和第二半导体结构402进行键合。

222.实际应用中,如图9i所示,所述键合的方式具体可以包括:将第一半导体结构401中第一键合层4014和第二半导体结构402中第二键合层4023对准,使得第一导电触点与第二导电触点相接触。随后,通过加热,使得二者的导电触点电性连接在一起,而两个半导体结构的非金属区的氢离子和氧离子互相结合,使得第一半导体结构401和第二半导体结构402的非金属区键合在一起。在第一半导体结构401和第二半导体结构402相接触之前,还包括:对第一半导体结构401和第二半导体结构402表面进行清洗和离子轰击,使得半导体结构表面游离的氢离子和氧离子增多,便于后续的键合。

223.实际应用中,在进行键合后,还可以在键合结构的顶部形成电引出结构404,如图9j所示。

224.在一些实施例中,所述方法还包括:

225.在顶部衬底上形成电引出结构404;所述顶部衬底为第一衬底和第二衬底中位置处于上方的衬底;所述cpu通过所述电引出结构404与外部器件连接;

226.所述形成电引出结构404,包括:

227.在所述顶部衬底中形成通孔4041;

228.在所述通孔4041中填充导电材料形成导电柱塞4042;

229.在所述顶部衬底上形成再布线层4043;

230.在所述再布线层4043上形成焊垫4044。

231.这里,顶部衬底为设置在cpu的顶部的衬底。示例性地,当第二半导体结构402设置在第一半导体结构401的上方时,顶部衬底可以指第二衬底4021。示例性地,当第一半导体结构401设置在第二半导体结构402的上方时,顶部衬底可以指第一衬底4011,如图9j所示。

232.实际应用中,为了降低形成通孔4041的工艺难度,可以先对顶部衬底进行减薄处理后,再进行通孔刻蚀。导电柱塞4042一般包括导电材料,包括但不限于铜。形成导电柱塞4042方式可以是常用的金属沉积方法。再布线层4043可以通过通孔或过孔的方式实现不同结构间的连接。

233.需要说明的是,第一半导体结构401和第二半导体结构402中需要与外部连接的器件均可以通过第一互连层4015、第二互连层4025及电引出结构404实现电引出。

234.实际应用中,所述n等于四时,形成的所述第二半导体结构包括第二级至第四级缓存器和包含有第二导电触点的第二键合层;

235.其中,所述cpu断电时的运行状态和数据快照存储于所述第四级缓存器中。

236.这里,形成所述第二半导体结构包括第二级至第四级缓存器,其中,在cpu断电时,该cpu的运行状态和数据快照存储于所述第四级缓存器;形成第二级至第四级缓存器的过程前已述及,这里不再赘述。

237.基于前述cpu,本发明实施例提供一种cpu的控制方法。图10为本发明实施例cpu的控制方法的实现流程示意图。如图10所示,所述方法包括以下步骤:

238.步骤1001:cpu的内核接收数据访问请求;其中,所述cpu包括本发明实施例提供的

cpu;

239.步骤1002:查看所述cpu的n级缓存器中的第一级缓存器中是否存在所述请求数据;

240.步骤1003:确定所述第一级缓存器中不存在所述请求数据时,查看所述n级缓存器中的所述第一级缓存器的下一级缓存器中是否存在所述请求数据;

241.步骤1004:确定被查找的缓存器中不存在所述请求数据时,按照缓存器级数依次增加的顺序,继续查看新的下一级缓存器中是否存在所述请求数据,至所述n级缓存器中的第n级缓存器;

242.步骤1005:确定所述第n级缓存器中存在所述请求数据时,返回所述请求数据;确定所述第n级缓存器中不存在所述请求数据时,将主存储器中的相应数据载入所述第n级缓存器中。

243.基于前述的cpu,实际应用中,在读取数据时,从存储器中查询数据的顺序为:先查询第一级缓存,第一级缓存未命中后再查询第二级缓存,按照该规律直到第n级缓存器,当第n级缓存器中未命中后将主存储器中的相应数据载入所述第n级缓存器中。

244.在一些实施例中,所述方法还包括:

245.在所述cpu被重启时,通过查看所述第n级缓存器中存储的所述cpu断电时的运行状态和数据的快照来快速恢复所述cpu的正常运行。

246.实际应用中,将cpu的运行状态和数据存储在第n级缓存器即相变存储器中,由于相变存储器为非易失性存储器,所以在cpu断电后,cpu的运行状态和数据仍存储在其中。cpu在供电恢复后,不需要从磁盘中将cpu的运行状态和数据复制到主存储器中,而是直接读取保留在第n级缓存器中的cpu的运行状态和数据快照,由于不需要启动磁盘的载入程序,cpu快速恢复正常运行得到了很大的提升。

247.在本发明实施例中,采用相变存储器中不同层的存储单元层作为cpu的多级缓存器中的部分级或全部级缓存器,并且cpu的部分级或全部级缓存器与内核之间是通过键合的方式连接在一起的。本领域技术人员可以理解的是,相变存储器具有较高的位密度,即具有较高的容量和较小体积,基于此,在cpu运行的过程中,较高的容量可以使得更多的数据通过cpu的缓存器来进行交换,从而提高缓存数据的使用量;同时,较小体积也可以缩短cpu中各级缓存器之间的距离,从而减少cpu内核到各级缓存器的延迟,而将cpu的多级缓存器集中在同一个相变存储器中,可以极大的缩小各级缓存器之间的距离,从而进一步减小cpu内核到各级缓存器之间的延迟;并且,集中在同一个相变存储器中的多级缓存器所在的第二半导体结构与cpu内核所在的第一半导体结构之间通过键合的方式连接在一起可以进一步节省cpu的尺寸,提高cpu的尺寸集成度。如此,本发明实施例提供的cpu具有较佳的性能以及较好的尺寸集成度。需要说明的是:“第一”、“第二”等是用于区别类似的对象,而不必用于描述特定的顺序或先后次序。

248.另外,本发明实施例所记载的技术方案之间,在不冲突的情况下,可以任意组合。

249.以上所述,仅为本发明的较佳实施例而已,并非用于限定本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1