半导体装置以及半导体装置的制造方法与流程

1.本发明涉及半导体装置以及半导体装置的制造方法。

背景技术:

2.伴随着半导体制造技术的提高,在电路内的每单位面积(单位信息投影面积)搭载更多且高性能的元件的高密度化正在发展。在用于半导体存储器等的电容器元件中,已知有通过在半导体基板形成槽(沟道),并进行三维结构化来增大表面积,从而提高每单位面积的电容密度的方法。

3.另外,在mems(micro electro mechanical systems:微电子机械系统)领域中,作为加工半导体基板的技术已知有博世蚀刻技术。在博世蚀刻技术中,通过一边反复蚀刻步骤和侧壁的钝化步骤一边挖入半导体基板,在半导体基板上形成槽形状。在使用博世蚀刻技术形成的槽的侧面产生鳞片状的凹凸(scallop)。

4.形成有凹凸的面的表面积比平滑的面大。因此,提出了通过以博世蚀刻形成沟道,而在侧壁部分设置凹凸结构来增大表面积,从而使沟道电容器的电容增大的方法(例如,专利文献1、专利文献2)。

5.专利文献1:美国专利申请公开第2012/0127625号公报

6.专利文献2:美国专利10,510,828号

7.通过博世蚀刻形成的鳞片状的凹凸结构的前端附近具有锐角形状(即,尖头形)的凸部。因此,在利用在侧壁表面具有凹凸结构的沟道来形成电容器(沟道电容器)的情况下,形成于沟道的侧壁表面的电容绝缘膜在凹凸结构的锐角形状的部分薄膜化。另外,在向对置电极施加电压时,电场集中在该锐角形状的部分。这些均存在导致电容绝缘膜的耐压降低的问题。

8.另外,在通过博世蚀刻形成了凹凸结构的侧壁的表面,也会产生比该凹凸结构小的、被识别为表面粗糙的等级的微小的凹凸。在这样的微小的凹凸的角的部分也会产生电容绝缘膜的薄膜化、电场集中,仍然存在成为电容绝缘膜的耐压降低的因素的问题。

技术实现要素:

9.本发明是鉴于上述问题点而完成的,目的在于提供一种能够使沟道电容器的电容增大并且抑制电容绝缘膜的耐压降低的半导体装置。

10.本发明的半导体装置的特征在于,具有:半导体基板;沟道,从上述半导体基板的一个面朝向内部延长,在侧壁表面具有凹凸结构;半导体膜,形成为覆盖上述沟道的侧壁表面且从上述侧壁表面连续地沿上述半导体基板的上述一个面延伸;对置电极,具有第一部分和第二部分,其中,上述第一部分设置于隔着上述半导体膜与上述半导体基板对置的位置,上述第一部分沿上述半导体基板的上述一个面延伸,上述第二部分从上述第一部分连续地延伸以填充上述沟道;以及绝缘膜,使上述半导体膜与上述对置电极绝缘。

11.另外,本发明的半导体装置的制造方法的特征在于,包含:通过博世蚀形成沟道的

步骤,其中,上述沟道从半导体基板的一个面朝向内部延长;形成半导体膜的步骤,上述半导体膜形成为覆盖上述沟道的侧壁表面且从上述侧壁表面连续地沿上述半导体基板的上述一个面延伸;在上述半导体膜的表面形成绝缘膜的步骤;以及在上述绝缘膜上形成对置电极的步骤,其中,上述对置电极具有第一部分和第二部分,上述第一部分沿上述半导体基板的上述一个面延伸,上述第二部分从上述第一部分连续地延伸以填充上述沟道。

12.根据本发明的半导体装置,能够抑制电容绝缘膜的耐压降低,并且增大沟道电容器的每单位面积的电容。

附图说明

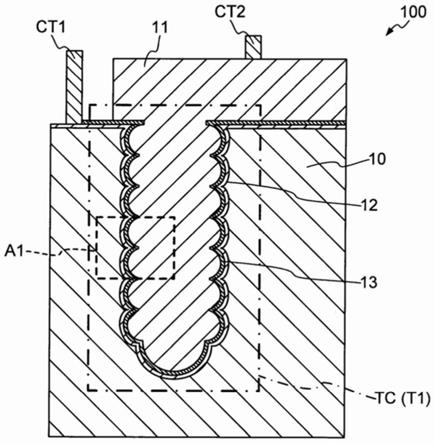

13.图1a是表示本发明的实施例1的半导体装置的结构的剖视图。

14.图1b是放大地表示图1a的用虚线包围的部分的图。

15.图2是表示实施例1的半导体装置的制造过程的流程图。

16.图3a是表示比较例的半导体装置的结构的剖视图。

17.图3b是放大地表示图3a的用虚线包围的部分的图。

18.图4a是示意性地表示比较例的沟道电容器的基板表面的一部分的剖视图。

19.图4b是放大地表示比较例的沟道电容器的表面的一部分的剖视图。

20.图5a是表示本发明的实施例2的沟道电容器的结构的剖视图。

21.图5b是放大地表示图5a的用虚线包围的部分的图。

22.图6是表示实施例2的半导体装置的制造过程的流程图。

23.图7是表示本发明的实施例3的半导体装置的结构的剖视图。

24.图8是表示实施例3的半导体装置的制造过程的流程图。

25.图9a是表示本发明的实施例3的沟道电容器的电容绝缘膜的形成工序中的表面的一部分的剖视图。

26.图9b是表示本发明的实施例3的沟道电容器的退火处理后的表面的一部分的剖视图。

27.图10是表示本发明的实施例4的半导体装置的结构的剖视图。

28.图11是表示实施例4的半导体装置的制造过程的流程图。

29.图12a是表示本发明的实施例4的沟道电容器的电容绝缘膜的形成工序中的表面的一部分的剖视图。

30.图12b是表示本发明的实施例4的沟道电容器的退火处理后的表面的一部分的剖视图。

31.附图标记说明:100...半导体装置;10...半导体基板;11...对置电极;12...多晶硅膜;13...电容绝缘膜;14...多晶硅膜;15...多晶硅膜;16...粗糙表面多晶硅膜。

具体实施方式

32.以下,对本发明的优选的实施例进行详细说明。此外,在以下的各实施例中的说明以及附图中,对实质相同或者等效的部分标注相同的附图标记。

33.[实施例1]

[0034]

图1a是示出本发明的实施例1的半导体装置100的结构的剖视图。半导体装置100

包括:半导体基板10以及对置电极11。在半导体基板10形成有沟道电容器tc。

[0035]

半导体基板10例如由硅(si)基板构成。在半导体基板10的构成元件搭载区域的面(以下,称为一个面),形成有多晶硅膜12以及电容绝缘膜13。

[0036]

在半导体基板10的一个面,形成有朝向内部延长的槽形状的凹部(以下,称为沟道t1)。沟道t1与形成于表面的多晶硅膜12以及电容绝缘膜13一起构成沟道电容器tc。

[0037]

通过利用博世蚀刻对半导体基板10进行沟道加工来形成沟道t1。在博世蚀刻中,一边反复蚀刻步骤和侧壁的钝化步骤一边挖入基板。因此,在蚀刻侧面形成鳞片状的凹凸(scallop)。

[0038]

因此,本实施例的沟道t1在侧壁表面具有由多个凹部以及凸部构成的凹凸结构。在该凹凸结构中,凹部具有相对带圆角的形状,相对于此凸部的前端附近具有锐角形状(即,尖头形)。换言之,沟道t1的侧壁表面的凹凸结构中的凸部的宽度比凹部的宽度小。各个凹部例如具有1~2μm左右的大小。

[0039]

对置电极11由多晶硅(poly

‑

si)构成。对置电极11形成为隔着电容绝缘膜13以及多晶硅膜12与半导体基板10对置。对置电极11具有:形成为沿半导体基板10的一个面延伸的平板状的部分(第一部分)、以及从该平板状的部分连续地朝向半导体基板10的内部延伸以填充半导体基板10的沟道的部分(第二部分)。

[0040]

多晶硅膜12是形成为覆盖沟道t1的内部的表面(特别是,侧壁表面)且沿半导体基板10的一个面延伸的半导体膜。在本实施例中,通过由未导入杂质的无掺杂的多晶硅(non

‑

dope poly

‑

si)构成的多晶硅膜来构成多晶硅膜12。通过利用lp-cvd法在形成有沟道t1的半导体基板10的表面直接将无掺杂多晶硅成膜来形成多晶硅膜12。

[0041]

电容绝缘膜13是设置于对置电极11与多晶硅膜12之间的绝缘膜。电容绝缘膜13形成于多晶硅膜12的表面,形成为覆盖沟道t1的内部的表面且沿半导体基板10的一个面延伸。电容绝缘膜13例如由氮化硅(sin)膜等绝缘膜构成,例如通过利用lp-cvd法在多晶硅膜12的表面直接将sin成膜来形成。

[0042]

在半导体基板10的一个面设置有触点ct1。触点ct1是接受电压的施加的基板侧的触点,经由多晶硅膜12与半导体基板10连接。

[0043]

在对置电极11的平板状的部分的表面(和与半导体基板10对置的面相反侧的面)设置有触点ct2。触点ct2是接受电压的施加的电极侧的触点,与对置电极11连接。触点ct1以及ct2例如由钨等导电体构成。

[0044]

如上所述,在本实施例的半导体装置100中,使用博世蚀刻技术在半导体基板10形成有沟道t1,利用博世蚀刻的特性,在沟道t1的侧壁形成有鳞片状的凹凸结构(“scallop”)。

[0045]

因此,本实施例的沟道t1的表面积比具有未形成有这样的凹凸结构的平滑的侧壁的沟道大。因此,本实施例的沟道电容器tc的电容器电容比在沟道的侧壁表面未形成有凹凸结构的沟道电容器大。

[0046]

另外,在沟道t1的侧壁表面形成有多晶硅膜12,在多晶硅膜12上还形成有电容绝缘膜13。多晶硅膜12是无掺杂的多晶硅膜,在向对置电极12施加电压时,与半导体基板10同样地动作。即,本实施例的沟道电容器tc具有电容根据施加于对置电极12的电压而变动的特性(所谓mos电容器的c-v特性)。

[0047]

图1b是放大地表示图1a的用虚线包围的部分a1的图。在这里,省略半导体基板10的阴影线。

[0048]

如上所述,在本实施例的半导体装置100中,使用博世蚀刻技术在半导体基板10形成有沟道t1。因此,在沟道t1的侧壁形成有凹凸结构(“scallop”)。另外,利用博世蚀刻的特性,在该侧壁的表面产生比该凹凸结构更小的微小的凹凸部分(以下,称为微小凹凸bu)。微小凹凸bu是识别为所谓表面粗糙的等级的不规则的凹凸结构,具有锐角形状。

[0049]

根据lp-cvd的成膜特性,多晶硅膜12在沟道t1的侧壁表面形成为保持凹凸结构的形状,并且圆润地覆盖锐角形状的部分(例如,在图1b表示为sp的尖头形的凸部)。另外,利用lp-cvd的成膜特性埋入比多晶硅膜12的膜厚小的微小凹凸bu,使形成有微小凹凸bu的部分的侧壁表面平滑化。

[0050]

接下来,参照图2的流程图,对本实施例的半导体装置100的制造方法进行说明。

[0051]

首先,对半导体基板10进行博世蚀刻,形成沟道(step101)。即,反复蚀刻步骤与钝化步骤,并且在半导体基板10形成槽。由此,形成在侧壁部分具有凹凸结构的沟道t1。

[0052]

接下来,利用lp-cvd法,在包含沟道t1的内壁的半导体基板10的表面形成无掺杂的多晶硅膜(step102)。由此,在半导体基板10的表面形成多晶硅膜12。

[0053]

接下来,利用lp-cvd法,在多晶硅膜12的表面形成氮化硅膜(sin)(step103)。此时,在触点ct1的形成位置进行刻画图案以使多晶硅膜12的一部分在晶圆表面露出,之后形成氮化硅膜。由此,形成电容绝缘膜13。

[0054]

接下来,在电容绝缘膜13的表面形成多晶硅层,以填充沟道t1的内部,且沿半导体基板10的一个面延伸。由此,形成多晶硅构成的对置电极11(step104)。

[0055]

接下来,在露出于晶圆表面的多晶硅膜12的表面以及对置电极11的表面形成接触孔,通过钨等导电体填充该接触孔。由此,形成触点ct1以及ct2(step105)。

[0056]

经由以上这样的工序,制造本实施例的半导体装置100。

[0057]

在本实施例的半导体装置100中,由于在多晶硅膜12的表面形成有电容绝缘膜13,因此与未形成有相同的多晶硅膜的情况相比,沟道电容器tc中的电容绝缘膜13的耐压较高。对此,以下进行说明。

[0058]

图3a是示出未形成有本实施例这样的多晶硅膜的比较例的半导体装置500的结构的剖视图。

[0059]

在比较例的半导体装置500中,通过博世蚀刻在半导体基板10形成有沟道,在沟道的侧壁形成有鳞片状的凹凸结构(scallop)。对于这一点,与本实施例的半导体装置100相同。

[0060]

然而,在比较例的半导体装置500中,在沟道t1的侧壁部的表面未形成有多晶硅膜,而仅形成有电容绝缘膜13。即,半导体基板10隔着电容绝缘膜13与对置电极12对置。

[0061]

图3b是放大地表示图3a的用虚线包围的部分a1的图。在比较例的半导体装置500中,在具有通过博世蚀刻形成的凹凸结构的沟道的侧壁表面直接形成有电容绝缘膜13。因此,在沟道侧壁表面的凹凸结构的锐角形状的部分(例如,在图3b中表示为sp的凸部的前端附近),将电容绝缘膜13部分薄膜化。

[0062]

另外,在经由触点ct1以及ct2对对置电极12施加电压时,电场集中在沟道侧壁的凹凸结构的锐角部分(即,凸部的前端附近)。由于这样的电容绝缘膜13的部分薄膜化、以及

施加电压时的向锐角部分的电场集中,而电容绝缘膜13的耐压降低。

[0063]

另外,在通过博世蚀刻形成的沟道的具有凹凸结构的侧壁表面还产生微小的凹凸,在该微小的凹凸的部分也产生电容绝缘膜13的薄膜化以及电场集中。

[0064]

图4a是示意性地示出紧接在博世蚀刻后(即,形成电容绝缘膜13以及对置电极12之前)的沟道的表面的图。根据博世蚀刻的特性,在具有凹凸结构的沟道的侧壁表面产生微小凹凸bu。

[0065]

图4b是示意性地示出形成对置电极后的沟道的表面的图。在比较例的半导体装置500中,在沟道的侧壁表面直接形成电容绝缘膜13。因此,形成于微小凹凸bu的电容绝缘膜13薄膜化。而且,在向对置电极12施加电压时,在微小凹凸bu产生电场集中。这样,由于微小凹凸bu上的电容绝缘膜13的薄膜化以及电场集中,而电容绝缘膜13的耐压降低。

[0066]

与此相对,如图1b所示,在本实施例的半导体装置100中,以圆润地覆盖沟道t1的凹凸结构的锐角形状的部分(例如,在图1b中表示为sp的凸部的前端附近)形成有多晶硅膜12。另外,由于形成于凹凸结构的表面的微小凹凸bu比多晶硅膜12的膜厚小,因此埋入多晶硅膜12,而平滑化。

[0067]

电容绝缘膜13形成于这样的多晶硅膜12的表面,未直接形成于沟道t1的侧壁上的凹凸结构的锐角形状的部分、微小凹凸bu的表面。因此,与比较例的半导体装置500不同,不产生电容绝缘膜13的部分薄膜化,不产生施加电压时的电场集中。

[0068]

因此,根据本实施例的半导体装置100,不产生由电容绝缘膜13的薄膜化、施加电压时的电场集中引起的电容绝缘膜13的耐压降低。

[0069]

如以上那样,在本实施例的半导体装置100中,由于在沟道t1的侧壁形成有凹凸结构,与平滑地形成沟道的侧壁表面的情况相比沟道的表面积较大,因此沟道电容器的电容较大。

[0070]

另外,在本实施例的半导体装置100中,在包含沟道t1的内壁的半导体基板10的表面形成有多晶硅膜12,在多晶硅膜12上形成有电容绝缘膜13。因此,在本实施例的半导体装置100中不产生在具有凹凸结构的沟道的侧壁表面直接形成有电容绝缘膜的情况下成为问题的由电容绝缘膜的薄膜化、施加电压时的电场集中引起的电容绝缘膜的耐压降低。

[0071]

因此,根据本实施例的半导体装置100,能够使沟道电容器tc的每单位面积的电容增大,并且抑制电容绝缘膜的耐压降低。

[0072]

[实施例2]

[0073]

接下来,对本发明的实施例2进行说明。图5a是示出本发明的实施例2的半导体装置200的结构的剖视图。

[0074]

在本实施例的半导体装置200中,在包含沟道t1的内壁的半导体基板10的表面形成有由掺杂有杂质的多晶硅(doped poly

‑

si)构成的多晶硅膜14。即,本实施例的半导体装置200在形成于半导体基板10的表面的多晶硅膜不是无掺杂的多晶硅而是掺杂有杂质的多晶硅这点,与实施例1的半导体装置100不同。

[0075]

图6是表示本实施例的半导体装置200的制造方法的流程图。

[0076]

首先,对半导体基板10进行博世蚀刻,形成沟道(step201)。由此,形成在槽的侧壁具有凹凸结构的沟道t1。

[0077]

接下来,使用lp-cvd法,在包含沟道t1的内壁的半导体基板10的表面形成作为掺

杂有杂质的多晶硅膜的多晶硅膜14(step202)。例如,在利用lp-cvd法进行的多晶硅的成膜中,通过向原料气体导入用于提高导电性的杂质,来形成多晶硅膜14。

[0078]

之后,经由step203~205的工序,制造本实施例的半导体装置200。此外,由于step203~205与实施例1的step103~105(参照图2)相同,因此在这里省略说明。

[0079]

图5b是放大地表示图5a的用虚线包围的部分a1的图。在这里,省略半导体基板10的阴影线。

[0080]

与实施例1的多晶硅膜12同样地、根据lp-cvd的成膜特性,在沟道t1的侧壁表面形成多晶硅膜14,以保持凹凸结构的形状,并且圆润地覆盖锐角形状的部分(即,凸部的前端附近)。另外,利用lp-cvd的成膜特性,埋入比多晶硅膜14的膜厚小的微小凹凸bu,使形成有微小凹凸bu的部分的侧壁表面平滑化。

[0081]

在多晶硅膜14的表面形成有电容绝缘膜13。即,电容绝缘膜13未直接形成于沟道t1的侧壁表面的凹凸结构中的锐角形状的部分、微小凹凸bu的表面。因此,与实施例1同样,不会产生电容绝缘膜13的部分薄膜化,不会产生施加电压时的电场集中。

[0082]

因此,与实施例1的半导体装置100同样地,根据本实施例的半导体装置200,能够使沟道电容器tc的每单位面积的电容增大,并且抑制电容绝缘膜的耐压降低。

[0083]

另一方面,本实施例的半导体装置200在形成于沟道t1的侧壁表面的半导体膜是由掺杂有杂质的多晶硅(doped poly

‑

si)构成的多晶硅膜14这点,与实施例1的半导体装置100不同。即,在本实施例的半导体装置200中,在沟道t1的侧壁部分形成有掺杂有杂质的多晶硅膜14,在基板侧形成有低电阻的多晶硅膜14。因此,向对置电极12施加电压时的沟道电容器tc作为mos电容器,无论施加电压如何都在电荷积蓄侧动作。即,在本实施例的沟道电容器tc中,无论对对置电极12施加的电压如何,都获得大致一定的电容特性。

[0084]

因此,本实施例的半导体装置200在用于旁路电容器等不宜与施加电压相应的电容变动的用途的情况下是有用的。

[0085]

[实施例3]

[0086]

接下来,对本发明的实施例3进行说明。图7是表示本发明的实施例3的半导体装置300的结构的剖视图。

[0087]

在本实施例的半导体装置300中,由导入了杂质的多晶硅构成的多晶硅膜14形成为比实施例2的多晶硅膜14厚(例如,形成为约2倍的厚度)。该多晶硅膜14的厚度的不同起因于多晶硅膜14的形成工序的不同。

[0088]

图8是表示本实施例的半导体装置的制造方法的流程图。

[0089]

首先,对半导体基板10进行博世蚀刻,形成沟道(step301)。由此,形成在槽的侧壁具有凹凸结构的沟道。

[0090]

接下来,向包含沟道的内壁的半导体基板10的表面导入杂质并且通过lp-cvd法将多晶硅成膜(step302)。由此,形成作为掺杂有杂质的多晶硅膜的多晶硅膜14。

[0091]

接下来,通过lp-cvd法,在多晶硅膜14的表面将多晶硅成膜(step303)。此时,与step302不同,不进行杂质的导入。由此,形成无掺杂的多晶硅膜12。

[0092]

接下来,通过lp-cvd法,在多晶硅膜12的表面形成氮化硅膜(sin)(step304)。由此,形成电容绝缘膜13。

[0093]

图9a是放大地表示在step304中形成有电容绝缘膜13的阶段的沟道的一部分的剖

视图。

[0094]

在沟道内部的半导体基板10的表面形成有掺杂有杂质的多晶硅膜14。进一步,在多晶硅膜14的表面形成有无掺杂的多晶硅膜12,在多晶硅膜12的表面形成有电容绝缘膜13。

[0095]

若再次参照图8,则对在表面依次形成有掺杂有杂质的多晶硅膜14、无掺杂的多晶硅膜12、以及电容绝缘膜13的半导体基板10进行热退火处理(step305)。由此,多晶硅膜14中的杂质固相扩散至多晶硅12膜,多晶硅膜14以及多晶硅膜12均成为掺杂有杂质的多晶硅膜。即,将无掺杂的多晶硅以及掺杂多晶硅(掺杂有杂质的多晶硅)的双层结构的膜整体掺杂多晶硅化。

[0096]

之后,与实施例1同样地,进行对置电极11的形成(step306)以及触点ct1以及ct2的形成(step307)。

[0097]

图9b是放大地表示经由上述这样的制造工序制造出的半导体基板10的沟道的一部分的剖视图。通过step305的热退火处理,将无掺杂多晶硅/掺杂多晶硅的双层结构的膜整体掺杂多晶硅化。因此,成为在半导体基板10的表面掺杂有杂质的多晶硅膜14形成为双层的量的膜厚,而在该多晶硅膜14表面形成有电容绝缘膜13的状态。

[0098]

在本实施例中,在无掺杂的多晶硅膜12的表面形成电容绝缘膜13,之后进行热退火处理,以使多晶硅膜12成为掺杂有杂质的多晶硅膜。即,在形成电容绝缘膜13的阶段,其基底表面为无掺杂的多晶硅膜12。

[0099]

若与本实施例不同,在掺杂有杂质的多晶硅膜的表面直接形成电容绝缘膜,则在多晶硅膜的表面出现杂质原子的部位,存在电容绝缘膜的成膜特性局部受到影响的可能性。其结果是,根据情况存在电容绝缘膜的膜质降低,耐压降低的可能性。

[0100]

然而,根据本实施例的制造方法,由于在形成电容绝缘膜13时其基底表面为无掺杂的多晶硅膜12,因此在该基底表面不出现杂质原子。因此,能够避免由杂质原子的影响导致的电容绝缘膜13的膜质降低。

[0101]

而且,在本实施例中,通过热退火处理使无掺杂的多晶硅膜12变化为掺杂有杂质的多晶硅膜14。因此,在制造半导体装置后,与实施例2同样地,无论对对置电极12施加的电压如何,都能够获得大致一定的电容特性。

[0102]

另外,在本实施例的半导体装置中,通过博世蚀刻形成具有凹凸结构的沟道,在包含沟道的内壁的半导体基板的表面隔着多晶硅膜14形成有电容绝缘膜13。因此,与实施例1以及实施例2同样地,能够使沟道电容器tc的每单位面积的电容增大,并且抑制电容绝缘膜的耐压降低。

[0103]

[实施例4]

[0104]

接下来,对本发明的实施例4进行说明。图10是表示本发明的实施例4的半导体装置400的结构的剖视图。

[0105]

在本实施例的半导体装置400中,在形成于半导体基板10的表面的多晶硅膜14中的沟道t1的内壁部分上的多晶硅膜(实施例3的多晶硅膜14)的表面形成有粗糙表面多晶硅膜。它们一体地构成多晶硅膜15。粗糙表面多晶硅膜是表面因半球状的多晶硅粒而变粗糙的多晶硅膜,例如由hsg-si(hemispherical grained si:半球晶硅)构成。

[0106]

图11是表示本实施例的半导体装置的制造方法的流程图。

[0107]

step401~403的工序与实施例3的step301~303的工序相同。即,在通过博世蚀刻形成沟道后(step401),通过lp-cvd法,在半导体基板10的表面形成掺杂有杂质的多晶硅膜14(step402)。然后,通过lp-cvd法,在多晶硅膜14上形成无掺杂的多晶硅膜12(step403)。

[0108]

接下来,使在step403中形成的多晶硅膜12平滑化,在多晶硅膜12的表面形成粗糙表面多晶硅膜(step404)。例如,在沟道t1的内壁的表面形成非晶体化的硅膜。然后,通过对非晶体化的硅膜的表面实施hsg处理,来形成由hsg构成的粗糙表面多晶硅膜。

[0109]

接下来,通过lp-cvd法,在粗糙表面多晶硅膜的表面形成氮化硅膜(sin)(step405)。由此,形成电容绝缘膜13。

[0110]

图12a是放大地表示在step405中形成了电容绝缘膜13的阶段的沟道的一部分的剖视图。

[0111]

在沟道内部的半导体基板10的表面,形成有掺杂有杂质的多晶硅膜14,进一步在多晶硅膜14的表面形成有无掺杂的多晶硅膜12。而且,在多晶硅膜12的表面形成有粗糙表面多晶硅膜16。

[0112]

粗糙表面多晶硅膜16例如具有的凹凸。即,粗糙表面多晶硅膜16的凹凸部分与通过博世蚀刻形成的沟道t1的内壁表面的凹凸结构(例如,1~2μm)相比极小。

[0113]

若再次参照图11,对在表面依次形成了掺杂有杂质的多晶硅膜14、无掺杂的多晶硅膜12、粗糙表面多晶硅膜16、以及电容绝缘膜13的半导体基板10进行热退火处理(step406)。由此,多晶硅膜14中的杂质固相扩散至多晶硅12以及粗糙表面多晶硅膜16,多晶硅膜14、多晶硅膜12以及粗糙表面多晶硅膜16均成为掺杂有杂质的多晶硅膜。

[0114]

之后,与实施例3同样地,进行对置电极11的形成(step407)以及触点ct1以及ct2的形成(step408)。

[0115]

图12b是放大地表示经由上述这样的制造工序制造出的半导体基板10的沟道的一部分的剖视图。通过step406的热退火处理,多晶硅膜14、多晶硅膜12以及粗糙表面多晶硅膜16一体地掺杂多晶硅化,形成在表面包含粗糙表面多晶硅的多晶硅膜15。

[0116]

在本实施例的半导体装置400中,形成有这样的具有包含粗糙表面多晶硅的表面(以下,称为粗表面)的多晶硅膜15,在多晶硅膜15的表面形成有电容绝缘膜13。因此,与在电容绝缘膜13的基底表面未形成有这样的粗表面的情况相比,沟道的表面积较大。

[0117]

另外,如上所述,粗糙表面多晶硅的凹凸部分与沟道t1的侧壁表面的凹凸结构相比,尺寸极小。因此,基于沟道t1的侧壁表面的凹凸结构(“scallop”)的表面积扩大效应、和基于粗糙表面多晶硅的凹凸部分的表面积扩大效应能够叠加。例如,若设定基于通过博世蚀刻形成的凹凸结构的表面积扩大的效应为1.5倍,基于粗糙表面多晶硅的表面积扩大的效应为2倍,则可以获得将它们叠加后的3倍的表面积扩大效应。

[0118]

另外,多晶硅膜15的粗表面的凹凸不具有如通过博世蚀刻产生的微小凹凸bu(即,多晶硅膜15的基底表面的微小凹凸)那样的锐角形状的部分。因此,不会产生由多晶硅膜15的粗表面的凹凸引起的电容绝缘膜13的耐压降低。

[0119]

因此,根据本实施例的半导体装置400,能够抑制电容绝缘膜的耐压降低,并且使沟道电容器tc的每单位面积的电容进一步增大。

[0120]

此外,本发明不限于在上述实施例中示出的内容。例如,在上述的各实施例中,以

使用多晶硅形成对置电极11的情况为例进行了说明。然而,并不局限于此,也可以使用由多晶硅以外的具有导电性的其它材料构成的导电层来构成对置电极11。

[0121]

另外,在上述的各实施例中,对作为用于覆盖沟道的凹凸结构中的锐角形状的部分的半导体膜使用多晶硅膜(无掺杂的多晶硅膜12或者掺杂有杂质的多晶硅膜14、15)的情况进行了说明。然而,并不局限于此,也可以使用多晶硅膜以外的半导体膜。

[0122]

另外,在上述实施例中,在实施例3以及实施例4中对执行热退火处理的例子进行了说明。然而,在实施例1以及实施例2中的每一个实施例中,也可以在形成电容绝缘膜13后执行热退火处理。

[0123]

另外,在上述各实施例中,以通过博世蚀刻形成于沟道的侧壁表面的凹凸结构具有1~2μm左右的大小的凹部的情况为例进行了说明。然而,凹部的大小不限于此。

[0124]

另外,在上述实施例4中,以在通过与实施例3相同的制造工序形成多晶硅膜12后,在多晶硅膜12的表面形成粗糙表面多晶硅膜16的情况为例进行了说明。然而,并不限于此,也可以对实施例1或者实施例2组合粗糙表面多晶硅膜来使用。例如,也可以为在实施例2的多晶硅膜14的表面形成粗糙表面多晶硅膜16,并通过实施热退火处理,来形成整体具有粗表面的多晶硅膜。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1