用于垂直的氮化镓基FET的再生长源极接触的方法和系统与流程

用于垂直的氮化镓基fet的再生长源极接触的方法和系统

1.相关申请的交叉引用

2.本技术要求2020年3月27日提交的标题为“method and system for regrown source contacts for vertical gallium nitride based fets”的美国临时专利申请号63/000,968的优先权权益,据此为了所有目的通过引用将该申请的公开全文并入。

背景技术:

3.电力电子产品广泛用于各种应用中,包括功率转换、电动机驱动器、开关电源、照明等。例如晶体管的电力电子器件通常用于这种电力开关应用中。慢开关速度和高比导通电阻妨碍了当前一代功率晶体管器件、特别是具有高电压(>600v)处理能力的功率晶体管器件的操作。

4.因此,在本领域中需要表现出低电容、低正阈值电压、低比导通电阻(specific on

‑

resistance)以及高击穿电压的功率晶体管器件。

技术实现要素:

5.本发明总体涉及对于给定阈值电压具有泄漏电流、最大电场和导通电阻的改进组合的垂直的基于鳍的场效应晶体管(field effect transistor,fet)器件。本发明的实施例提供了具有改善的比导通电阻、泄漏电流和击穿电压的新颖的垂直的基于鳍的fet器件以及制造这种fet器件的方法。

6.在本发明的一个方面中,一种用于形成对齐接触的方法包括:提供iii族氮化物衬底;在iii族氮化物衬底上外延生长第一iii族氮化物层,其中,第一iii族氮化物层的特征在于第一导电类型;在第一iii族氮化物层上形成第一硬掩模层;使用第一硬掩模层作为掩模在第一iii族氮化物层上形成多个iii族氮化物鳍,其中,多个iii族氮化物鳍中的每一个被多个第一凹进区中的一个分开,其中,多个iii族氮化物鳍的特征在于第一导电类型;在多个第一凹进区中外延生长具有与第一导电类型相反的第二导电类型的iii族氮化物栅极层;在第一硬掩模层和栅极层上形成第一电介质层,其中,第一电介质层包括与多个鳍中的每一个对齐的接触区以及与iii族氮化物栅极层对齐的栅极区;在第一电介质层的栅极区上形成光刻胶层;使用光刻胶层作为掩模蚀刻第一电介质层的接触区,以暴露第一硬掩模层的上表面;去除光刻胶层;去除第一硬掩模层以暴露多个iii族氮化物鳍中的每一个的上表面;以及外延再生长耦合到多个iii族氮化物鳍中的每一个的iii族氮化物源极接触部分。

7.在一个实施例中,iii族氮化物源极接触部分的外延再生长在多个iii族氮化物鳍中的每一个的顶部上是自限制的。

8.在本发明的另一方面中,一种用于形成对齐接触的方法包括:提供iii族氮化物衬底;在iii族氮化物衬底上外延生长第一iii族氮化物层,其中,第一iii族氮化物层的特征在于第一导电类型;在第一iii族氮化物层上形成多个iii族氮化物鳍,其中,多个iii族氮化物鳍中的每一个被多个第一凹进区中的一个分开,其中,多个iii族氮化物鳍的特征在于

第一导电类型;在多个iii族氮化物鳍中的每一个上外延再生长iii族氮化物源极接触部分;以及在iii族氮化物源极接触部分上形成源极接触结构。

9.在本发明的另一方面中,一种用于形成对齐接触的方法包括:提供iii族氮化物衬底;在iii族氮化物衬底上外延生长第一iii族氮化物层,其中,第一iii族氮化物层的特征在于第一导电类型;在第一iii族氮化物层上形成第一硬掩模层;使用第一硬掩模层作为掩模在第一iii族氮化物层上形成多个iii族氮化物鳍,其中,多个iii族氮化物鳍中的每一个被多个第一凹进区中的一个分开,其中,多个iii族氮化物鳍的特征在于第一导电类型;在多个第一凹进区中外延生长具有与第一导电类型相反的第二导电类型的iii族氮化物栅极层;在第一硬掩模层和iii族氮化物栅极层上形成第一电介质层,其中,第一电介质层包括与多个鳍中的每一个对齐的接触区以及与iii族氮化物栅极层对齐的栅极区;在第一电介质层的栅极区上形成光刻胶层;使用光刻胶层作为掩模来蚀刻第一电介质层的接触区以形成第二凹进区,其中,多个iii族氮化物鳍中的每一个的上表面以及围绕多个iii族氮化物鳍中的每一个的iii族氮化物栅极层的上表面的一部分从第二凹进区的底面暴露;去除光刻胶层;在第二凹进区中外延再生长iii族氮化物源极接触部分;以及去除第一电介质层。

10.在本发明的另一方面中,一种用于形成对齐接触的方法包括:提供iii族氮化物衬底;在iii族氮化物衬底上外延生长第一iii族氮化物层,其中,第一iii族氮化物层的特征在于第一导电类型;在第一iii族氮化物层上形成多个iii族氮化物鳍,其中,多个iii族氮化物鳍中的每一个被多个第一凹进区中的一个分开,其中,多个iii族氮化物鳍的特征在于第一导电类型;在多个第一凹进区中外延生长具有与第一导电类型相反的第二导电类型的iii族氮化物栅极层;外延生长覆盖多个iii族氮化物鳍和iii族氮化物栅极层的第二iii族氮化物层,其中,第二iii族氮化物层的特征在于第一掺杂浓度;外延生长耦合到第二iii族氮化物层的第三iii族氮化物层,其中,第三iii族氮化物层的特征在于大于第一掺杂浓度的第二掺杂浓度;形成耦合到第三iii族氮化物层的第一源极金属层;形成耦合到第一源极金属层的第二源极金属层;形成耦合到第二源极金属层的第三源极金属层;形成具有与iii族氮化物栅极层的一部分对齐的开口的源极金属掩模层;蚀刻第一源极金属层、第二源极金属层和第三源极金属层以暴露第三iii族氮化物层的上表面部分;蚀刻第三iii族氮化物层和第二iii族氮化物层以及iii族氮化物栅极层的一部分;以及去除源极金属掩膜层。

11.在一个实施例中,方法还包括:外延生长耦合到iii族氮化物栅极层的未掺杂的iii族氮化物盖层。

12.在一个实施例中,蚀刻第三iii族氮化物层和第二iii族氮化物层以及iii族氮化物栅极层的一部分可以包括:蚀刻掉iii族氮化物栅极层中的未掺杂的iii族氮化物盖层。

13.在本发明的另一方面中,一种晶体管包括:iii族氮化物衬底;在iii族氮化物衬底上的第一iii族氮化物层,其中,第一iii族氮化物层的特征在于第一导电类型;在第一iii族氮化物层上的多个iii族氮化物鳍,其中,多个iii族氮化物鳍中的每一个被多个第一凹进区中的一个分开,其中,多个iii族氮化物鳍的特征在于第一导电类型;在多个第一凹进区中的具有与第一导电类型相反的第二导电类型的iii族氮化物栅极层;以及再生长的iii族氮化物源极接触部分,该接触部分耦合到多个iii族氮化物鳍中的每一个,其中,iii族氮化物源极接触部分的特征在于第一导电类型。

14.在一个实施例中,再生长的iii族氮化物源极接触部分的生长在多个iii族氮化物

鳍中的每一个的顶部上是自限制的。

15.本发明实现了优于传统技术的许多益处。例如,本发明的实施例提供了方法和系统,这些方法和系统利用渐变掺杂区作为用于蚀刻垂直鳍的着陆区,从而最小化蚀刻工艺中的蚀刻深度变化对fet的导通电阻和栅源电容的影响。而且,其它实施例提供了自对齐源极接触,以减少或消除接触形成工艺中的对齐问题,从而最小化寄生电容。另外,一些实施例利用在包括二元iii

‑

v族化合物衬底上的三元iii

‑

v族化合物的渐变掺杂区上的外延再生长的栅极层。

16.三元iii

‑

v族化合物栅极层和二元iii

‑

v族化合物衬底的晶格常数之间的差异以及所引起的应变生成极化电荷,该极化电荷在与栅极层的界面处导致二维电子气(two

‑

dimensional electron gas,2deg)。2deg使得电流能够首先基本上在水平方向上沿着栅极层的横向底面流动,然后在垂直上通过漂移区,从而减小器件中的扩展电阻并且减小器件比导通电阻。通过控制进入渐变掺杂区的蚀刻深度,漏源导通电阻、阈值电压、电场和漏源泄漏电流可以保持在期望的范围内。另外,一些实施例包括对合并的p

‑

i

‑

n/肖特基(merged p

‑

i

‑

n/schottky,mps)二极管和对垂直mosfet的应用。特别地,使用外延再生长的三元iii

‑

v族化合物作为mps二极管中的p型区可以降低二极管的导通电压。渐变掺杂区着陆区对于垂直mosfet具有与对于垂直jfet类似的优点,并且自对齐源极接触也可以应用于垂直mosfet结构。结合下文和附图更详细地描述本发明的这些和其它实施例以及许多其优点和特征。

附图说明

17.附图形成了描述本发明的示例性实施方式的本公开的一部分。附图与说明书一起将说明本发明的原理。

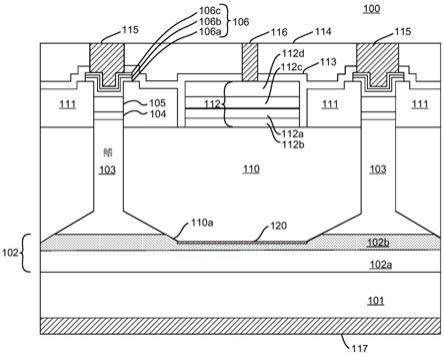

18.图1是根据本公开的实施例的垂直的基于鳍的场效应晶体管(field effect transistor,fet)器件的剖视图。

19.图2是根据本公开的实施例的垂直的基于鳍的fet器件的简化剖视图,例示了从沿着二维电子气(two

‑

dimensional electron gas,2deg)的横向到朝向衬底的垂直的电流流动。

20.图3是根据本公开的实施例的制造垂直的基于鳍的fet器件的方法的简化流程图。

21.图4a至图4i是示出了根据本公开的第一实施例的制造垂直的基于鳍的fet器件的方法的中间阶段的剖视图。

22.图4j至图4m是示出了根据本公开的第二实施例的制造垂直的基于鳍的fet器件的方法的中间阶段的剖视图。

23.图4n至图4u是示出了可以应用于本公开的第一实施例和第二实施例的制造垂直的基于鳍的fet器件的方法的中间阶段的剖视图。

24.图5是具有0.2μm鳍厚度的垂直的基于鳍fet器件的模拟结构。

25.图6是例示了作为蚀刻偏移(以μm为单位)的函数的垂直的基于鳍的fet器件的阈值电压(以v为单位)的曲线图。

26.图7是例示了作为蚀刻偏移(以μm为单位)的函数的垂直的基于鳍的fet器件的电场e(以mv/cm为单位)的曲线图。

27.图8是例示了作为蚀刻偏移(以μm为单位)的函数的垂直的基于鳍的fet器件的沟道泄漏(以a为单位)的曲线图。

28.图9a是例示了正常蚀刻的电流密度的曲线图。

29.图9b是例示了0.1μm过度蚀刻的电流密度的曲线图。

30.图9c是例示了0.2μm过度蚀刻的电流密度的曲线图。

31.图10a是例示了对于正常蚀刻在栅极拐角处的电场的曲线图。

32.图10b是例示了对于0.1μm蚀刻不足在栅极拐角处的电场的曲线图。

33.图10c是例示了0.2μm蚀刻不足的电流密度的曲线图。

34.图11是例示了对于0.2μm渐变外延层的作为蚀刻变化(μm)的函数的导通电阻ron的曲线图。

35.图12是例示了对于0.2μm渐变外延层的作为蚀刻变化(μm)的函数的阈值电压vt(v)的曲线图。

36.图13是例示了对于0.2μm渐变外延层的作为蚀刻变化(μm)的函数的最大电场(mv/cm)的曲线图。

37.图14是例示了对于0.2μm渐变外延层的作为蚀刻变化(μm)的函数的1200v下的高电压漏极泄漏电流idss(a)的曲线图。

38.图15是例示了对于0.3μm渐变外延层的作为蚀刻变化(μm)的函数的导通电阻ron(mω)的曲线图。

39.图16是例示了对于0.3μm渐变外延层的作为蚀刻变化(μm)的函数的阈值电压vt(v)的曲线图。

40.图17是例示了对于0.3μm渐变外延层的作为蚀刻变化(μm)的函数的电场(mv/cm)的曲线图。

41.图18是例示了对于0.3μm渐变外延层的作为蚀刻变化(μm)的函数的1200v下的高电压漏极泄漏电流idss(a)的曲线图。

42.图19a是例示了没有极化电荷对预测在c平面in

0.15

ga

0.85

n/gan界面处产生的电流密度的影响的曲线图。

43.图19b是例示了根据本公开的一些实施例的预测在c平面in

0.15

ga

0.85

n/gan界面处产生的极化电荷的效应的曲线图。

44.图20a是例示了预测在c平面in

0.15

ga

0.85

n栅极层与gan漂移层之间的界面处产生的电场的效应的曲线图。

45.图20b是例示了根据本公开的一些实施例的预测在c平面in

0.15

ga

0.85

n/gan界面处产生的电场的效应的曲线图。该曲线图示出了由于在截止状态下的极化而形成的相对高的电场。

46.图20c是例示了没有极化和有极化的电场的截止状态幅度的曲线图。

47.图21a是例示了通过基线fet的沟道的电流密度的曲线图。图21b是例示了通过非极化fet的沟道的电流密度的曲线图。图21c是与非极化fet的沟道比较的通过基线fet的沟道的电流密度的曲线图。图21d是与非极化fet的能带图比较的基线fet的能带图的曲线图。

48.图22a至图22j是示出了根据本公开的实施例的制造垂直的基于鳍的fet器件的方法的中间阶段的剖视图。

49.图23a至图23g是示出了根据本公开的实施例的制造垂直的基于鳍的fet器件的方法的中间阶段的剖视图。

50.图24a至图24g是示出了根据本公开的实施例的制造垂直的基于鳍的fet器件的方法的中间阶段的剖视图。

具体实施方式

51.下文中将参照附图更充分地描述本公开的实施例。然而,本公开可以以许多不同形式来具体实施,并且不应被解释为限于本文阐述的实施例。相反,提供这些实施例,使得本公开将彻底且完整,并且将向本领域技术人员完全传达本发明的范围。特征可能未等比例绘制,为了清楚起见,一些细节可能相对于其他元素被放大。同样的附图标记自始至终提及同样的元件。

52.本公开的实施例涉及垂直的基于鳍的场效应晶体管(field effect transistor,fet)器件。更具体地,本公开涉及对于给定阈值电压具有改进的泄漏电流、最大电场和导通电阻的垂直的基于鳍的fet器件。仅以示例的方式,本公开涉及方法和具有掺杂漂移区中的渐变掺杂区以及与渐变掺杂区直接接触的再生长外延栅极层的垂直晶体管器件。通过在渐变掺杂区上具有外延再生长的栅极层,可以获得许多优点,例如,与在垂直上通过漂移层朝向衬底相比,首先在沿着栅极层的底部界面层的横向上改善的导通电阻、最大电场和电流流动。

53.图1是根据本公开的实施例的垂直的基于鳍的场效应晶体管器件100的剖视图。术语“fet”、“finfet”和“垂直的基于鳍的fet”在本文中可互换使用。参考图1,fet器件100可以包括半导体衬底101、包括半导体衬底101上的均匀掺杂区102a和均匀掺杂区102a上的渐变掺杂区102b的漂移层102、以及从渐变掺杂区102b突出的多个鳍103。在一个实施例中,各个鳍103可以包括布置在鳍的上部中的重掺杂层104和布置在重掺杂层104上的金属层105,该金属层包括包含难熔金属、难熔金属化合物或难熔金属合金层(例如tin层)的材料。fet器件100还可以包括在金属层105(例如,tin)上的源极接触结构106。源极接触结构106可包括在金属层105上的钛(ti)层106a(例如,tin)、在钛(ti)层106a上的铝(al)层106b、以及在铝(al)层106b上的阻挡(barrier)金属层(例如,钼(mo)、钛(ti)、钽(ta)或类似物)106c。

54.fet器件100还可以包括具有与渐变掺杂区102b直接接触的底部的栅极层110、布置在栅极层110上并围绕鳍103的绝缘层111(例如,电介质(例如,二氧化硅或氮化硅))层、布置在栅极层110上的栅极接触结构112、布置在绝缘层111和栅极接触结构112上的第一层间电介质层113、以及布置在第一层间电介质层113上的第二层间电介质层114。在一个实施例中,栅极接触结构112可以包括布置在栅极层110上的镍(ni)层112a、布置在镍(ni)层112a上的第一金(au)层112b、布置在第一金(au)层112b上的阻挡金属(例如,钼(mo)、钛(ti)、钽(ta)或类似的)层112c、以及布置在阻挡层112c上的第二金(au)层112d。

55.fet器件100还可以包括延伸穿过第一和第二层间电介质层113、114并与源极接触结构106接触的第一过孔接触115、延伸穿过第一和第二层间电介质层113、114并与栅极接触结构112接触的第二过孔接触116、以及在半导体衬底101的底面上的漏极金属接触117。如本文所用的,术语“漂移层”和“漂移区”可互换使用,术语“掺杂层”和“掺杂区”可互换使用,并且术语“渐变掺杂区”和“渐变掺杂层”可互换使用。

56.在一些实施例中,半导体衬底101可以包括n+掺杂的iii族氮化物材料,鳍103可以包括具有第一掺杂浓度的n掺杂的iii族氮化物材料,漂移层102的均匀掺杂区102a可以包括具有低于第一掺杂浓度的第二掺杂浓度的n掺杂的iii族氮化物材料,并且渐变掺杂区102b具有从第二掺杂浓度线性地增加到第一掺杂浓度的第三掺杂浓度。

57.在一个实施例中,第一掺杂浓度为约7.5

×

10

16

原子/cm3,且第二掺杂浓度为约1

×

10

16

原子/cm3。

58.在一个实施例中,漂移区具有约12μm的厚度,渐变掺杂区具有约0.3μm的厚度,并且半导体鳍具有在约0.7μm与0.8μm之间的范围内的高度以及约0.2μm的宽度。

59.在一个实施例中,栅极层110可包括in

x

ga1‑

x

n层,其中,0<x<1,即,x介于0与1之间且不等于0或1。在一个实施例中,栅极层110布置于两相邻鳍之间的凹进区中,且具有一部分110a接触渐变掺杂区102b。栅极层的部分110a的深度(或厚度)可以影响fet器件的阈值电压、电导、最大电场。下面将更详细地描述嵌入在渐变掺杂区中的部分110a的深度(或厚度)的影响。

60.在一个实施例中,fet器件100可包括:半导体衬底101,该半导体衬底可包括n+gan材料层;漏极金属接触117,该漏极金属接触布置在其底面处;n gan漂移层102,该n gan漂移层具有布置在半导体衬底101上的均匀掺杂区102a和布置在均匀掺杂区102a上的渐变掺杂区102b;以及外延gan层,该外延gan层布置在渐变掺杂区上并包括用于形成多个鳍103的凹进区。fet器件还可以包括填充凹进区的栅极层110,例如p型gan栅极层。渐变掺杂区102b可以用作着陆焊盘以确保栅极层110的充分接触。在一个实施例中,栅极层可包括三元化合物半导体层(例如,in

x

ga1‑

x

n层,其中,0<x<1)。在一个实施例中,栅极层110的部分110a可以具有延伸到渐变掺杂区102b中的约0.1μm(+/

‑

0.1μm)的深度(或厚度)。鳍各自可以具有约0.2μm的宽度并且彼此隔开约2.0μm的间隔,即,凹进区或填充两个相邻鳍之间的凹进区的栅极层具有约2.0μm的横向宽度。fet器件还可以包括形成在栅极层110与渐变掺杂区102b之间的界面中的二维电子气(2deg)层120。栅极层110的表面积大,使得电流在沿衬底方向垂直流向漏极金属层117之前沿着2deg层120横向流动,从而提高fet器件的电导(降低导通电阻)。换言之,沟道fet器件具有两个部分,第一部分是控制通过2deg层的电流流动的横向沟道,该沟道在漂移区中有效地分布电流,并且第二部分是垂直沟道,该沟道通过漂移区朝向半导体衬底101和漏极金属层117垂直地承载电流。

61.在一个实施例中,各个鳍可以包括由tin制成的金属层105和多层源极金属结构(例如,ti/al或ti/tin/al的堆叠层,其中,ti与金属层105接触)。fet器件还可以包括绝缘层111,例如栅极层110上的二氧化硅或氮化硅层。绝缘层111包括开口,在该开口处形成与栅极层110接触的栅极接触结构112(即,栅电极)。栅极接触结构112(即,栅电极)具有金属的多层结构,例如,pd/pt/au,其中pd与栅极层110接触,或者ni和au,其中ni被沉积为与栅极层110接触。其它实施例可以包括本领域技术人员已知的其它栅电极金属结构。

62.在一个实施例中,各个鳍可以包括具有彼此平行并且基本上垂直于衬底表面的侧壁的上部和具有彼此不平行并且与衬底表面形成除90度之外的角度的侧壁的下部。平行侧壁可以限定非极化平面,例如m平面。

63.在一个实施例中,2deg层由栅极层与漂移区之间在c平面中的极化诱导,并且垂直流过漂移区的电流沿着m平面。

64.图2是根据本公开的实施例的垂直的fet器件200的简化剖视图,例示了从沿着2deg的横向到朝向衬底的垂直的电流流动。参考图2,垂直fet器件200可以包括衬底201、覆盖衬底201的漂移层202、从漂移层202的表面突出的多个鳍203、在漂移层202上并围绕鳍的栅极层210。fet器件20还可以包括在栅极层210上的栅电极212、以及在栅极层210上并围绕鳍203和栅电极212的电介质层(例如,二氧化硅)211。fet器件20还可以包括二维电子气220,栅极层220在二维电子气中沿着极化平面方向与漂移层202相接。fet器件20还可以包括耦合到鳍203的源电极206。当没有电势施加到栅电极212时,fet器件20处于截止状态。

65.当电势施加到栅电极212时,它调制与漏电极电连通的连续二维电子气(2deg)220。源极电流231在栅极层210下横向流动并垂直流入漏电极217。在一个实施例中,鳍各自具有约0.2μm的宽度,并且以约2.0μm的距离隔开。在栅极层与漂移区的渐变掺杂区之间的界面中形成极化诱导的2deg 220,从而在漂移区中分布电流以提高fet器件的电导。

66.本公开的实施例还提供了一种制造垂直fet器件的方法。图3是根据本公开的实施例的制造具有再生长栅极层的垂直fet器件的方法300的简化流程图。参考图3,提供iii族氮化物衬底(310)。在实施例中,iii族氮化物衬底是具有在大约0.020欧姆

‑

厘米范围内的电阻率的n+gan衬底。在一个实施例中,n+gan衬底的电阻率可为约0.001欧姆

‑

厘米至0.018欧姆

‑

厘米,优选小于0.016欧姆

‑

厘米,更优选小于0.012欧姆

‑

厘米。方法300还包括:形成沉积在iii族氮化物衬底上的第一iii族氮化物外延层,例如12μm厚的第一iii族氮化物外延层(例如,n型gan外延层)(312)。第一iii族氮化物外延层在950℃至1100℃之间的温度下在iii族氮化物衬底上外延生长,并且特征在于第一掺杂浓度,例如具有大约1

×

10

16

原子/cm3的掺杂浓度的n型掺杂。在一些实施例中,第一iii族氮化物外延层是漂移层,包括在iii族氮化物衬底上的均匀掺杂区(层)和在均匀掺杂区上的渐变掺杂区(层)。在实施例中,均匀掺杂区具有约12μm的厚度,渐变掺杂区具有约0.3微米的厚度。在实施例中,衬底310的表面以一定角度从c平面斜切,以促进用于漂移层的高电压操作的高质量外延生长。

67.方法300还包括:在第一iii族氮化物外延层上形成第二iii族氮化物外延层(314)。在实施例中,第二iii族氮化物外延层外延生长在第一iii族氮化物外延层上,厚度为大约0.7μm,并且特征在于第二掺杂浓度,例如n型掺杂。在一些实施例中,第二掺杂浓度高于第一掺杂浓度。在实施例中,第二掺杂浓度为约1.3

×

10

17

原子/cm3。方法300还包括:在第二iii族氮化物外延层上形成金属层并在金属层上形成图案化的硬掩模层,以及使用图案化的硬掩模层作为掩模来图案化金属层(316)。方法300还包括:通过蚀刻工艺(例如,反应离子蚀刻(reactive ion etching,rie)工艺)使用图案化的硬掩模层在第二iii族氮化物外延层中形成凹进区(318)。方法300还包括:在凹进区中再生长第三iii族氮化物外延层(320)。再生长的iii族氮化物外延层可以形成栅极层。在一个实施例中,再生长的iii族氮化物外延层具有与第一和第二iii族氮化物外延层的导电类型相反的导电类型。

68.方法300还包括:在再生长的iii族氮化物外延层上和在图案化的硬掩模层上形成第一电介质层以及在第一电介质层上形成第二电介质层(322)。方法300还包括:去除第二电介质层的一部分以在鳍的上部的相对侧上的第一电介质层的侧壁上形成间隔物(324)。方法300还包括:去除第一电介质层的一部分以暴露再生长的iii族氮化物外延层的表面部分,同时在鳍的相对侧上留下第一电介质层的一部分(326)。方法300还包括:去除间隔物和硬掩模层,同时暴露金属层的表面并保留鳍的相对侧上的第一电介质层的部分(328)。

69.方法300还包括:在再生长的外延iii族氮化物层的暴露表面部分上形成源极掩模层(330)。方法300还包括:在金属层的表面上形成源极接触结构并去除源极掩模层(332)。方法300还包括:形成覆盖源极接触结构的栅极掩模层,同时暴露再生长的iii族氮化物外延层的表面部分,在再生长的iii族氮化物外延层的暴露的表面部分上形成栅极接触结构,以及去除栅极掩模层(334)。方法300还包括:形成覆盖源极接触结构和栅极接触结构的层间电介质层,在层间电介质层上形成图案化的掩模层,蚀刻层间电介质层以形成延伸到源极接触结构的通孔,以及用导电材料填充通孔以形成过孔(336)。注意,可以与形成到源极接触结构的通孔和过孔同时地形成到栅极接触结构的通孔和过孔。

70.应当理解,图3所例示的具体步骤提供了根据本发明实施例的制造具有再生长栅极层的垂直fet器件的特定方法。根据替代实施例,也可以执行其它步骤顺序。例如,本发明的替代实施例可以以不同的顺序执行上述步骤。而且,图3所例示的各个步骤可以包括多个子步骤,这些子步骤可以以适合于各个步骤的各种顺序来执行。此外,根据特定应用,可以添加或去除附加步骤。本领域普通技术人员将认识到许多变更、修改和替换。

71.再次参考图3并参考图4a到图4u,示出了根据本公开的若干实施例的示出制造垂直的基于鳍的fet器件的各种方法的中间阶段的剖视图。参考图4a,提供n+掺杂的iii族氮化物衬底401(方框310)。在950℃至1200℃之间的温度下,优选在1000℃至1150℃之间的温度下,更优选在大约1100℃的温度下,在n+掺杂的iii族氮化物衬底401上外延生长被称为第一半导体层402的第一n掺杂半导体(漂移)层(方框312)。在图4b中,具有约0.3μm厚度的渐变掺杂区460布置在第一与第二半导体层之间,并且具有从约1

×

10

16

原子/cm3线性增加到1.3

×

10

17

原子/cm3(即从第一半导体层朝向第二半导体层线性增加)的掺杂浓度。

72.在950℃至1200℃之间的温度下,优选在1000℃至1150℃之间的温度下,更优选在大约1100℃的温度下,在第一半导体层402上外延生长第二n掺杂半导体层403(方框314)。参考图4b,在第二半导体层403上形成金属层405,并且在金属层405上形成图案化的硬掩模层406(方框316)。在一个实施例中,重n+掺杂层404可以存在于第二半导体层403与金属层405之间,以提高第二半导体层与金属层之间的接触电阻。在实施例中,硬掩模层可包括si3n4,并通过(plasma enhanced chemical vapor deposition,pecvd)在约300℃下形成有约400nm的厚度。在实施例中,图案化的硬掩模层406可以使用rie通过基于f的化学过程形成。在实施例中,省略金属层405。

73.在实施例中,n+掺杂的iii族氮化物衬底401重掺杂有n型掺杂剂,掺杂剂的掺杂浓度在约5

×

10

17

原子/cm3到约1

×

10

19

原子/cm3的范围内,电阻率小于0.020欧姆

‑

厘米。在一个实施例中,n+掺杂的iii族氮化物衬底的电阻率可以从大约0.001欧姆

‑

厘米到0.018欧姆

‑

厘米,优选地小于0.016欧姆

‑

厘米,更优选地小于0.012欧姆

‑

厘米。第一半导体层402是在约1

×

10

16

原子/cm3的掺杂浓度范围内具有约12μm厚度的漂移层。第二半导体层403是具有约1.3

×

10

17

原子/cm3的n型掺杂剂和约12μm厚度的均匀掺杂区的鳍导电层。金属层405可以包括tin,并且硬掩模层406可以包括氮化硅。在一些附图中,为了清楚起见,省略了渐变掺杂区460和重n+掺杂层404。

74.参考图4c,使用图案化硬掩模406作为掩模执行蚀刻工艺以形成多个鳍403’(方框318)。在一些实施例中,鳍各自具有约0.2μm的宽度、在约0.7μm至0.8μm之间的范围内的高度,并且彼此隔开约2μm的间距,即,鳍间距为约2μm。为了实现鳍的均匀高度,需要蚀刻工艺

的深度的良好可控性。根据本公开,蚀刻工艺可以包括使用rie的基于cl的化学过程,并且被进行为去除第二半导体层403的一部分以形成凹进区408。在实施例中,当去除约0.1μm的渐变掺杂区460时,蚀刻工艺可以停止。使用渐变掺杂区来减轻蚀刻工艺变化或公差的电效应,如以下将进一步详细描述的。

75.注意,在蚀刻工艺之后,鳍的底部可以具有与图4c所示的形状不同的形状。本公开的实施例在本文中参考是本发明的理想化实施例(和中间结构)的示意图的剖视图来描述。为了清楚起见,附图中的层和区域的厚度可以被放大。另外,预期来自作为例如制造技术和/或公差的结果的、例示的形状的变化。由此,本发明的实施例不应被解释为限于本文所例示的区域的特定形状,而是包括例如因制造而产生的形状的偏差。在以下附图中,鳍的底部被示出为与渐变掺杂区的表面具有90度角,即,鳍被示出为具有横截面矩形形状。理解,鳍的底部可以具有圆形或弯曲的特征。由此,图中例示的区域本质上是示意性的,并且它们的形状不旨在例示器件的区域的实际形状,并且不旨在限制本发明的范围。

76.在一个实施例中,在形成沟槽之后,使用约25重量%的tmah溶液在约85℃的温度下进行清洁工艺,且持续约30分钟的持续时间。在另一实施例中,在使用tmah溶液执行清洁之前,还可以执行预清洁,例如2分钟的使用h2so4:h2o以2:1的体积比的皮伦尼亚(piranha)清洁。

77.参考图4d,在清洁之后,在凹进区408中外延生长第三半导体层407(方框320)。在实施例中,第三半导体层407可包括p型gan层,该层在大约950℃的温度下在沟槽中非共形地生长,直到基本上与金属层405’的底部(或硬掩模406’,在省略金属层405’时)相平的厚度。在一个实施例中,第三半导体层407的厚度为约840nm。p型gan层可以用约1

×

10

19

原子/cm3的掺杂浓度掺杂mg。p型gan层可以用约1

×

10

19

原子/cm3的掺杂浓度掺杂mg。其后,执行热退火(例如,在n2中在850℃下快速热退火5分钟)以激活mg掺杂原子。然后,在p型gan层中以大于10重量%的量激活mg原子。在一个实施例中,重n+掺杂层404的剩余部分(如图4b所示)可以存在于鳍403’与金属层405’之间,以改善鳍403’与金属层405’之间的接触电阻。

78.在第一实施例中,参考图4e,可以在第三半导体层407上执行平坦化工艺。在实施例中,平坦化工艺包括:通过蚀刻去除第三半导体层407的上部。在实施例中,平坦化工艺包括:去除约0.2μm的第三半导体层407的上部。

79.其后,至少在第四电介质半导体层407的平坦化表面上形成第一电介质层410a,并且第一电介质层基本上与鳍的侧壁、金属层405’和硬掩模406'共形。在实施例中,第一电介质层410a具有大约100nm的厚度,并且可以包括si3n4,并且通过pecvd在大约300℃下沉积。第二电介质层410b形成于第一电介质层410a上。在实施例中,第二电介质层410b具有大约100nm的厚度,并且可以包括sio2,并且通过pecvd在大约300℃下沉积。第三电介质层410c形成于第二电介质层410b上。在实施例中,第三电介质层410c具有大约400nm的厚度,并且可以包括si3n4,并且通过pecvd在大约300℃下沉积。

80.参考图4f,回蚀第三电介质层410c(如图4e所示)以在第二电介质层410b的侧壁上形成间隔物412a。在一个实施例中,间隔物412a在足部处具有约300nm的宽度。

81.参考图4g,使用基本各向同性的蚀刻来蚀刻第二电介质层410b,以暴露平坦化区域407和硬掩模406’上方的第一电介质层410a的顶部。在一个实施例中,蚀刻使用例如缓冲hf的湿法蚀刻剂;在另一实施例中,蚀刻使用基于f的等离子体蚀刻。在蚀刻之后,第二电介

质层410b的与间隔物412a相邻的剩余部分表示为410b’。

82.参考图4h,蚀刻第三电介质层410c(间隔物412a)、第一电介质层410a和硬掩模406’以暴露金属层405’上方的接触区。在一个实施例中,省略金属层405’,并且接触区是鳍403’的顶部。

83.参考图4i,蚀刻第二电介质层410b’(图4h所示)的剩余部分以暴露第一电介质层410a的剩余表面。

84.图4j至图4m是示出了根据本公开的第二实施例的制造垂直的基于鳍的fet器件的方法的中间阶段的剖视图。在第二实施例中,从图4d所示的结构开始,并且参考图4j,可以在第三半导体层407上执行平坦化工艺。在实施例中,平坦化工艺包括:通过蚀刻去除第三半导体层407的上部。在实施例中,平坦化工艺包括:去除约0.2μm的第三半导体层407的上部。其后,在第四半导体层407的平坦化表面上形成第一电介质层450,并且在第一电介质层450上形成第二电介质层452。在实施例中,第一电介质层450可以包括sio2并且通过pecvd在大约300℃下沉积。第二电介质层452可以包括si3n4并且通过pecvd在大约300℃下沉积。

85.参考图4k,回蚀第二电介质层452以在第一电介质层450的侧壁上形成具有约的厚度的间隔物454。在一个实施例中,第一电介质层450也被回蚀一定深度,使得第一电介质层450的上表面在硬掩模层406’的厚度内,如图4k所示。

86.参考图4l,进一步回蚀第一电介质层450,这暴露第四半导体层407的上表面。在实施例中,第一电介质层450可以被过度蚀刻50%的量以暴露硬掩模层406’的上表面和一部分侧壁。

87.参考图4m,去除硬掩模层406’和间隔物454,同时保留第一电介质层450的剩余部分。为了清楚起见,金属层405’已经被去除,但是它可以用于形成到鳍403’的电接触并且被包括在器件结构中,如对于本领域技术人员将是明显的。

88.图4n到图4u是示出可以应用于第一和第二实施例的制造垂直的基于鳍的fet的方法的中间阶段的剖视图。为了例示的目的,图4n至图4u应用于第二实施例,并且本领域技术人员可以容易地将相同的中间阶段应用于第一实施例。参考图4n,源极掩模层415形成为覆盖第四半导体层407的暴露的上表面,并具有暴露第一电介质层450的一部分和鳍403’的上表面的开口415a。源极掩模层415还具有在开口415a上延伸的悬突415b。在实施例中,源极掩模层415是能够剥离的,并且具有0.65μm的底部cd和0.55μm的顶部cd。

89.参考图4o,通过在约150℃的温度下在鳍403’的暴露上表面上沉积来形成源极金属接触结构416。在实施例中,源极金属接触结构416可以包括堆叠结构,该堆叠结构包括在鳍403’的上表面上的第一源极金属层416a、在第一源极金属层416a上的第二源极金属层416b和在第二源极金属层416b上的第三源极金属层416c。如果存在金属层405’,则第一源极金属层416a在第一金属层405’上。在实施例中,第一源极金属层416a包括厚度约25nm的ti,第二源极金属层416b包括厚度约100nm的al,第三源极金属层416c包括厚度约40nm的mo。在另一实施例中,第二源极金属层416b包括tin,第三源极金属层416c包括al。在另一实施例中,第二源极金属层416b包括tin,省略第三源极金属层416c。在形成源极金属接触结构之后,溶解源极掩模层415以剥离沉积在其上的金属层,而沉积在鳍的上表面上的金属层保持完整。在另一实施例中,在沉积源极金属接触结构416之后以反色调施加源极掩模层415,并且除了存在反色调掩模层415的地方之外,(例如,使用rie)蚀刻源极金属接触结构

416。然后去除源极掩模层415。在开口415a下方形成的源极金属接触结构416将具有与开口的宽度对应的大约0.65μm的宽度。在实施例中,可以在n2中在850℃下执行快速温度退火(rta)处理5分钟。在rta处理之后,源极金属接触结构将具有小于约10

‑5欧姆

‑

厘米的比电阻。

90.在一些实施例中,通过注入(例如,注入氮(n)或氩(ar))在fet器件有源区外部形成结终端边缘(jte)结构,以使得器件能够稳定地高压操作。

91.参考图4p,形成栅极金属掩模层420,该栅极金属掩模层覆盖源极金属结构的暴露的上表面,并且具有暴露第四半导体层407的表面部分的开口420a。栅极金属掩模层420还具有在开口420a上方延伸的悬突(overhang)420b。在实施例中,栅极金属掩模层420是能够剥离的,并且具有0.9μm的底部cd和0.8μm的顶部cd。

92.参考图4q,通过开口420a在第四半导体层407的暴露表面部分上沉积形成栅极金属接触结构421。在实施例中,栅极金属接触结构421可以包括堆叠结构,该堆叠结构包括在第四半导体层407的表面部分上的第一栅极金属层421a、在第一栅极金属层421a上的第二栅极金属层421b、在第二栅极金属层421b上的第三栅极金属层421c、以及在第三栅极金属层421c上的第四栅极金属层421d。在实施例中,第一栅极金属层421a包括ni,第二栅极金属层421b包括au,第三栅极金属层421c包括mo,并且第四栅极金属层421d包括au。在另一实施例中,省略了栅极金属层421c和421d,并且第一栅极金属层421a包括ni且第二栅极金属层421b包括au。在另一实施例中,省略了栅极金属层421d,并且第一栅极金属层421a包括pd,第二栅极金属层421b包括pt,且第三栅极金属层421c包括au。在形成栅极金属接触结构之后,溶解栅极金属掩模层420以剥离沉积在栅极掩模层上的金属层,而沉积在第四半导体层407的表面部分上的金属层保持完整。

93.参考图4r,去除栅极金属掩模层420,并且执行热退火以提供稳定的低接触电阻接触。在实施例中,可以在o2中在500℃下执行快速热退火(rta)处理10分钟。在热处理之后,栅极金属接触结构421将具有小于约10

‑3欧姆

‑

厘米的比电阻。

94.参考图4s,在300℃的温度下使用等离子体增强化学气相沉积(pecvd)工艺沉积第一层间电介质层425,该第一层间电介质层425覆盖栅极金属接触结构421、源极金属接触结构416和第四半导体层407的表面。第一层间电介质层425是相对共形的。在实施例中,第一层间电介质层425具有大约50nm的厚度并且可以包括氮化物(例如,氮化硅)。接着,在300℃的温度下使用等离子体增强化学气相沉积(pecvd)工艺在第一层间电介质层425上沉积第二层间电介质层426(方框336)。第二层间电介质层426具有约50nm的厚度,并且可以包括氧化物(例如,氧化硅)。

95.参考图4t,在可以被平坦化或未平坦化的第二层间电介质层426上形成图案化的光刻胶层427。形成图案化的光刻胶层427,并用公知的光刻工艺对其进行图案化,以限定将要形成过孔428的位置。接着,蚀刻第一和第二层间电介质层425、426,直到暴露源极金属接触结构416的上表面。在一些实施例中,到栅极金属接触结构421的过孔也可以与用于源极金属接触结构的过孔428同时形成。在实施例中,过孔具有大约0.45μm的cd。

96.接着,去除图案化光刻胶层427。参考图4u,形成导电材料429,该导电材料填充过孔428,并且通过蒸发在填充的过孔上执行焊盘金属沉积到大约4μm的厚度。上述制造垂直的基于鳍的fet的方法的优点在于,在鳍外延层上形成金属、金属合金或金属化合物层(例

如tin),随后形成硬掩模层。

97.图5是使用0.2μm鳍宽度的模拟单元结构的剖视图。标称蚀刻深度是在鳍层的底部下方0.1μm(进入渐变区0.1μm)。模拟了标称周围+/

‑

0.1μm的蚀刻深度变化、以及对于第二轮模拟的0.2μm的渐变区厚度和对于第三轮模拟的0.3μm的渐变区厚度。

98.图6是例示了对于0.3μm鳍和未渐变外延层的作为蚀刻偏移(以μm为单位)的函数的垂直的基于鳍的fet器件的阈值电压(以v为单位)的曲线图。x轴上的“0”表示鳍与漂移区之间的界面。蚀刻偏移的正值指示过度蚀刻到鳍层下方的漂移区中,而蚀刻偏移的负值指示蚀刻不足。y轴表示电压阈值(v)。参考图6,过度蚀刻到鳍层下方的漂移区中导致电压阈值的显著增加。因此,发明人已经发现关于电导和阈值电压的到漂移区中的过度蚀刻的可接受极限是大约0.1μm。

99.图7是例示了对于0.3μm鳍和未渐变外延层的作为蚀刻偏移(以μm为单位)的函数的垂直的基于鳍的fet器件的电场e(以mv/cm为单位)的曲线图。x轴上的“0”表示鳍与漂移区之间的界面。蚀刻偏移的正值指示过度蚀刻到鳍层下方的漂移区中,而蚀刻偏移的负值指示蚀刻不足。y轴表示电场e(mv/cm)。外延层的蚀刻不足(即,在与漂移层的界面上方)导致最大电场的显著增加。即,击穿风险随着0.1μm或更大的蚀刻不足而增加。

100.图8是例示了对于0.3μm鳍和未渐变外延层的作为蚀刻偏移(以μm为单位)的函数的垂直的基于鳍的fet器件的沟道泄漏(以a为单位)的曲线图。x轴中的“0”表示鳍与漂移区之间的界面。蚀刻偏移的正值指示过度蚀刻到鳍层下方的漂移区中,而蚀刻偏移的负值指示蚀刻不足。y轴表示漏源泄漏电流idss(a)。参考图8,不存在蚀刻变化对泄漏电流的显著影响。

101.图9a是例示了正常蚀刻的电流密度的曲线图。图9b是例示了0.1μm过度蚀刻的电流密度的曲线图。图9c是例示了0.2μm过度蚀刻的电流密度的曲线图。因此,这些曲线图例示了关于0.3μm鳍和未渐变外延层的若干蚀刻条件下的作为相对于鳍的位置的函数的电流密度(a/cm2)。鳍位于各个曲线图的右侧。水平实线910是标称蚀刻深度,虚线901示出了鳍/漂移区界面。x轴表示以微米为单位的电流密度相对于鳍的位置,其中,“1”对应于鳍的中间。y轴表示蚀刻的漂移区相对于栅极层的位置,其中,“0”对应于栅极层的上表面,并且“0.8”对应于栅极层的标称底部位置。

102.参考图9a,对于终止于栅极层的底部的标称蚀刻,即蚀刻深度为0.8μm且终止于与漂移区的界面处,高电流密度在栅极层的底部与鳍的底部之间的界面周围,且阈值电压在标称范围内。在例示了0.1μm过度蚀刻的电流密度的图9b中,与栅极层底部的界面位于0.9μm处。阈值电压较高,如由条带902指示的。在例示了0.2μm过度蚀刻的电流密度的图9c中,阈值电压更差,如条带903指示的。结果也在图6中得到证实,图6示出了在0.2μm过度蚀刻时的阈值电压的显著增加。

103.图10a是例示了对于正常蚀刻在栅极拐角处的电场的曲线图。图10b是例示了对于0.1μm蚀刻不足在栅极拐角处的电场的曲线图。图10c是例示了0.2μm蚀刻不足的电流密度的曲线图。如图例示,这些曲线图示出了对于不同蚀刻条件在栅极拐角处的电场。标称蚀刻条件由标记为“n/n界面”的水平线1010指示。图10a是例示了对于正常蚀刻在栅极拐角处具有标称值的电场1001的曲线图。双箭头1002示出了在与栅极层的界面下方的重掺杂区域。图10b是例示了对于0.1μm蚀刻不足在栅极拐角处的电场1003的曲线图。双箭头1004示出了

布置在栅极层与蚀刻不足区域之间的重掺杂区域的一部分,该蚀刻不足区域可能在栅极拐角处引起高电场。图10c是例示了用于0.2μm蚀刻不足的电场的曲线图。高场区(由图10b中的椭圆1007和图10c中的椭圆1008指示)靠近具有鳍的栅极拐角。由双箭头1006指示的重掺杂区完全布置在蚀刻不足区中。

104.具有0.2μm渐变外延层的0.2μm鳍

105.图11是例示了对于0.2μm渐变外延层的作为蚀刻变化(μm)的函数的漏源导通电阻ron(mω)的曲线图。“0”对应于鳍与漂移区之间的0.2μm渐变外延层的中间。ron随着0.1μm过度蚀刻而显著增加。参考图11,在约0.05μm过度蚀刻时达到ron上限“usl”(规格上限)。即,当蚀刻变化在

±

0.1μm之间的范围内时,导通电阻值将在规格上限之外。

106.图12是例示了对于0.2μm渐变外延层的作为蚀刻变化(μm)的函数的阈值电压vt(v)的曲线图。“0”对应于鳍与漂移区之间的0.2μm渐变外延层的中间。与导通电阻相似,阈值电压vt随着0.1μm过度蚀刻而显著增加。即,当过度蚀刻渐变掺杂区时,阈值可能增加到不可接受的值。参考图11和图12,蚀刻不足确实提供了导通电阻和阈值电压的改进。如下面的图13和图14所示,蚀刻不足还提供了最大电场和漏电流的改进。

107.图13是例示了对于0.2μm渐变外延层的作为蚀刻变化(μm)的函数的最大电场(mv/cm)的曲线图。通过允许标称蚀刻在渐变掺杂层中结束,0.2μm渐变外延层确实提供了具有蚀刻不足的电场的改善。0.1μm蚀刻不足情况现在类似于第一轮模拟中的标称情况,其中由于渐变掺杂层中的附加电荷而导致电场略微增大。

108.图14是例示了对于0.2μm渐变外延层的作为蚀刻变化(μm)的函数的1200v下的高电压漏极泄漏电流idss(a)的曲线图。参考图14,高压漏极泄漏电流idss保持由渐变外延层很好地控制。即,过度蚀刻或蚀刻不足不影响泄漏电流。

109.具有0.3μm渐变外延层的0.2μm鳍

110.发明人使用0.2μm的鳍进行了第三轮模拟,其中0.3μm厚的线性渐变外延层插入在鳍外延层与漂移区之间。在第三轮模拟中,标称蚀刻深度保持在鳍外延层的底部下方0.1μm处,且结果示出在图16到图19中。

111.图15是例示了对于0.3μm渐变外延层的作为蚀刻变化(μm)的函数的漏源导通电阻ron(mω)的曲线图。参考图15,对于

‑

0.1μm到零范围内的蚀刻不足,导通电阻ron被很好地控制。参考图15,对于0.1μm过度蚀刻条件,导通电阻ron增加约10%,这是可接受的,并且远小于在第二组模拟中使用的0.2μm渐变外延层(参见图11)中观察到的导通电阻。

112.图16是例示了对于0.3μm渐变外延层的作为蚀刻变化(μm)的函数的阈值电压vt(v)的曲线图。参考图16,对于

‑

0.1μm到零范围内的蚀刻不足,阈值电压vt被很好地控制。随着0.1μm的过度蚀刻,阈值电压vt增加了大约10%,这是可接受的,并且远小于图12中对于使用在第二组模拟中使用的0.2μm渐变外延层的结构例示的阈值电压vt。

113.图17是例示了对于0.3μm渐变外延层的作为蚀刻变化(μm)的函数的电场(mv/cm)的曲线图。参考图17,0.3μm渐变区的电场高于图13所例示的0.2μm渐变区的电场。在0.1μm蚀刻不足条件下,电场约为3.15mv/cm(在边界线处),即,最大电场在最小蚀刻深度处是边缘的。通过另外的优化,通过改变标称蚀刻深度的渐变或重新居中,将改善边界线或边缘条件。

114.图18是例示了对于0.3μm渐变外延层的作为蚀刻变化(μm)的函数的1,200v下的高

电压漏极泄漏电流idss(a)的曲线图。参考图18,在模拟蚀刻范围内很好地控制了高压漏极泄漏电流idss。

115.总之,发明人已经确定,使用突变的鳍外延层到漂移区掺杂过渡,预期的鳍蚀刻深度工艺变化将导致漏源导通电阻ron、阈值电压vt和击穿电压的不可接受的变化。在鳍外延区与漂移区之间插入渐变掺杂区作为过渡层显著地改善了随蚀刻工艺变化的参数变化。线性渐变的0.3μm过渡区实现了对漏源导通电阻ron和vt变化的良好控制。电场较高,并且通过本发明的实施例优化了渐变(或蚀刻深度),以将电场水平降低到大约3mv/cm。

116.在一个实施例中,用于fet器件的现有silvaco tcad模型被修改为在栅极区中使用in

0.15

ga

0.85

n材料。使用材料模型和应变计算来计算in

0.15

ga

0.85

n/gan界面处的预期极化电荷。

117.表1示出了所计算的in

0.15

ga

0.85

n/gan界面的电荷分量。

118.表1

[0119][0120]

假设该极化电荷发生在c平面上,而不是在沟道侧壁(m平面)上,遵循这些平面上的iii

‑

n族异质结面的典型行为。

[0121]

图19a是例示了没有极化电荷对预测在c平面in

0.15

ga

0.85

n/gan界面处产生的电流密度的影响的曲线图。该曲线图示出了在不包括极化的情况下的总电流密度的2d横截面。参考图19a,电流1901从鳍(即,沟道)与栅极区之间的沟道区流向漂移区,而没有通过in

0.15

ga

0.85

n栅极区与gan漂移区之间的界面充分地水平扩散。图19b是例示了根据本公开的一些实施例的预测在c平面in

0.15

ga

0.85

n/gan界面处产生的极化电荷的效应的曲线图。该曲线图示出了在包括极化的情况下的总电流密度的2d横截面。预期由于极化而在界面处的净固定正电荷吸引相等且相反的移动电荷(2d电子气)。在该位置处的2deg导致在沟道开口处更大的电流扩散到漂移层。参考图19b,电流1903经由二维电子气(2deg)沿着栅极层的底部的侧面水平流动,然后通过漂移区在朝向衬底和漏极金属接触的方向上垂直流动,二维电子气由in

0.15

ga

0.85

n/gan界面在c平面中的极化而引起。这可以提供比不包括极化的现有器件更小的器件尺寸和更低的成本的显著优点。

[0122]

图20a是例示了预测在c平面in

0.15

ga

0.85

n栅极层与gan漂移层之间的界面处产生的电场的效应的曲线图。在截止状态下,在栅极层(区)与漂移层(区)之间均匀地形成相对低的电场。图20b是例示了根据本公开的一些实施例的预测在c平面in

0.15

ga

0.85

n/gan界面处产生的电场的效应的曲线图。该曲线图示出了由于在截止状态下的极化而形成的相对高的电场。

[0123]

图20c是例示了没有极化2111和有极化2112的电场的截止状态幅度的曲线图。参考图20c,垂直剖切线2113被例示为穿过非沟道(p

‑

n结区)。由于极化而存在2deg导致在截

止状态下在界面处产生高电场。

[0124]

表2例示了基线gan finfet相对于包括极化的in

0.15

ga

0.85

n栅极finfet的模拟电参数。

[0125]

表2

[0126] 基线finfet具有极化的ingan finfetichannel0.80.8nchannel1.30e+171.30e+17渐变着陆是是鳍宽度(μm)0.20.2vth(v)1.231.15idss@1200v(a)8.70e

‑

127.10e

‑

12最大e(mv/cm)2.924.5最大e||(mv/cm)2.42.4电导/单位沟槽(s/cm)6.55e

‑

086.60e

‑

0.8

[0127]

如图19a、图19b、图20a至图20c以及上表2所示,使用15%的ingan示出能够提供预期的益处(较低的阈值电压:vth 1.15v对1.23v),但是在截止状态下具有增加的电场的严重折衷(4.5mv/cm对2.92mv/cm)。它建议使用较低百分比的in,这导致较低的极化电荷,甚至可忽略的极化。本发明人将在下面示出非极化ingan finfet结构的模拟结果。

[0128]

表3例示了基线gan finfet相对于非极化ingan栅极finfet的模拟电参数。

[0129]

表3

[0130][0131][0132]

参考表3,使用ingan导致在低电场(2.6mv/cm对2.92mv/cm)情况下的

‑

0.08v的阈值电压偏移(1.15v对1.23v)。沟道掺杂可以被重新调整以返回到基线阈值电压,这导致结构之间的非常小的电气差异。ingan的优点将是更低温度生长和更好的欧姆接触和p型掺杂。

[0133]

图21a是例示了通过基线fet的沟道的电流密度的曲线图。图21b是例示了通过非极化fet的沟道的电流密度的曲线图,其中p型ingan栅极沿着非极化平面与ingan沟道界面连接。图21c是在150摄氏度下与通过非极化fet的沟道的电流密度(曲线2412)相比较的通过基线fet的沟道的电流密度(曲线2411)的曲线图。在图21c中,电流密度对应于定位在沟道中的剖切线2110(图21a中示出)。图21d是与非极化fet的能带图比较的基线fet的能带图的曲线图。在图21d中,在对应于剖切线2115(图21b所示)的栅极(非沟道区)下示出了基线fet(曲线2413)和非极化fet(曲线2414)的能带图。接合处2420也在图21d中例示。

[0134]

根据本发明的实施例,提供了具有利用ingan(例如,代替gan)的p型栅极区的finfet。将ingan用于p型栅极材料提供了使用常规技术不能获得的许多益处。例如,本文描述的一些工艺流程利用ingan比gan低的生长温度,gan用于保护在再生长工艺期间利用的再生长硬掩模。而且,一些实施例利用镁掺杂,其中,mg掺杂剂在ingan层中较浅,这导致在相同温度下的掺杂剂的较高离子化。另外,ingan的较低带隙有助于形成与p型区的欧姆接触。

[0135]

本发明的实施例考虑极化效应来实现电流扩展与高电场之间的期望折衷,这已得到证明。

[0136]

下面提供另外的实施例,以进一步例示根据本发明实施例的制造垂直的基于鳍的fet器件的方法。以下实施例中的一些集中于制造用于垂直的基于鳍的fet器件的自对齐源极接触。

[0137]

本发明的另外的实施例可以在参考图4c例示的方法300的步骤320之后提供中间步骤。为了清楚起见,图4c所示的中间阶段通常在图22a中再现。参考图22a,垂直的基于鳍的fet器件2200包括半导体衬底2202,例如n+掺杂的半导体衬底。在实施例中,半导体衬底2202可以包括iii族氮化物化合物,例如n型gan。在950℃至1200℃之间、优选在1000℃至1150℃之间、更优选约1100℃的温度下,在半导体衬底2202上外延生长第一半导体层2204。在实施例中,第一半导体层2204可以包括iii族氮化物材料,例如n型gan。与参考图4a至图4c例示的实施例类似,使用图案化的硬掩模层2210作为掩模来执行蚀刻工艺,以在第一半导体层2204上形成多个半导体鳍2206。多个半导体鳍2206中的每一个被多个凹进区2205中的一个分开。在实施例中,多个半导体鳍2206可以包括iii族氮化物化合物,例如n型gan。

[0138]

在一些实施例中,半导体衬底2202可重掺杂有n型掺杂剂,这些掺杂剂的掺杂浓度在约5

×

10

17

原子/cm3至约1

×

10

19

原子/cm3的范围内,且电阻率小于0.020欧姆

‑

厘米。在一些实施例中,可实施为n+掺杂半导体衬底的半导体衬底2202的电阻率可为从约0.001欧姆

‑

厘米至0.018欧姆

‑

厘米,优选地小于0.016欧姆

‑

厘米,且更优选地小于0.012欧姆

‑

厘米。在一些实施例中,第一半导体层2204是具有约12μm厚度和约1

×

10

16

原子/cm3范围内的掺杂浓度的漂移层。多个半导体鳍2206的特征可以在于用约1.3

×

10

17

原子/cm3的n型掺杂剂进行的均匀掺杂和约12μm的厚度。在一些实施例中,例如图4c所示的渐变掺杂区460的渐变掺杂层(图22a中未示出)布置在第一半导体层2204与多个半导体鳍2206之间。在一些实施例中,多个半导体鳍2206中的每一个具有约0.2μm的宽度、在约0.7μm至0.8μm之间的范围内的高度,并且通过约2.0μm的凹进区2205彼此隔开,即,鳍间距为约2.0μm。为了提供特征在于均匀高度的鳍,本发明的实施例利用特征在于良好深度可控性的蚀刻工艺。在一些实施例中,多个半导体鳍2206中的每一个可以包括金属,例如图4c所示的金属层405。金属层布置在硬

掩模层2210与多个半导体鳍2206中的每一个的顶部之间。为了清楚起见,金属层未在图22a中示出。

[0139]

在一些实施例中,在形成多个凹进区2205之后,使用约25重量%的tmah溶液在约85℃的温度下进行清洁工艺,并且持续约5分钟的持续时间。其后,在实施例中,执行抛光蚀刻工艺。抛光蚀刻工艺可以包括使用rie的低功率基于cl的化学过程。在另一实施例中,在使用tmah溶液执行清洁之前,还可以执行预清洁,例如2分钟的使用h2so4:h2o以2:1的体积比的皮伦尼亚清洁。

[0140]

参考图22b,在完成清洁之后,在多个凹进区2205(图22a中示出)的每一个中外延再生长半导体栅极层2208。在一些实施例中,半导体栅极层2208可以包括p型gan材料,该p型gan材料在大约950℃的温度下在凹进区2205中非共形地生长到与硬掩模层2210的底部基本上相平的厚度。在一些实施例中,半导体栅极层2208的厚度为约840nm。p型gan层可以用约1

×

10

19

原子/cm3的掺杂浓度掺杂mg。其后,执行热退火(例如,在n2中在850℃下快速热退火5分钟)以激活mg掺杂原子。然后,在p型gan层中以大于1重量%的量激活mg原子。在一些实施例中,在多个半导体鳍2206与硬掩模层2210之间可以存在重n+掺杂层(在图22b中未示出),例如图4b中示出的层404。

[0141]

在一些实施例中,可以对半导体栅极层2208执行平坦化工艺。在一些实施例中,平坦化工艺包括:通过蚀刻去除半导体栅极层2208的上部,例如去除0.2μm的半导体栅极层2208的上部。

[0142]

参考图22c,在半导体栅极层2208和硬掩模层2210上形成第一电介质层2212。在一些实施例中,第一电介质层2212与硬掩模层2210的侧壁基本上共形。在实施例中,第一电介质层2212具有大约200nm的厚度,并且可以包括sio2,并且通过pecvd在大约300℃下沉积。第一电介质层2212的一部分可以指定为与多个半导体鳍2206中的每一个基本对齐的接触区2214和与鳍之间的半导体栅极层2208基本对齐的栅极区2216。

[0143]

其后,在第一电介质层2212的栅极区2216上形成图案化的光刻胶层2218。在一些实施例中,光刻胶层2218的上表面与第一电介质层2212的接触区2214的上表面相平。在一些实施例中,形成图案化的光刻胶层2218,并利用公知的光刻工艺对光刻胶层进行图案化,以暴露硬掩模层2210的接触区2214。接着,参考图22d,使用光刻胶层2218为掩模来蚀刻第一电介质层2212的接触区2214,以暴露出硬掩模层2210的上表面。在一些实施例中,接触区2214被过度蚀刻以延伸到第一电介质层2212中的预定深度,使得第一电介质层2212的接触区2214的上表面布置在硬掩模层2210的厚度内。在实施例中,预定深度为约0.25μm。其后,如图22e所示,蚀刻硬掩模层2210以暴露多个半导体鳍2206中的每一个的上表面2220。

[0144]

参考图22e,去除光刻胶层2218(图22d中示出)以暴露第一电介质层2212的上表面以及半导体鳍2206的上表面2220。参考图22f,在多个半导体鳍2206中的每一个的上表面2220上再生长半导体源极接触部分2222并将该部分耦合到多个半导体鳍2206中的每一个。在一些实施例中,半导体源极接触部分2222包括n型gan,该n型gan的掺杂浓度为约2

×

10

17

至5

×

10

17

原子/cm3。当半导体源极接触部分2222的特征在于三角形时,半导体源极接触部分2222的再生长是自限制的。作为示例,在自限制生长工艺中,半导体源极接触部分2222的特征可以在于等腰三角形形状,该形状在如图22f例示的剖视图中具有58度至65度之间的范围内的底角。

[0145]

在实施例中,半导体源极接触部分2222具有约0.1μm至0.2μm的高度。在实施例中,在800℃至1150℃之间的范围内的生长温度下且在约600毫巴的压力下,利用h2载气,可获得用于再生长刻面的平滑表面。在实施例中,再生长温度在850℃至1100℃的范围内,优选在900℃至1050℃之间的范围内,更优选在约930℃至970℃之间的范围内,例如在实施例中为950℃。

[0146]

其后,在第一电介质层2212和半导体源极接触部分2222上形成源极接触结构。在一些实施例中,源极接触结构包含多个(二到四个)金属或金属合金层。在实施例中,源极接触结构可以包括第一源极金属层、第二源极金属层和第三源极金属层。参考图22g,第一源极金属层2224形成为覆盖半导体源极接触部分2222和第一电介质层2212。在实施例中,第一源极金属层2224可以包括具有约25nm的厚度的钛。接着,在第一源极金属层2224上形成第二源极金属层2226并将第二源极金属层耦合至第一源极金属层2224。在实施例中,第二源极金属层2226可以包括具有100nm厚度的铝。其后,在第二源极金属层2226上形成第三源极金属层2228并将第三源极金属层耦合至第二源极金属层2226。在实施例中,第三源极金属层2228可包括具有约40nm厚度的钼。在另一实施例中,第二源极金属层2226可以包括氮化钛,第三源极金属层2228可以包括铝。在一些实施例中,省略了第三源极金属层2228。

[0147]

参考图22h,在第三源极金属层2228上形成源极金属掩模层2230。源极金属掩模层2230具有与栅极区2216对齐的开口2232。在实施例中,源极金属掩模层2230是能够剥离的,并且具有约0.6μm的底部cd。其后,参考图22i,使用源极金属掩模层2230作为掩模蚀刻第三源极金属层2228、第二源极金属层2226和第一源极金属层2224以暴露第一电介质层2212的上表面。在实施例中,蚀刻工艺可以包括使用rie的基于cl的化学过程。然后,使用源极金属掩模层2230作为掩模蚀刻掉第一电介质层2212,以暴露半导体栅极层2208的上表面。在实施例中,蚀刻第一电介质层2212可以包括使用rie的基于f的化学过程。

[0148]

参考图22j,去除源极金属掩模层2230(图22h中示出)。在实施例中,在去除源极金属掩模层2230之后,执行热退火工艺以提供稳定的低接触电阻接触。在实施例中,可以在n2中在825℃下进行快速热退火(rta)处理90秒。在rta处理之后,源极金属结构将优选地具有小于约10

‑5欧姆

‑

厘米的比电阻。

[0149]

参考图23a至图23g,例示了根据本发明的制造用于垂直的基于鳍的fet器件的自对齐源极接触的另一实施例。如下面更充分地描述的,可以执行与参考图22a至图22c例示的工艺类似的工艺来实现如图23a所示的工艺阶段。具体地,垂直的基于鳍的fet器件2300包括可以是n+掺杂半导体衬底的半导体衬底2302、在半导体衬底2302上外延生长的第一半导体层2304、以及在第一半导体层2304上形成的多个半导体鳍2306。多个半导体鳍2306中的每一个被多个凹进区中的一个分开。在多个凹进区中外延形成半导体栅极层2308。

[0150]

与图22a所示的实施例相似,硬掩模层2310存在于多个半导体鳍2306中的每一个的顶部上。在半导体栅极层2308和硬掩模层2310上形成第一电介质层2312。在实施例中,第一电介质层2312与硬掩模层2310的侧壁基本上共形。第一电介质层2312的一部分可以指定为与多个半导体鳍2306中的每一个基本对齐的接触区2314和与鳍之间的半导体栅极层2308基本对齐的栅极区2316。其后,在第一电介质层2312的栅极区2316上形成图案化的光刻胶层2318。在实施例中,在栅极区2316的一部分上形成光刻胶层2318,使接触区2314具有各个半导体鳍2306的宽度的至少三倍的宽度。例如,当多个半导体鳍2306中的每一个的宽

度是0.2μm时,接触区2314具有0.6μm的宽度。

[0151]

参考图23b,使用光刻胶层2318作为掩模蚀刻第一电介质层2312,以去除第一电介质层2312和硬掩模层2310的部分,并形成多个凹进区2320。多个半导体鳍2306中的每一个的上表面2324和半导体栅极层2308的上表面的围绕多个半导体鳍2306中的每一个的部分2322在多个凹进区2320中的每一个的底部处暴露。

[0152]

参考图23c,去除光刻胶层2318(图23b中示出)。参考图23d,在多个凹进区2320的每一个中外延再生长半导体源极接触部分2326,并且将该部分耦合到多个半导体鳍2306中的每一个。在实施例中,半导体源极接触部分2326包括iii族氮化物材料,例如具有大约2

×

10

17

至5

×

10

17

原子/cm3的掺杂浓度的n型gan。当源极接触部分2326的特征在于等腰梯形形状时,半导体源极接触部分2326的再生长是自限制的。在实施例中,半导体源极接触部分2326具有约0.1μm至0.2μm的高度。在实施例中,在800℃至1150℃之间的范围内的生长温度下且在约600毫巴的压力下,利用h2载气,可获得用于再生长刻面的平滑表面。在实施例中,再生长温度在850℃至1100℃的范围内,优选在900℃至1050℃之间的范围内,更优选在约930℃至970℃之间的范围内,例如在实施例中为950℃。

[0153]

参考图23e,在再生长半导体源极接触部分2326之后,去除第一电介质层2312(图23d中示出),以暴露半导体栅极层2308的上表面。在实施例中,执行湿法蚀刻工艺来去除第一电介质层2312。参考图23f,将源极金属掩模层2328形成为覆盖半导体栅极层2308的暴露的上表面,该源极金属掩模层具有暴露半导体源极接触部分2326的上表面的开口2338。在实施例中,源极金属掩模层2328是能够剥离的,并且具有0.6μm的底部cd和0.5μm的顶部cd。

[0154]

其后,在约25℃至150℃的温度下,在半导体源极接触部分2326的暴露的上表面上形成源极接触结构。在一些实施例中,源极接触结构包含多个(二到四个)金属或金属合金层。在实施例中,源极接触结构可以包括第一源极金属层2332、第二源极金属层2334和第三源极金属层2336。具体地,第一源极金属层2332形成为覆盖半导体源极接触部分2326和源极金属掩模层2328。在实施例中,第一源极金属层2332可以包括具有约25nm的厚度的钛。接着,在第一源极金属层2332上形成第二源极金属层2334并将第二源极金属层耦合至第一源极金属层2332。在实施例中,第二源极金属层2334可以包括具有100nm厚度的铝。其后,在第二源极金属层2334上形成第三源极金属层2336并将第三源极金属层耦合至第二源极金属层2334。在实施例中,第三源极金属层2336可包括具有约40nm厚度的钼。在另一实施例中,第二源极金属层2334可以包括铝,并且第三源极金属层2336可以包括氮化钛。在一些实施例中,省略了第三源极金属层2336。

[0155]

参考图23g,溶解源极金属掩模层2328(图23f中示出),以剥离沉积在其上的金属层2332、2334和2336,而沉积在半导体源极接触部分2326的上表面上的金属层2332、2334和2336保持完整。在实施例中,源极金属结构具有0.6μm的宽度。在实施例中,可以在n2中在825℃下进行快速温度退火(rta)处理90秒。在rta处理之后,源极金属结构将优选地具有小于约10

‑5欧姆

‑

厘米的比电阻。

[0156]

参考图24a至图24e,例示了制造用于垂直的基于鳍的fet器件的自对齐源极接触的另一实施例。如下面更充分地描述的,可以执行与参考图22a至图22b例示的工艺类似的工艺来实现如图24a所示的工艺阶段。具体地,垂直的基于鳍的fet器件2400包括例如是n+掺杂半导体衬底的半导体衬底2402、在半导体衬底2402上外延生长的第一半导体层2404、

以及在第一半导体层2404上形成的多个半导体鳍2406。多个半导体鳍2406中的每一个被多个凹进区中的一个分开。在多个凹进区中外延形成半导体栅极层2408。与图22a所示的实施例相似,硬掩模层2410存在于多个半导体鳍2406中的每一个的顶部上。

[0157]

其后,参考图24b,去除硬掩模层2410以暴露多个半导体鳍2406的上表面。在实施例中,在半导体栅极层2408的上部的至少一部分中外延再生长未掺杂的半导体盖层2409。在实施例中,在鳍之间的半导体栅极层2408的上部中的基本上中心部分处外延生长未掺杂的半导体盖层2409。

[0158]

参考图24c,将第二半导体层2414外延生长为覆盖多个半导体鳍2406和半导体栅极层2408。在实施例中,第二半导体层2414包括iii族氮化物材料,例如具有第一掺杂浓度的n型gan。接着,在第二半导体层2414上外延生长第三半导体层2415。在实施例中,第三半导体层2415包括iii族氮化物化合物,例如具有大于第二半导体层2414的第一掺杂浓度的第二掺杂浓度的n型gan。为了描述的清楚,与多个半导体鳍2406中的每一个对齐的区域被指定为接触区2413,并且与半导体栅极层2408对齐的区域被指定为栅极区2417。接触区2413的宽度可以根据垂直的基于鳍的fet器件2400的要求来确定。在实施例中,栅极区2417的宽度至少覆盖未掺杂的半导体盖层2409的宽度。

[0159]

参考图24d,形成源极金属结构。在一些实施例中,源极金属结构包含多个(二到四个)金属或金属合金层。具体地,在第三半导体层2415上形成第一源极金属层2416。在实施例中,第一源极金属层2416可以包括具有约25nm的厚度的钛。接着,在第一源极金属层2416上形成第二源极金属层2418并将第二源极金属层耦合至第一源极金属层2416。在实施例中,第二源极金属层2418可以包括具有100nm厚度的铝。其后,在第二源极金属层2418上形成第三源极金属层2420并将第三源极金属层耦合至第二源极金属层2418。在实施例中,第三源极金属层2420可包括具有约40nm厚度的钼。在另一实施例中,第二源极金属层2418可以包括氮化钛,第三源极金属层2420可以包括铝。在一些实施例中,省略了第三源极金属层2420。

[0160]

参考图24e,在第三源极金属层2420上形成源极金属掩模层2422。源极金属掩模层2422具有与栅极区2417基本上对齐的开口2424。其后,参考图24f,使用源极金属掩模层2422作为掩模蚀刻源极金属层2420、2418和2416以暴露第三半导体层2415的上表面。在实施例中,蚀刻工艺可以包括使用rie的基于cl的化学过程。接着,使用源极金属掩模层2422作为掩模蚀刻第三和第二半导体层2415和2414以暴露半导体栅极层2408的上表面。在实施例中,蚀刻工艺可以包括使用rie的cl基的化学过程。其后,使用源极金属掩模层2422作为掩模执行定时蚀刻工艺,以延伸到半导体栅极层2408中的预定深度。在实施例中,执行定时蚀刻工艺以消除未掺杂的半导体盖层2409(图24b中示出)。

[0161]

参考图24g,去除源极金属掩模层2422(图24f中示出)。在实施例中,在去除源极金属掩模层2422之后,执行热退火工艺以提供稳定的低接触电阻接触。在实施例中,可以在n2中在825℃下进行快速热退火(rta)处理90秒。在rta处理之后,源极金属结构将具有小于约10

‑5欧姆

‑

厘米的比电阻。

[0162]

应当理解,当例如层、区域或衬底的元件被称为在另一元件“上”或延伸到另一元件“上”时,该元件可以直接在另一元件上或直接延伸到另一元件上,或者也可以存在介入元件。相反,当元件被称为“直接在另一元件上”或“直接延伸到另一元件上”时,不存在介入

元件。还应当理解,当元件被称为“连接”或“耦合”到另一元件时,该元件可以直接连接或耦合到另一元件,或者介入元件也可以存在。相反,当元件被称为“直接连接”或“直接耦合”到另一元件时,不存在介入元件。

[0163]

相对性术语,例如“下方”或“上方”或“上”或“下”或“水平”或“横向”或“垂直”在本文中可用于描述一个元件、层或区域与另一元件、层或区域的关系,如图例示。应当理解,这些术语旨在除了包含附图中描绘的取向之外还包含器件的不同取向。

[0164]

本文所用的术语仅是为了描述特定实施例的目的且不旨在限制本发明。如本文所用的,单数形式“一”和“一个”旨在也包括复数形式,除非上下文另外清楚指示。还将理解,术语“包括”在本文使用时指定所述特征、整数、步骤、操作、元件和/或部件,但不排除一个或更多个其他特征、整数、步骤、操作、元件、部件和/或其组的存在或增加。

[0165]

本公开的实施例在本文中参考是本发明的理想化实施例(和中间结构)的示意图的剖视图来描述。为了清楚起见,附图中的层和区域的厚度可以相对于其它层和区域放大。另外,预期来自作为例如制造技术和/或公差的结果的、例示的形状的变化。由此,本发明的实施例不应被解释为限于本文所例示的区域的特定形状,而是包括例如因制造而产生的形状的偏差。例如,例示为矩形的注入区在其边缘处通常将具有圆形或弯曲的特征和/或注入浓度梯度,而不是从注入区到非注入区的离散变化。同样地,通过注入形成的掩埋区可以导致在掩埋区与发生注入所通过的表面之间的区域中的一些注入。由此,图中例示的区域本质上是示意性的,并且它们的形状不旨在例示器件的区域的实际形状,并且不旨在限制本发明的范围。

[0166]

相关领域的普通技术人员已知的技术、方法和器件可能未作详细讨论,但是在应用这些技术、方法和设备的情况下,这些技术、方法和设备应当被认为是本说明书的一部分。进一步地,在附图中,类似的附图标记用于指代类似的项目,并且一旦在一个附图中定义了项目,则将不需要在随后的附图中进一步说明。

[0167]

本文公开的实施例不受本文描述的具体实施例的范围限制。除了本文所述的实施例之外,根据前面的描述和附图,本发明的实施例的各种修改对于本领域的普通技术人员将是显而易见的。进一步地,尽管已经在用于特定目的特定环境中的特定实现的背景下描述了本发明的一些实施例,但是本领域的普通技术人员将认识到,其有用性不限于此,并且本发明的实施例可以出于任何数量的目的而在任何数量的环境中有益地实现。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1