一种功率半导体封装结构的制作方法

1.本技术涉及半导体的技术领域,尤其涉及一种功率半导体封装结构。

背景技术:

2.半导体是一种导电能力介于导体与非导体之间的材料,半导体元件根据半导体材料的特性,属于固态元件,其体积可以缩小到很小的尺寸,因此耗电量少,集成度高,在电子技术领域获得了广泛的应用,而随着半导体元件运行功率的逐渐增加,散热性能成为半导体元件的重要指标之一,在这样的高热量工作环境下,保持半导体元件的工作可靠性是一个非常重要的问题。

3.传统的半导体封装结构中,芯片都是通过焊接或胶接于引线框架上方,芯片产生的热需要通过焊接或胶接材料传递至引线框架,再由引线框架传递至外界,热传导路径较长,热阻较大,导致半导体存在散热慢的技术问题。

技术实现要素:

4.本发明实施例的目的在于:提供一种功率半导体封装结构,其能够解决现有技术的半导体封装结构存在的散热慢的技术问题。

5.为达上述目的,本技术采用以下技术方案:

6.一种功率半导体封装结构,包括芯片、引线框架和封装树脂,所述芯片具有相对设置的第一表面以及第二表面,所述第一表面与所述引线框架焊接连接,所述引线框架与所述芯片封装在所述封装树脂中,所述芯片的第二表面不与所述引线框架连接且其正对方向无所述封装树脂遮挡。

7.优选的,所述芯片的周部设置有限位结构,所述封装树脂具有与所述限位结构接触的承载面,所述承载面限制所述芯片向远离所述引线框架的方向移动。

8.优选的,所述限位结构包括限位凹槽,所述限位凹槽设置在所述第一表面与所述第二表面之间。

9.优选的,所述限位结构包括设置于所述芯片的周部的限位凸起,所述限位凸起远离所述第一表面的一侧为限位面,所述承载面与所述限位面形状相配合且抵靠所述限位面,从而限制所述芯片向远离所述引线框架的方向移动。

10.优选的,所述限位面为与所述第一表面平行的平面。

11.优选的,所述限位面为具有若干平行于所述第一表面的平面的阶梯面。

12.优选的,所述限位面为与所述第一表面之间形成一定夹角的锥面。

13.优选的,所述第二表面还设置有芯片保护层,所述芯片保护层覆盖整个所述第二表面无封装树脂遮挡的部分,所述芯片保护层远离所述第二表面的表面与封装树脂齐平。

14.优选的,所述芯片保护层周部形成有保护层限位部,所述保护层限位部延伸至所述封装树脂内部。

15.优选的,所述保护层限位部嵌入所述芯片的侧部内或向远离所述芯片的侧壁的方

向延伸。

16.优选的,所述芯片为二极管芯片或三极管芯片。

17.本技术的有益效果为:本发明提供了一种功率半导体封装结构,芯片和引线框架连接后,通过封装树脂塑封进行固定,使半导体形成一个固定整体,其中,芯片的第一表面(即顶面)与引线框架连接后被封装树脂包裹,第二表面(即底面)不与引线框架连接且无封装树脂遮挡,芯片工作过程中产生的热量,可直接从芯片底面散出,无需经过引线框架的传导,缩短了传导途径,减少了热阻,从而起到加快散热效率的有益效果。

附图说明

18.下面根据附图和实施例对本技术作进一步详细说明。

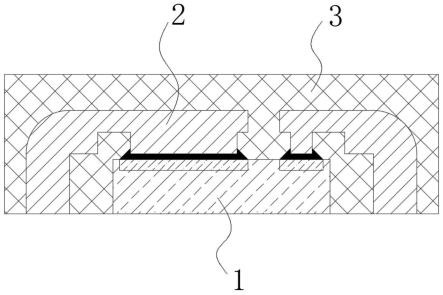

19.图1为现有技术的功率半导体封装结构的剖面示意图;

20.图2为本发明的功率半导体封装结构一种实施方式的剖面示意图;

21.图3为本发明的功率半导体封装结构另一种实施方式的剖面示意图;

22.图4为图3的结构的芯片和引线框架的组合状态结构示意图;

23.图5为本发明的功率半导体封装结构再一种实施方式的剖面示意图;

24.图6为本发明的功率半导体封装结构再一种实施方式的剖面示意图;

25.图7为本发明的功率半导体封装结构再一种实施方式的剖面示意图;

26.图8为本发明的功率半导体封装结构再一种实施方式的芯片的底部结构示意图;

27.图9为图8的结构的侧面的结构示意图;

28.图10为本发明的功率半导体封装结构再一种实施方式的剖面示意图;

29.图11为本发明的功率半导体封装结构再一种实施方式的剖面示意图;

30.图12为本发明的功率半导体封装结构再一种实施方式的剖面示意图;

31.图13为本发明的功率半导体封装结构再一种实施方式的剖面示意图;

32.图14为本发明的功率半导体封装结构再一种实施方式的剖面示意图;

33.图15为本发明的功率半导体封装结构再一种实施方式的剖面示意图。

34.图中:

35.1、芯片;11、限位凸起;12、限位凹槽;2、引线框架;3、封装树脂;4、芯片保护层;41、保护层限位部。

具体实施方式

36.为使本技术解决的技术问题、采用的技术方案和达到的技术效果更加清楚,下面对本技术实施例的技术方案作进一步的详细描述,显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

37.在本技术的描述中,除非另有明确的规定和限定,术语“相连”“连接”、“固定”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或成一体;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通或两个元件的相互作用关系。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本发明中的具体含义。

38.在本技术中,除非另有明确的规定和限定,第一特征在第二特征之“上”或之“下”可以包括第一和第二特征直接接触,也可以包括第一和第二特征不是直接接触而是通过它们之间的另外的特征接触。而且,第一特征在第二特征“之上”、“上方”和“上面”包括第一特征在第二特征正上方和斜上方,或仅仅表示第一特征水平高度高于第二特征。第一特征在第二特征“之下”、“下方”和“下面”包括第一特征在第二特征正下方和斜下方,或仅仅表示第一特征水平高度小于第二特征。

39.半导体是一种导电能力介于导体与非导体之间的材料,半导体元件根据半导体材料的特性,属于固态元件,其体积可以缩小到很小的尺寸,因此耗电量少,集成度高,在电子技术领域获得了广泛的引用,而随着半导体元件运行功率的逐渐增加,散热性能成为半导体元件的重要指标之一,在这样的高热量工作环境下,保持半导体元件的工作可靠性是一个非常重要的问题。

40.参照图1,传统的功率半导体封装结构中,芯片1都是通过焊接或胶接于引线框架2上方,芯片1产生的热需要通过焊接或胶接材料传递至引线框架2,再由引线框架2传递至外界,热传导路径较长,热阻较大,导致功率半导体存在散热慢的技术问题。

41.为此,本技术提供以下实施例解决上述问题:

42.一种功率半导体封装结构,包括芯片1、引线框架2和封装树脂3,所述芯片1具有相对设置的第一表面(即芯片的顶面)以及第二表面(即芯片的底面),所述第一表面与所述引线框架2焊接连接,所述引线框架2与所述芯片1封装在所述封装树脂3中,所述芯片1的第二表面不与所述引线框架2连接且其正对方向无所述封装树脂3遮挡。

43.基于本实施例的功率半导体封装结构,芯片1工作过程中产生的热量,可直接从芯片底面散出,无需经过引线框架的传导,缩短了传导途径,减少了热阻,从而起到加快散热效率的有益效果。

44.本方案的功率半导体在封装之前,将引线框架2与芯片1焊接连接实现电性导通,之后再对引线框架2和芯片1进行塑封;结合图1,与传统的方案相比,本方案的芯片1无需以其他的引线框架作为支撑体,由此省略了将芯片1固定到其他引线框架上的步骤,因此本方案还具有简化生产工序的效果,其中,塑封优选采用树脂材料。

45.为加强芯片1与塑封体3的结合,避免芯片1从封装树脂3内脱落,本实施例中,所述芯片1的周部设置有限位结构,所述封装树脂3具有与所述限位结构接触的承载面,所述承载面限制所述芯片向远离所述引线框架的方向移动。以此,利用封装树脂3的承载面限制限位结构11,可使芯片1无法从封装树脂3内脱离,对芯片1起到有效的加固效果。

46.对于本实施例的限位结构,作为一种较佳的设置方式,参照图3-4,所述限位结构包括限位凹槽12,所述限位凹槽12设置在所述第一表面与所述第二表面之间。即,在芯片1的侧壁开有限位凹槽12以形成限位结构,在塑封时,封装树脂3填充限位凹槽12,封装树脂3位于限位凹槽12内的部分朝向第一表面的一面为承载面,固化后承载面顶靠限位凹槽12使芯片1无法脱离,即可实现令芯片1和封装树脂3牢固结合。

47.作为另一种较佳的设置方式,所述限位结构包括设置于所述芯片1的周部的限位凸起11,所述限位凸起11远离所述第一表面的表面为限位面,所述承载面抵靠所述限位面从而限制所述芯片11向远离所述引线框架2的方向移动。需要说明的是,限位凸起11的形成,可以通过在芯片1周部靠近第一表面的部分增设材料或在芯片1周部靠近第二表面的部

分去除一定材料实现,使芯片1靠近第一表面的一侧形成相对第二表面凸出的结构,即形成了所述限位凸起11。

48.限位凸起11远离所述第一表面的表面为限位面,封装树脂3与限位面贴合的一面则为所述承载面,以此承载面可以给与限位面朝向第一表面的作用力,进而实现将芯片1限制固定在封装树脂3内。

49.本方案中限位面的形态的可以为多种,例如:

50.参照图5所示,在该实施方式中所述限位面为与所述第一表面平行的平面。

51.参照图6所示,在该实施方式中所述限位面为具有若干平行于所述第一表面的平面的阶梯面。

52.参照图7所示,在该实施方式中,所述限位件为与所述第一表面之间形成一定夹角的锥面。

53.可选的,该倾斜面可以从第二表面延伸至第一表面,也可从第二表面延伸至芯片的侧壁的中部,本实施例中采用从第二表面延伸至芯片的侧壁的中部的方案。

54.上述各实施方式中的限位凸起11的形成采用在芯片1靠近第二表面的部分去除附近材料的方式形成,相对于在芯片1的侧壁开限位凹槽12,此方式加工更加简单,加工难度低。

55.上述实施方式中限位凸起11均为整周设置在所述芯片1的周部,然而,在实际应用中,限位凸起11并不限于为整周的形式,如图8-9所示,其还可以为在芯片1的周部间隔设置若干限位凸起11结构。

56.其中,限位凸起11的形成,当采用在芯片1上去除部分材料形成时,可通过多次切割方法实现,切割方法可采用刀片锯割或激光划槽。

57.为进一步加强对芯片1的保护,参照图10-15,所述第二表面还设置有芯片保护层4,所述芯片保护层4覆盖芯片1整个所述第二表面无封装树脂遮挡的部分,所述芯片保护层4远离所述第二表面的表面与封装树脂齐平。由此,芯片保护层4对芯片1起到一定的保护作用。优选地,为了保证较好的散热效果,芯片保护层4的厚度应较引线框架2的厚度薄,芯片保护层4为铜片。相较于现有技术采用引线框架支撑芯片,芯片保护层4导热性能好,其对芯片1的导热效果好。

58.其中,芯片保护层4的结构,可结合芯片的第二表面的实际形态设置,如图9,芯片保护层4完全覆盖芯片1的第二表面,如图11-12,当芯片1的第二表面部分材料被去除时,芯片保护层4的形状与之做相应调整,使芯片保护层4恰好能够贴合芯片保护层4的第二表面。

59.进一步的,也可对芯片保护层4的形状做进一步优化,以加强其与封装树脂3的结合。

60.如图13-15,所述芯片保护层4周部形成有保护层限位部41,所述保护层限位部41延伸至所述封装树脂3内部。芯片保护层4至少需要包裹芯片的第二表面的整个表面,位于芯片保护层4的第二表面之外的部分为其周部,此时可使芯片保护层4的周部向远离芯片1的第二表面的方向延伸,即为使芯片保护层4的周部延伸入封装树脂3内以形成所述保护层限位部41。

61.参照图13的形态,芯片保护层4的周部沿芯片1的侧壁向上翻折嵌入封装树脂3内形成保护层限位部41,保护层限位部41有效增大了芯片保护层4与封装树脂3的结合面积,

提高芯片保护层4的稳固性。此外,此方式还能够使芯片保护层4紧贴芯片的第二表面,因此无需担心芯片保护层4脱落,无需在芯片保护层4与芯片1之间设置粘胶粘接,从而保证较低的热阻,提高散热效率。

62.进一步的,所述保护层限位部41嵌入所述芯片1的侧部内或向远离所述芯片1的侧壁的方向延伸。

63.即,参照图14的形态,保护层限位部41向远离第二表面的方向延伸一定距离后,保护层限位部41再向远离芯片1的侧壁方向延伸,此时保护层限位部41被锁紧于封装树脂3内。

64.参照图15的形态,在芯片1的侧壁开有限位凹槽,保护层限位部41向远离第二表面的方向延伸一定距离后,保护层限位部41再向内弯折延伸入限位凹槽内,此时保护层限位部41被锁紧于限位凹槽内。

65.可选的,所述芯片为二极管芯片或三极管芯片。

66.综上,本实施例提供了一种功率半导体封装结构,封装树脂3不对芯片1的第二表面进行包裹,芯片1工作过程中产生的热量,可直接从芯片1第二表面散出,无需经过引线框架2的传导,缩短了传导途径,减少了热阻,从而起到加快散热效率的有益效果。在芯片1底部设置有导热效果好的芯片保护层4,对芯片1其保护作用。

67.于本文的描述中,需要理解的是,术语“上”、“下”、“左”、“右”、等方位或位置关系,仅是为了便于描述和简化操作,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本技术的限制。此外,术语“第一”、“第二”,仅仅用于在描述上加以区分,并没有特殊的含义。

68.在本说明书的描述中,参考术语“一实施例”、“示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施例或示例。

69.此外,应当理解,虽然本说明书按照实施方式加以描述,但并非每个实施方式仅包含一个独立的技术方案,说明书的这种叙述方式仅仅是为清楚起见,本领域技术人员应当将说明书作为一个整体,各实施例中的技术方案也可以适当组合,形成本领域技术人员可以理解的其他实施方式。

70.以上结合具体实施例描述了本技术的技术原理。这些描述只是为了解释本技术的原理,而不能以任何方式解释为对本技术保护范围的限制。基于此处的解释,本领域的技术人员不需要付出创造性的劳动即可联想到本技术的其它具体实施方式,这些方式都将落入本技术的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1