一种半导体表面平坦化的方法及制得的半导体和用途与流程

1.本发明涉及半导体制造技术领域,尤其涉及一种半导体表面平坦化的方法及制得的半导体和用途。

背景技术:

2.在半导体制造工艺中,cu的化学机械抛光主要是用于后段大马士革金属铜表面的平坦化。

3.金属铜化学机械研磨主要通过三个研磨盘进行,第一研磨盘进行大压力铜的去除,去除沟槽上方大部分的铜;第二研磨盘用相对小的压力去除沟槽上方剩余的金属铜;第三研磨盘对沟槽和旁边的氧化层进行减薄到工艺需求的厚度。

4.现有技术通常在第二研磨盘探测到研磨终点时仍然继续研磨,以确保完全去除沟槽上方剩余的金属铜,探测到研磨终点后一般会有一段过抛过程来确保沟槽上方金属铜去除干净。而在过抛过程中会形成具有铜凹陷的蝶形结构,而过抛时间越长蝶形深度越大。

5.在半导体多层互连结构中,具有严重的碟形凹陷的不平坦的硅片表面将会产生一系列问题,其中最为严重的就是无法在硅片表面进行图形制作,从而导致后续制程的稳定性降低,影响多层互连结构中金属铜化学机械抛光的工艺窗口。

6.另一方面,对铜进行化学机械抛光时进行的过度研磨所产生的碟形凹陷还会导致铜互连线的电阻过大,造成半导体器件的处理速度变慢,甚至由于发热过大而将铜互连线熔断,从而发生半导体器件的断路。

7.cn108682650a公开了一种表面平坦化方法及半导体多层互连结构,该方法包括:第一化学机械抛光工序,对半导体多层互连结构中沉积于深孔的金属进行化学机械抛光;第二介质层形成工序,在半导体多层互连结构中阻挡层的表面形成第二介质层;以及第二化学机械抛光工序,对第二介质层及阻挡层进行化学机械抛光。但该方法新增第二介质层的形成工序和化学机械抛光程序,成本高。诸如cn1855417a和cn1855420a的方法同样存在成本较高,工艺较为复杂的问题。

8.因此,需要成本较低的、能够控制蝶形凹陷的大小的半导体表面平坦化工艺。

技术实现要素:

9.鉴于现有技术中存在的问题,本发明提供一种半导体表面平坦化的方法及制得的半导体和用途,所述方法在不改变原有沉积工艺的基础上,仅通过增加一道平坦化处理工序,就解决了多层互连结构中蝶形凹陷的叠加问题,提高了多层互连结构半导体的性能。

10.为达此目的,本发明采用以下技术方案:

11.第一方面,本发明提供一种半导体表面平坦化的方法,所述方法包括:

12.在半导体至少两层互连结构的第n段制造工艺中,覆盖第n段初始介质层后,所述第n段初始介质层先经厚度方向上的平坦化处理,得到第n段介质层,再进行后续工序;

13.所述第n段初始介质层的厚度大于第n段介质层的厚度,n≥2。

14.本发明所述方法通过在覆盖第n段初始介质层时,使第n段初始介质层的厚度比现有技术的介质层厚度厚,再通过增设平坦化处理步骤,使处理后的第n段初始介质层不再具有蝶形凹陷,为平坦表面,从而解决了多层互连结构中半导体表面蝶形凹陷的叠加问题。

15.本发明所述n的取值范围为≥2的自然数,例如可以是2、3、4、5或6等,可根据实际工艺进行调整,只要是在第1段制造工艺基础上叠加的制造工艺即可。

16.优选地,所述平坦化处理的方法包括化学机械抛光方法。

17.优选地,所述第n段初始介质层的厚度大于第1段制造工艺中第1段介质层的厚度。由于具有平坦化处理步骤,将其在厚度方向上去除一层厚度,同时去除具有第n段初始介质层中具有凹陷的部分,得到第n段介质层的平坦表面。

18.优选地,所述第n段介质层的厚度等于第1段制造工艺中第1段介质层的厚度。

19.一般情况下,多层互连结构的半导体每一层的介质层设置相同,因此本发明优选第n段介质层的厚度与第1段介质层的厚度相同,但也可根据实际情况设置每一段的介质层厚度,只要满足最终第n段介质层的厚度复合预期设计厚度即可。

20.优选地,所述第n段初始介质层的表面含有蝶形凹陷。由于第1段介质层或者前面段介质层的表面形貌是具有蝶形凹陷的,这一蝶形凹陷是由于第1段制造工艺或前1段制造工艺对金属进行研磨时,为了确保完全去除沟槽上方剩余的金属,因此一般需要过抛来保障沟槽上方金属去除干净,而在过抛过程中就会导致对沟槽内部金属的去除,从而造成蝶形凹陷的形成。在上述工艺的基础上,继续在其表面覆盖介质层,上一蝶形凹陷将继续保留,因此第n段初始介质层的表面含有蝶形凹陷。

21.优选地,所述第n段初始介质层的厚度比第n段介质层的厚度多出的厚度值大于所述蝶形凹陷的深度值。为了确保经平坦化处理后的介质层表面既没有蝶形凹陷,其厚度值又能符合标准,本发明优选所述第n段初始介质层的厚度比第n段介质层的厚度多出的厚度值大于所述蝶形凹陷的深度值,从而能够为平坦化处理预留足够的操作厚度。

22.优选地,所述第n段初始介质层的厚度比第n段介质层的厚度多2000~3000a,例如可以是2000a、2100a、2200a、2300a、2400a、2500a、2600a、2800a或3000a等。虽然本发明也可根据实际工艺设计情况,对所述第n段初始介质层的厚度比第n段介质层的厚度之间的差值进行适当调整;但出于现有单段蝶形凹陷的厚度一般在2000a左右考虑,本发明中优选限定第n段初始介质层的厚度比第n段介质层的厚度多2000~3000a,能够更好地符合半导体的结构设计。

23.本发明一般对所述后续工序不做特殊限定,采用本领域技术人员熟知的后续制造工艺即可,也可根据实际工艺情况进行调整,但进一步优选地,在第n段制造工艺中,所述后续工序依次包括覆盖蚀刻阻挡层、光刻、蚀刻、覆盖阻挡层、覆盖金属层和抛光。

24.优选地,所述抛光包括化学机械抛光。

25.优选地,所述覆盖金属层包括依次进行的光刻、蚀刻和沉积。

26.优选地,所述制造工艺包括大马士革制造工艺。

27.本发明对所述大马士革制造工艺中的其他工艺参数没有特殊限制,可采用本领域技术人员熟知的任何可用于大马士革制造工艺的工艺参数进行,也可根据实际工艺进行调整。

28.优选地,所述金属层包括铜层。

29.本发明对所述介质层的材质和厚度没有特殊限制,采用本领域技术人员熟知的任何可用于半导体中介质层的材质和厚度即可,例如可以包括氧化物和/或氮化物,例如可以是氮化硅或氧化硅等,厚度例如可以是2500a等。

30.本发明对所述阻挡层的材质和厚度没有特殊限制,采用本领域技术人员熟知的任何可用于半导体中阻挡层的材质和厚度即可,例如可以包括氧化物和/或氮化物,例如可以是正硅酸四乙酯(teos)制备的氧化硅等,厚度例如可以是400a等。

31.作为本发明优选地技术方案,所述方法包括如下步骤:

32.(1)进行第一段大马士革制造工艺,得到第1段半导体结构;

33.(2)在步骤(1)所述第1段半导体结构的表面覆盖第n段初始介质层后,所述第n段初始介质层先经厚度方向上的平坦化处理,得到第n段介质层;所述第n段初始介质层的厚度大于第n段介质层的厚度,n≥2;

34.(3)在所述第n段介质层的表面覆盖蚀刻阻挡层、光刻、蚀刻、覆盖阻挡层、覆盖金属层和抛光,得到第n段半导体结构;

35.重复步骤(2)~(3)直至得到设计的半导体。

36.第二方面,本发明提供一种半导体,所述半导体根据第一方面所述的半导体表面平坦化的方法制得。

37.本发明所述半导体由于蝶形凹陷小,金属互连线的电阻低,最终形成的半导体器件的处理速度快,而且能够减少半导体器件的断路现象。

38.优选地,所述半导体具有至少两层互连结构。本发明所述至少两层互连结构是指具有至少两个重复的竖直叠加的半导体结构单元。

39.本发明对每一段内半导体的结构单元没有特殊限制,可采用本领域技术人员熟知的任何半导体的单元结构,也可根据实际情况进行调整。

40.优选地,所述半导体中自下向上第1段半导体结构包括介质层,所述介质层的表面设置有第一阻挡层,所述介质层和第一阻挡层在对应位置设置有凹槽,所述第一阻挡层的凹槽从第一阻挡层表面贯穿至介质层中,所述介质层和第一阻挡层对应凹槽内沉积有金属,所述凹槽内金属的表面含有蝶形凹陷。其他段半导体结构优选与第1段半导体结构相同。

41.优选地,所述半导体为晶圆。通过进一步优选为晶圆,显著降低了晶圆的蝶形凹陷程度。

42.第三方面,本发明提供一种第一方面所述的半导体在集成电路中的用途。

43.本发明所述半导体由于蝶形凹陷小,因此具有优良的处理速度和低电阻,应用在集成电路中,能够大幅增加集成电路的运行效率。

44.与现有技术相比,本发明至少具有以下有益效果:

45.(1)本发明提供的半导体表面平坦化的方法克服了至少两层互连结构中前段制造工艺产生的蝶形凹陷在后段工艺叠加的影响,仅需要在原始步骤中增加介质层厚度减薄步骤即可使蝶形大小得到了有效控制,第n段半导体结构的蝶形凹陷的深度与第1段半导体结构的蝶形凹陷的深度的差值≤70a,在优选条件下≤20a,甚至可达到≤2a或第n段半导体结构的蝶形凹陷的深度比第1段半导体结构的蝶形凹陷的深度小,而且制备工艺流程简单,成本低廉;

46.(2)本发明提供的半导体由于蝶形凹陷小,金属互连线的电阻低,最终形成的半导体器件的处理速度快,而且能够减少半导体器件的断路现象,能够较好的应用在集成电路中。

附图说明

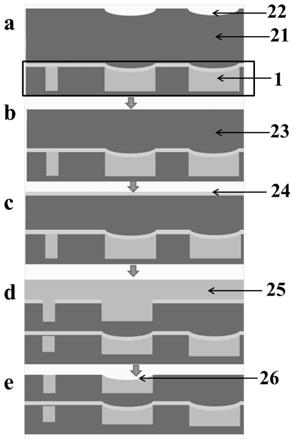

47.图1是本发明提供的半导体表面平坦化的方法流程示意图。

48.图2是对比例1提供的半导体的制备方法流程示意图。

49.图中:1

‑

第1段半导体结构;21

‑

第2初始介质层;22

‑

第2初始介质层表面的蝶形凹陷;23

‑

第2介质层;24

‑

蚀刻阻挡层;25

‑

金属铜;26

‑

金属铜表面的蝶形凹陷。

具体实施方式

50.下面结合附图并通过具体实施方式来进一步说明本发明的技术方案。

51.下面对本发明进一步详细说明。但下述的实例仅仅是本发明的简易例子,并不代表或限制本发明的权利保护范围,本发明的保护范围以权利要求书为准。

52.需要理解的是,在本发明的描述中,术语“中心”、“纵向”、“横向”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。此外,术语“第一”、“第二”等仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”等的特征可以明示或者隐含地包括一个或者更多个该特征。在本发明的描述中,除非另有说明,“多个”的含义是两个或两个以上。

53.需要说明的是,在本发明的描述中,除非另有明确的规定和限定,术语“设置”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以通过具体情况理解上述术语在本发明中的具体含义。

54.作为本发明的一个具体实施方式,提供一种半导体表面平坦化的方法,以两段大马士革工艺为例,如图1所示,所述方法包括如下步骤:

55.(1)进行第一段大马士革制造工艺,得到第1段半导体结构1,所述第1段半导体结构1包括介质层,所述介质层的表面设置有第一阻挡层,所述介质层和第一阻挡层在对应位置设置有凹槽,所述第一阻挡层的凹槽从第一阻挡层表面贯穿至介质层中,所述介质层内沉积有金属铜,所述凹槽内金属铜的表面含有蝶形凹陷;

56.(2)在步骤(1)所述第1段半导体结构1的表面覆盖第2初始介质层21后,得到覆盖有第2初始介质层21的半导体结构,如图1中a所示,此时可以看到第2初始介质层表面的蝶形凹陷22;

57.所述第2初始介质层21先经厚度方向上的平坦化处理,得到第2介质层23,如图1中b所示;所述第2初始介质层21的厚度大于第2介质层23的厚度;

58.(3)依次在所述第2介质层23的表面覆盖蚀刻阻挡层24、光刻、蚀刻、覆盖第二阻挡

层(未示出)、覆盖金属铜25和抛光,覆盖蚀刻阻挡层24后如图1中c所示、覆盖金属铜25后如图1中d所示、抛光后如图1中e所示,可以看出第1段半导体结构1的蝶形凹陷并未传递至第2段,得到第2段半导体结构;成型后的所述第2段半导体结构包括第2介质层23,所述介质层23的表面设置有凹槽,所述介质层23对应凹槽内沉积有金属铜25,所述凹槽内金属铜25的表面含有金属铜表面的蝶形凹陷26,得到设计的双层大马士革金属铜晶圆。

59.上述具体实施方式中,凹槽的深度不做特殊限定,可根据实际工艺进行调整,例如可以是200a等。同样对介质层、蚀刻阻挡层、第一阻挡层和第二阻挡层的厚度不做特殊限定,可根据实际工艺进行调整,例如介质层的厚度可以是2500a等,第一阻挡层和第二阻挡层的厚度可以是400a等。

60.实施例1

61.本实施例提供一种半导体表面平坦化的方法,所述方法包括如下步骤:

62.(1)进行第1段大马士革制造工艺,所述第1段大马士革制造工艺具体包括:在介质层(氧化硅)的表面进行化学气相沉积400a的蚀刻阻挡层(氧化硅),然后依次进行光刻、蚀刻和铜沉积(电镀,工艺参数为7000a),再进行三次化学机械抛光,第一次化学机械抛光进行大压力~2psi研磨,去除沟槽上方大部分的铜;第二次化学机械抛光用相对小的压力~1.2psi去除沟槽上方剩余的金属铜;第三次化学机械抛光对沟槽和旁边的氧化硅进行减薄到工艺需求的厚度~1000a,并沉积第一阻挡层,所述第一阻挡层为用于阻止金属向介质层扩散的碳化硅层,厚度为200a,得到第1段半导体结构1;所述介质层的表面设置有第一阻挡层,所述介质层和第一阻挡层在对应位置设置有凹槽,所述第一阻挡层的凹槽从第一阻挡层表面贯穿至介质层中,所述介质层内沉积有金属铜,所述凹槽内金属铜的表面含有蝶形凹陷;

63.(2)在步骤(1)所述第2段半导体结构的表面覆盖第2初始介质层21后,所述第2初始介质层21先经厚度方向上的平坦化处理,所述平坦化处理为化学机械抛光处理,压力为~2.0psi,时间为~30s得到第2介质层23;所述第2初始介质层21的厚度比第2介质层23的厚度厚2500a;

64.(3)在所述第2介质层23的表面覆盖蚀刻阻挡层24(氧化硅、400a)、经光刻、蚀刻、沉积第二阻挡层以及覆盖金属铜25和三次化学机械抛光,其中所述第二阻挡层为用于阻止金属向介质层扩散的氮化钽层,厚度为100a,该三次化学机械抛光和沉积等步骤参照步骤(1)进行,得到第2段半导体结构,得到设计的双层大马士革金属铜晶圆。

65.实施例2

66.本实施例提供一种半导体表面平坦化的方法,所述方法包括如下步骤:

67.(1)进行第1段大马士革制造工艺,所述第1段大马士革制造工艺具体包括:在介质层(氧化硅)的表面沉积(化学气相沉积,工艺参数为300a)蚀刻阻挡层(氧化硅)并依次进行光刻、蚀刻和铜沉积(电镀,工艺参数为7500a),再进行三次化学机械抛光,第一次化学机械抛光进行大压力~2.5psi研磨,去除沟槽上方大部分的铜;第二次化学机械抛光用相对小的压力~1.4psi去除沟槽上方剩余的金属铜;第三次化学机械抛光对沟槽和旁边的氧化层进行减薄到工艺需求的厚度~1600a,并沉积第一阻挡层,即碳化硅,厚度为150a,得到第1段半导体结构1;所述第1段半导体结构1包括介质层,所述介质层的表面设置有第一阻挡层,所述介质层和第一阻挡层在对应位置设置有凹槽,所述第一阻挡层的凹槽从第一阻挡

层表面贯穿至介质层中,所述介质层内沉积有金属铜,所述凹槽内金属铜的表面含有蝶形凹陷;

68.(2)在步骤(1)所述第2段半导体结构的表面覆盖第2初始介质层21后,所述第2初始介质层21先经厚度方向上的平坦化处理,所述平坦化处理为化学机械抛光处理,压力为~2.5psi,时间为~30s,得到第2介质层23;所述第2初始介质层21的厚度比第2介质层23的厚度厚2000a;

69.(3)在所述第2介质层23的表面覆盖蚀刻阻挡层24(500a)、并依次经光刻、蚀刻、沉积第二阻挡层和覆盖金属铜层和三次化学机械抛光,其中所述第二阻挡层为用于阻止金属向介质层扩散的氮化钽层,厚度为120a,该三次化学机械抛光和沉积等步骤参照步骤(1)进行,得到第2段半导体结构,得到设计的双层大马士革金属铜晶圆。

70.实施例3

71.本实施例提供一种半导体表面平坦化的方法,所述方法包括如下步骤:

72.(1)进行第1段大马士革制造工艺,所述第1段大马士革制造工艺具体包括:在介质层(氧化硅)的表面沉积(化学气相沉积,工艺参数为600a)蚀刻阻挡层(氧化硅)并蚀刻深孔,然后依次进行光刻、蚀刻和铜沉积(电镀,工艺参数为8000a),再进行三次化学机械抛光,第一次化学机械抛光进行大压力~1.8psi研磨,去除沟槽上方大部分的铜;第二次化学机械抛光用相对小的压力~1.5psi去除沟槽上方剩余的金属铜;第三次化学机械抛光对沟槽和旁边的氧化层进行减薄到工艺需求的厚度~1200a,得到第1段半导体结构1;所述第1段半导体结构1包括介质层,所述介质层的表面设置有第一阻挡层,所述介质层和第一阻挡层在对应位置设置有凹槽,所述第一阻挡层的凹槽从第一阻挡层表面贯穿至介质层中,所述介质层内沉积有金属铜,所述凹槽内金属铜的表面含有蝶形凹陷;

73.(2)在步骤(1)所述第2段半导体结构的表面覆盖第2初始介质层21后,所述第2初始介质层21先经厚度方向上的平坦化处理,所述平坦化处理为化学机械抛光处理,压力为~2.1psi,时间为~35s,得到第2介质层23;所述第2初始介质层21的厚度比第2介质层23的厚度厚3000a;

74.(3)在所述第2介质层23的表面覆盖蚀刻阻挡层24(400a)并依次经光刻、蚀刻、沉积第二阻挡层、覆盖金属铜25和三次化学机械抛光,其中所述第二阻挡层为用于阻止金属向介质层扩散的氮化钽层,厚度为110a,该三次化学机械抛光和沉积等步骤参照步骤(1)进行,得到第2段半导体结构;

75.重复步骤(2)~(3)在所述第2段半导体结构上构造第3段半导体结构,得到设计的三层大马士革金属铜晶圆。

76.实施例4

77.本实施例提供一种半导体表面平坦化的方法,所述方法除所述第2初始介质层21的厚度比第2介质层23的厚度厚6000a外,其余均与实施例1相同。本实施例与实施例1相比,由于初始沉积介质层的厚度较厚,成本增加较多。

78.实施例5

79.本实施例提供一种半导体表面平坦化的方法,所述方法除所述第2初始介质层21的厚度比第2介质层23的厚度厚200a外,其余均与实施例1相同。本实施例由于初始沉积的介质层厚度不够填补由于第1段工艺累积的蝶形凹陷的深度,平坦化处理后第2介质层23的

表面仍然具有小幅的蝶形凹陷。

80.对比例1

81.本对比例提供一种半导体制备的方法,如图2所示,所述方法除步骤(2)中覆盖第2初始介质层21的厚度直接与实施例1中第2介质层23的厚度相同外,步骤(1)~(3)中的制备工艺参数均与实施例1相同,具体包括如下步骤:

82.(1)进行第1段大马士革制造工艺,所述第1段大马士革制造工艺具体包括:在介质层(氧化硅)的表面进行化学气相沉积400a的蚀刻阻挡层(氧化硅),然后依次进行光刻、蚀刻和铜沉积(电镀,工艺参数为7000a),再进行三次化学机械抛光,第一次化学机械抛光进行大压力~2psi研磨,去除沟槽上方大部分的铜;第二次化学机械抛光用相对小的压力~1.2psi去除沟槽上方剩余的金属铜;第三次化学机械抛光对沟槽和旁边的氧化硅进行减薄到工艺需求的厚度~1000a,并沉积第一阻挡层,所述第一阻挡层为用于阻止金属向介质层扩散的碳化硅层,厚度为200a,得到第1段半导体结构1;所述介质层的表面设置有第一阻挡层,所述介质层和第一阻挡层在对应位置设置有凹槽,所述第一阻挡层的凹槽从第一阻挡层表面贯穿至介质层中,所述介质层内沉积有金属铜,所述凹槽内金属铜的表面含有蝶形凹陷;

83.(2)在步骤(1)所述第2段半导体结构的表面覆盖第2介质层23;

84.(3)依次在所述第2介质层23的表面覆盖蚀刻阻挡层24(氧化硅、400a)、并依次经光刻、蚀刻、沉积第二阻挡层以及覆盖金属铜25和三次化学机械抛光,其中所述第二阻挡层为用于阻止金属向介质层扩散的氮化钽层,厚度为100a,蚀刻阻挡层24后如图2中c所示、覆盖金属铜25后如图2中d所述、抛光后如图2中e所示,可以看出第1段半导体结构1的蝶形凹陷继续传递至第2段,得到第2段半导体结构;成型后的所述第2段半导体结构包括第2介质层23,所述介质层23设置有凹槽,所述介质层23沉积的凹槽内有金属铜25,所述凹槽内金属铜25的表面含有金属铜表面的蝶形凹陷26,得到设计的双层大马士革金属铜晶圆,但所述晶圆中第2段半导体结构的蝶形凹陷较第1段半导体结构1的蝶形凹陷显著增加。

85.本发明所述方法还可适用于其他多段半导体结构的半导体制造,出于篇幅的考虑,在此不再赘述。

86.测试方法:采用afm(原子力显微镜)方法测量上述实施例和对比例制得的晶圆中的蝶形凹陷的深度,结果如表1所示。

87.表1

[0088][0089][0090]

从表1可以看出以下几点:

[0091]

(1)综合实施例1~3可以看出,本发明提供的半导体表面平坦化的方法在至少两段的半导体结构制造过程中,能够有效组织第1段半导体结构中蝶形凹陷的深度值向第2段半导体结构或第3段半导体结构转化,即大于1段的半导体结构的蝶形凹陷的深度与第1段半导体结构的蝶形凹陷深度的差值≤20a;

[0092]

(2)综合实施例1和实施例4~5可以看出,实施例1中所述第2初始介质层的厚度比第2介质层的厚度厚2500a,相较于实施例4和实施例5中所述第2初始介质层的厚度比第2介质层的厚度分别厚6000a和200a而言,实施例1中第2段半导体结构的蝶形凹陷仅为220a,相较于第1段增加15a,而实施例4中虽然仅比第1段增加2a,但介质层增加的厚度过多,成本增加显著,实施例5中第2段比第段增加70a,蝶形凹陷有一定程度的传递,由此表明,本发明通过将第n初始介质层的厚度比第n介质层的厚度加厚的值控制在特定范围内,能够减少蝶形凹陷传递的同时控制成本;

[0093]

(3)综合实施例1和对比例1可以看出,对比例1中直接在沉积时仅沉积最终第2介质层的厚度,最终第2段半导体结构的蝶形凹陷高达295a,比第1段半导体结构的蝶形凹陷高100a,远高于实施例1中的15a,由此表明,本发明通过增加初始沉积时介质层的厚度,并增加一步化学机械抛光步骤,显著减少了蝶形凹陷在几段半导体结构之间的传递。

[0094]

综上所述,本发明提供的半导体表面平坦化的方法克服了至少两层互连结构中前

段制造工艺产生的蝶形凹陷在后段工艺叠加的影响,使蝶形大小得到了有效控制,成本低,适合工业化推广。

[0095]

申请人声明,本发明通过上述实施例来说明本发明的详细结构特征,但本发明并不局限于上述详细结构特征,即不意味着本发明必须依赖上述详细结构特征才能实施。所属技术领域的技术人员应该明了,对本发明的任何改进,对本发明所选用部件的等效替换以及辅助部件的增加、具体方式的选择等,均落在本发明的保护范围和公开范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1