一种键合封装体及其制备方法与流程

1.本发明涉及半导体封装领域,特别是涉及一种键合封装体及其制备方法。

背景技术:

2.在现有的半导体封装结构中,当一半导体管芯中具备硅通孔结构时,需要利用化学机械掩膜工艺以暴露硅通孔的顶表面,进而将另一半导体管芯的导电焊盘通过焊料结合至该半导体管芯的该硅通孔结构,以完成半导体管芯的键合。然而在上述键合工艺中,半导体管芯的键合体中具有间隙,进而导致该键合体容易剥离倒塌,进而导致该键合体的功能失效。如何进一步改善键合体的结构,以防止键合体剥离倒塌,这引起了相关技术人员的广泛关注。

技术实现要素:

3.本发明的目的是克服上述现有技术的不足,提供一种键合封装体及其制备方法。

4.为实现上述目的,本发明采用的技术方案是:一种键合封装体的制备方法,包括以下步骤:步骤(1):提供第一半导体管芯,所述第一半导体管芯中具有硅通孔。

5.步骤(2):将所述第一半导体管芯设置于第一基板上,接着对所述第一半导管芯进行刻蚀处理,以在所述第一半导体管芯的四周分别形成第一、第二、第三、第四键合部,所述第一、第二、第三、第四键合部分别突出于所述第一半导体管芯的第一、第二、第三、第四侧表面。

6.步骤(3):接着对所述第一半导体管芯的上表面进行刻蚀处理,以在所述第一半导体管芯中形成第一凹槽,所述第一凹槽露出所述硅通孔,并在所述第一键合部上形成多个第一凸柱,在所述第二键合部上分别形成多个第二凸柱,在所述第三键合部上形成多个第三凸柱,在所述第四键合部上分别形成多个第四凸柱。

7.步骤(4):接着在第一凹槽中暴露的所述硅通孔上形成导电凸块。

8.步骤(5):提供第二半导体管芯,所述第二半导体管芯的上表面具有导电焊盘,将所述第二半导体管芯设置于第二基板上,接着对所述第二半导管芯进行刻蚀处理,以在所述第二半导体管芯的四周分别形成第五、第六、第七、第八键合部,所述第五、第六、第七、第八键合部分别突出于所述第二半导体管芯的第一、第二、第三、第四侧表面。

9.步骤(6):接着对所述第二半导体管芯的上表面进行刻蚀处理,以在所述第五、第六、第七、第八键合部上分别形成第一、第二、第三、第四沟槽。

10.步骤(7):接着在所述第二半导体管芯的所述导电焊盘上形成环形导电块。

11.步骤(8):接着将第二半导体管芯键合至所述第一半导体管芯,使得多个所述第一凸柱嵌入到所述第一沟槽中,多个所述第二凸柱嵌入到所述第二沟槽中,多个所述第三凸柱嵌入到所述第三沟槽中,多个所述第四凸柱嵌入到所述第四沟槽中,并使得所述导电凸块嵌入到所述环形导电块中,进而将所述导电焊盘电连接至所述硅通孔。

12.步骤(9):接着去除所述第二基板,然后形成塑封层以包裹所述第一、第二半导体管芯,接着去除所述第一基板。

13.步骤(10):接着在所述塑封层上形成重布线层,并在所述重布线层上形成导电焊球。

14.在更优选的技术方案中,在所述步骤(2)中,将所述第一半导体管芯设置于所述第一基板上之前,在所述第一基板上设置粘结层,进而利用所述粘结层粘结所述第一半导体管芯,通过湿法刻蚀工艺或干法刻蚀工艺对所述第一半导管芯进行刻蚀处理。

15.在更优选的技术方案中,在所述步骤(3)中,通过去除所述第一、第二、第三、第四键合部的一部分以分别形成多个所述第一、第二、第三、第四凸柱。

16.在更优选的技术方案中,在所述步骤(4)中,所述导电凸块的材质为铜、铝、钛、钯、银、镍、金中的一种或多种的组合,所述导电凸块通过电镀、化学镀、化学气相沉积或物理气相沉积工艺形成。

17.在更优选的技术方案中,在所述步骤(5)中,所述第五、第六、第七、第八键合部与所述第一、第二、第三、第四键合部分别一一对应。

18.在更优选的技术方案中,在所述步骤(7)中,所述环形导电块的材质为铜、铝、钛、钯、银、镍、金中的一种或多种的组合,所述环形导电块通过电镀、化学镀、化学气相沉积或物理气相沉积工艺形成。

19.在更优选的技术方案中,在所述步骤(8)中,先在所述第一、第二、第三、第四沟槽中设置黏附材料,进而利用所述黏附材料分别粘结所述第一、第二、第三、第四凸柱,在所述环形导电块中设置导电钎料,进而利用所述导电钎料粘结所述导电凸块。

20.在更优选的技术方案中,本发明还提出一种键合封装体,其采用上述制备方法制备形成的。

21.相较于现有技术,本发明的键合封装体及其制备方法有如下的有益效果:通过在所述第一半导体管芯的四周分别形成第一、第二、第三、第四键合部,并在所述第一半导体管芯中形成第一凹槽,所述第一凹槽露出硅通孔,并在所述第一键合部上形成多个第一凸柱,在所述第二键合部上分别形成多个第二凸柱,在所述第三键合部上形成多个第三凸柱,在所述第四键合部上分别形成多个第四凸柱,接着第一凹槽中暴露的所述硅通孔上形成导电凸块。进而通过在所述第二半导体管芯的四周分别形成第五、第六、第七、第八键合部,并在所述第五、第六、第七、第八键合部上分别形成第一、第二、第三、第四沟槽,在所述第二半导体管芯的所述导电焊盘上形成环形导电块,接着将第二半导体管芯键合至所述第一半导体管芯,使得多个所述第一凸柱嵌入到所述第一沟槽中,多个所述第二凸柱嵌入到所述第二沟槽中,多个所述第三凸柱嵌入到所述第三沟槽中,多个所述第四凸柱嵌入到所述第四沟槽中,并使得所述导电凸块嵌入到所述环形导电块中,进而将所述导电焊盘电连接至所述硅通孔。上述结构的设置,通过第一凹槽的设置为硅通孔与另一半导体管芯的电连接提供接合空间,且第一半导体管芯的四周边缘的形成第一、第二、第三、第四键合部以及第二半导体管芯的四周边缘的形成第五、第六、第七、第八键合部,进而可以提高第一、第二半导体管芯的键合强度,有效防止其剥离倒塌,且为硅通孔的电连接提供安装空间,进而可以提高电连接的稳定性。

附图说明

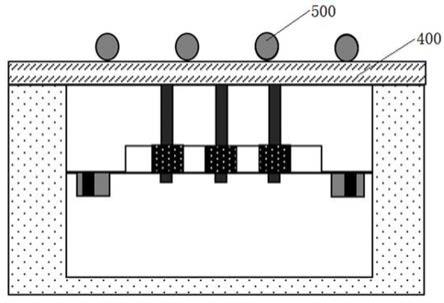

22.图1为本发明的键合封装体的制备过程中步骤(1)的结构示意图;图2为本发明的键合封装体的制备过程中步骤(2)的结构示意图;图3为本发明的键合封装体的制备过程中步骤(3)的结构示意图;图4为本发明的键合封装体的制备过程中步骤(4)的结构示意图;图5为本发明的键合封装体的制备过程中步骤(5)的结构示意图;图6为本发明的键合封装体的制备过程中步骤(6)的结构示意图;图7为本发明的键合封装体的制备过程中步骤(7)的结构示意图;图8为本发明的键合封装体的制备过程中步骤(8)的结构示意图;图9为本发明的键合封装体的制备过程中步骤(9)的结构示意图;图10为本发明的键合封装体的制备过程中步骤(10)的结构示意图。

具体实施方式

23.为了更好的理解本发明的技术方案,下面结合附图对本发明实施例进行详细描述。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其 它实施例,都属于本发明保护的范围。

24.本发明提出一种键合封装体的制备方法,包括以下步骤:步骤(1):提供第一半导体管芯,所述第一半导体管芯中具有硅通孔。

25.步骤(2):将所述第一半导体管芯设置于第一基板上,接着对所述第一半导管芯进行刻蚀处理,以在所述第一半导体管芯的四周分别形成第一、第二、第三、第四键合部,所述第一、第二、第三、第四键合部分别突出于所述第一半导体管芯的第一、第二、第三、第四侧表面。

26.步骤(3):接着对所述第一半导体管芯的上表面进行刻蚀处理,以在所述第一半导体管芯中形成第一凹槽,所述第一凹槽露出所述硅通孔,并在所述第一键合部上形成多个第一凸柱,在所述第二键合部上分别形成多个第二凸柱,在所述第三键合部上形成多个第三凸柱,在所述第四键合部上分别形成多个第四凸柱。

27.步骤(4):接着在第一凹槽中暴露的所述硅通孔上形成导电凸块。

28.步骤(5):提供第二半导体管芯,所述第二半导体管芯的上表面具有导电焊盘,将所述第二半导体管芯设置于第二基板上,接着对所述第二半导管芯进行刻蚀处理,以在所述第二半导体管芯的四周分别形成第五、第六、第七、第八键合部,所述第五、第六、第七、第八键合部分别突出于所述第二半导体管芯的第一、第二、第三、第四侧表面。

29.步骤(6):接着对所述第二半导体管芯的上表面进行刻蚀处理,以在所述第五、第六、第七、第八键合部上分别形成第一、第二、第三、第四沟槽。

30.步骤(7):接着在所述第二半导体管芯的所述导电焊盘上形成环形导电块。

31.步骤(8):接着将第二半导体管芯键合至所述第一半导体管芯,使得多个所述第一凸柱嵌入到所述第一沟槽中,多个所述第二凸柱嵌入到所述第二沟槽中,多个所述第三凸柱嵌入到所述第三沟槽中,多个所述第四凸柱嵌入到所述第四沟槽中,并使得所述导电凸块嵌入到所述环形导电块中,进而将所述导电焊盘电连接至所述硅通孔。

32.步骤(9):接着去除所述第二基板,然后形成塑封层以包裹所述第一、第二半导体

管芯,接着去除所述第一基板。

33.步骤(10):接着在所述塑封层上形成重布线层,并在所述重布线层上形成导电焊球。

34.其中,在所述步骤(2)中,将所述第一半导体管芯设置于所述第一基板上之前,在所述第一基板上设置粘结层,进而利用所述粘结层粘结所述第一半导体管芯,通过湿法刻蚀工艺或干法刻蚀工艺对所述第一半导管芯进行刻蚀处理。

35.其中,在所述步骤(3)中,通过去除所述第一、第二、第三、第四键合部的一部分以分别形成多个所述第一、第二、第三、第四凸柱。

36.其中,在所述步骤(4)中,所述导电凸块的材质为铜、铝、钛、钯、银、镍、金中的一种或多种的组合,所述导电凸块通过电镀、化学镀、化学气相沉积或物理气相沉积工艺形成。

37.其中,在所述步骤(5)中,所述第五、第六、第七、第八键合部与所述第一、第二、第三、第四键合部分别一一对应。

38.其中,在所述步骤(7)中,所述环形导电块的材质为铜、铝、钛、钯、银、镍、金中的一种或多种的组合,所述环形导电块通过电镀、化学镀、化学气相沉积或物理气相沉积工艺形成。

39.其中,在所述步骤(8)中,先在所述第一、第二、第三、第四沟槽中设置黏附材料,进而利用所述黏附材料分别粘结所述第一、第二、第三、第四凸柱,在所述环形导电块中设置导电钎料,进而利用所述导电钎料粘结所述导电凸块。

40.本发明还提出一种键合封装体,其采用上述制备方法制备形成的。

41.如图1~图10所示,本实施例提供一种键合封装体的制备方法,该制备方法包括以下步骤:如图1所示,在步骤(1)中,提供第一半导体管芯100,所述第一半导体管芯100中具有硅通孔101。

42.如图2所示,在步骤(2)中:将所述第一半导体管芯100设置于第一基板102上,接着对所述第一半导管芯100进行刻蚀处理,以在所述第一半导体管芯100的四周分别形成第一键合部103、第二键合部104、第三键合部105、第四键合部106,所述第一、第二、第三、第四键合部103

‑

106分别突出于所述第一半导体管芯100的第一、第二、第三、第四侧表面。

43.在具体的实施例中,在所述步骤(2)中,将所述第一半导体管芯100设置于所述第一基板102上之前,在所述第一基板102上设置粘结层(未图示),进而利用所述粘结层粘结所述第一半导体管芯100,通过湿法刻蚀工艺或干法刻蚀工艺对所述第一半导管芯100进行刻蚀处理。

44.在具体的实施例中,所述第一、第二、第三、第四键合部103

‑

106的尺寸相同,进而利用掩膜对所述第一半导体管芯100进行湿法刻蚀以同时形成所述第一、第二、第三、第四键合部103

‑

106。

45.如图3所示,在步骤(3)中:接着对所述第一半导体管芯100的上表面进行刻蚀处理,以在所述第一半导体管芯100中形成第一凹槽107,所述第一凹槽107露出所述硅通孔101,并在所述第一键合部103上形成多个第一凸柱1031,在所述第二键合部104上分别形成多个第二凸柱1041,在所述第三键合部105上形成多个第三凸柱1051,在所述第四键合部106上分别形成多个第四凸柱1061。

46.在具体的实施例中,在所述步骤(3)中,通过去除所述第一、第二、第三、第四键合部103

‑

106的一部分以分别形成多个所述第一、第二、第三、第四凸柱1031

‑

1061。

47.在具体的实施例中,通过湿法刻蚀或干法刻蚀以分别形成所述第一凹槽107和所述第一、第二、第三、第四凸柱1031

‑

1061,所述第一、第二、第三、第四凸柱为圆柱或方柱,更具体的,所述第一、第二、第三、第四凸柱的直径或边长均为500

‑

5000纳米,相邻所述第一凸柱、第二凸柱、第三凸柱或者第四凸柱之间的间距均为1000

‑

6000纳米,所述第一、第二、第三、第四凸柱的高度为2

‑

8微米。

48.如图4所示,在步骤(4)中:接着在第一凹槽107中暴露的所述硅通孔101上形成导电凸块108。

49.在具体的实施例中,在所述步骤(4)中,所述导电凸块108的材质为铜、铝、钛、钯、银、镍、金中的一种或多种的组合,所述导电凸块108通过电镀、化学镀、化学气相沉积或物理气相沉积工艺形成。

50.在更具体的实施例中,通过电镀铜工艺形成导电铜柱。

51.如图5所示,在步骤(5)中:提供第二半导体管芯200,所述第二半导体管芯200的上表面具有导电焊盘201,将所述第二半导体管芯200设置于第二基板202上,接着对所述第二半导管芯200进行刻蚀处理,以在所述第二半导体管芯200的四周分别形成第五键合部203、第六键合部204、第七键合部205、第八键合部206,所述第五、第六、第七、第八键合部203

‑

206分别突出于所述第二半导体管芯200的第一、第二、第三、第四侧表面。

52.在具体的实施例中,在所述步骤(5)中,所述第五、第六、第七、第八键合部203

‑

206与所述第一、第二、第三、第四键合部103

‑

106分别一一对应。

53.在具体的实施例中,在所述步骤(5)中,将所述第二半导体管芯200设置于所述第二基板202上之前,在所述第二基板202上设置粘结层(未图示),进而利用所述粘结层粘结所述第二半导体管芯200,通过湿法刻蚀工艺或干法刻蚀工艺对所述第二半导管芯200进行刻蚀处理。

54.在具体的实施例中,利用掩膜对所述第二半导体管芯200进行湿法刻蚀以同时形成所述第一、第二、第三、第四键合部203

‑

206。

55.如图6所示,在步骤(6)中:接着对所述第二半导体管芯200的上表面进行刻蚀处理,以在所述第五、第六、第七、第八键合部203

‑

206上分别形成第一沟槽2031、第二沟槽2041、第三沟槽2051、第四沟槽2061。

56.在具体的实施例中,通过湿法刻蚀或者干法刻蚀分别形成所述第一沟槽2031、第二沟槽2041、第三沟槽2051、第四沟槽2061。

57.如图7所示,在步骤(7)中:接着在所述第二半导体管芯200的所述导电焊盘201上形成环形导电块207。

58.在具体的实施例中,在所述步骤(7)中,所述环形导电块207的材质为铜、铝、钛、钯、银、镍、金中的一种或多种的组合,所述环形导电块207通过电镀、化学镀、化学气相沉积或物理气相沉积工艺形成。

59.在更具体的实施例中,通过电镀铜工艺形成环形导电铜块。

60.如图8所示,在步骤(8)中:接着将第二半导体管芯200键合至所述第一半导体管芯100,使得多个所述第一凸柱1031嵌入到所述第一沟槽2031中,多个所述第二凸柱1041嵌入

到所述第二沟槽2041中,多个所述第三凸柱1051嵌入到所述第三沟槽2051中,多个所述第四凸柱1061嵌入到所述第四沟槽2061中,并使得所述导电凸块108嵌入到所述环形导电块207中,进而将所述导电焊盘201电连接至所述硅通孔101。

61.在具体的实施例中,在所述步骤(8)中,先在所述第一、第二、第三、第四沟槽2031

‑

2061中设置黏附材料,进而利用所述黏附材料分别粘结所述第一、第二、第三、第四凸柱1031

‑

1061,在所述环形导电块207中设置导电钎料,进而利用所述导电钎料粘结所述导电凸块108。

62.如图9所示,在步骤(9)中:接着去除所述第二基板202,然后形成塑封层300以包裹所述第一、第二半导体管芯100和200,接着去除所述第一基板102。

63.在具体的实施例中,所述塑封层300可以为环氧树脂。

64.如图10所示,在步骤(10)中:接着在所述塑封层300上形成重布线层400,并在所述重布线层400上形成导电焊球500。

65.在具体的实施例中,所述第一半导体管芯100直接接触所述重布线层400。

66.如图10所示,本发明还提出一种键合封装体,其采用上述制备方法制备形成的。

67.相较于现有技术,本发明的键合封装体及其制备方法有如下的有益效果:通过在所述第一半导体管芯的四周分别形成第一、第二、第三、第四键合部,并在所述第一半导体管芯中形成第一凹槽,所述第一凹槽露出硅通孔,并在所述第一键合部上形成多个第一凸柱,在所述第二键合部上分别形成多个第二凸柱,在所述第三键合部上形成多个第三凸柱,在所述第四键合部上分别形成多个第四凸柱,接着第一凹槽中暴露的所述硅通孔上形成导电凸块。进而通过在所述第二半导体管芯的四周分别形成第五、第六、第七、第八键合部,并在所述第五、第六、第七、第八键合部上分别形成第一、第二、第三、第四沟槽,在所述第二半导体管芯的所述导电焊盘上形成环形导电块,接着将第二半导体管芯键合至所述第一半导体管芯,使得多个所述第一凸柱嵌入到所述第一沟槽中,多个所述第二凸柱嵌入到所述第二沟槽中,多个所述第三凸柱嵌入到所述第三沟槽中,多个所述第四凸柱嵌入到所述第四沟槽中,并使得所述导电凸块嵌入到所述环形导电块中,进而将所述导电焊盘电连接至所述硅通孔。上述结构的设置,通过第一凹槽的设置为硅通孔与另一半导体管芯的电连接提供接合空间,且第一半导体管芯的四周边缘的形成第一、第二、第三、第四键合部以及第二半导体管芯的四周边缘的形成第五、第六、第七、第八键合部,进而可以提高第一、第二半导体管芯的键合强度,有效防止其剥离倒塌,且为硅通孔的电连接提供安装空间,进而可以提高电连接的稳定性。

68.上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,举凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1