半导体结构的制作方法

1.本发明半导体技术领域,尤其涉及一种半导体结构。

背景技术:

2.由于高性能集成电路需要在较高频率下以较低电源电压提供较大电流,因此电源系统的设计日益成为一项挑战。可以采用去耦电容器作为临时电荷储存器,以防止电源电压的瞬时波动。去耦电容器对于降低数字电路(例如微处理器)中的电源噪声越来越重要,该数字电路包括许多在开和关状态之间交替的晶体管。

3.尽管现有的半导体结构通常是足够的,但是它们在各个方面都不是令人满意的。例如,因为必须将多个电容器用于不同的电源域(power domain),集成去耦电容器具有挑战性。例如,中央处理单元(central processing unit,cpu)可能需要一个去耦电容器,而高性能系统单芯片(system-on-chip,soc)晶粒可能需要5到10个去耦电容器。因此,需要进一步改进半导体结构以提供设计灵活性。

技术实现要素:

4.有鉴于此,本发明提供一种半导体结构,以解决上述问题。

5.根据本发明的第一方面,公开一种半导体结构,包括:

6.第一基板,包括布线结构;

7.第一半导体晶粒和第二半导体晶粒,设置在该第一基板上;以及多端子多电容结构,设置于该第一基板上,该多端子多电容结构包括:

8.第二基板;绝缘层,设置于该第二基板上方;第一多端子电容器,设置在该绝缘层上方并通过该布线结构电耦接到该第一半导体晶粒;以及第二多端子电容器,设置在该绝缘层上方并通过该布线结构电耦接到该第二半导体晶粒,其中该第一多端子电容器和该第二多端子电容器与该第二基板电隔离。

9.根据本发明的第二方面,公开一种半导体结构,包括:

10.多端子多电容结构,包括:绝缘层;第一多端子电容器,设置在该绝缘层上并包括第一正极端子和第一接地端子;以及第二多端子电容器,设置在该绝缘层上并包括第二正极端子和第二接地端子,其中该第二多端子电容器与该第一多端子电容器电隔离;以及

11.封装结构,设置在该多端子多电容器结构之上,包括:第一半导体晶粒,电耦接到该第一多端子电容器;以及第二半导体晶粒,电耦接到该第二多端子电容器。

12.本发明的半导体结构由于包括:第一基板,包括布线结构;第一半导体晶粒和第二半导体晶粒,设置在该第一基板上;以及多端子多电容结构,设置于该第一基板上,该多端子多电容结构包括:第二基板;绝缘层,设置于该第二基板上方;第一多端子电容器,设置在该绝缘层上方并通过该布线结构电耦接到该第一半导体晶粒;以及第二多端子电容器,设置在该绝缘层上方并通过该布线结构电耦接到该第二半导体晶粒,其中该第一多端子电容器和该第二多端子电容器与该第二基板电隔离。与针对不同半导体的不同电压域使用单独

的电容器相比,本发明采用包括多个电容器和多个端子的多端子多电容结构。端子包括正极端子和接地端子。因此,本发明可以减少电容器所占用的空间,并且可以增加基板上保留的导电结构。因此,本发明可以增加设计灵活性,并且可以更容易地设计。本发明还可以提供半导体封装性能的提升。

附图说明

13.图1是根据一些实施例的示例性半导体结构的俯视图;

14.图2是根据一些实施例的示例性半导体结构的俯视图;

15.图3是根据一些实施例的示例性半导体结构的截面图;

16.图4a和4b是根据一些实施例的示例性半导体结构的多端子多电容结构的俯视图;

17.图5a、5b和5c是根据一些实施例的示例性半导体结构的多端子多电容结构的概念图;

18.图6是根据一些实施例的示例性半导体结构的多端子多电容结构的截面图。

具体实施方式

19.以下公开提供了用于实现所提供的主题的不同特征的许多不同的实施例或示例。下面描述组件和布置的特定示例以简化本发明。当然,这些仅是示例,而无意于进行限制。例如,在下面的描述中,在第二特征之上或之上的第一特征的形成可以包括其中第一特征和第二特征形成为直接接触实施例,并且还可以包括其中在第一特征和第二特征之间形成附加特征的实施例,使得第一和第二特征可以不直接接触。另外,本发明可以在各个示例中重复参考数字和/或字母。该重复是出于简单和清楚的目的,并且其本身并不指示所讨论的各种实施例和/或配置之间的关系。

20.另外,在本发明的一些实施例中,关于附接,联接等的术语,诸如“连接”和“互连”,是指一种关系,其中结构通过彼此直接或间接地固定或彼此附接。除非另有明确说明,否则中间结构以及可移动的或刚性的附件或关系。另外,术语“耦接”包括直接和间接电连接的任何方法。

21.此外,为了便于描述,本文中可以使用诸如“在...下方”、“在...之下”、“在...下”、“在...上方”、“在...之上”之类的空间相对术语,以便于描述一个元件或特征与之的关系。如图所示的另一元件或特征。除了在图中描述的方位之外,空间相对术语还意图涵盖设备在使用或操作中的不同方位。该装置可以以其他方式定向(旋转90度或以其他定向),并且在此使用的空间相对描述语可以同样地被相应地解释。

22.术语“大约”、“大致”和“约”通常表示规定值的

±

20%、或所述规定值的

±

10%、或所述规定值的

±

5%、或所述规定值的

±

3%、或规定值的

±

2%、或规定值的

±

1%、或规定值的

±

0.5%的范围内。本发明的规定值是近似值。当没有具体描述时,所述规定值包括“大约”、“大致”和“约”的含义。本文所使用的术语仅出于描述特定实施例的目的,并不旨在限制本发明。如本文所使用的,单数术语“一”,“一个”和“该”也旨在包括复数形式,除非上下文另外明确指出。

23.下面描述本发明的一些实施例。可以在这些实施例中描述的阶段之前,之中和/或之后提供附加的操作。对于不同的实施例,可以替换或消除所描述的某些阶段。可以将附加

特征添加到半导体装置结构中。对于不同的实施例,下面描述的一些特征可以被替换或消除。尽管以以特定顺序执行的操作讨论了一些实施例,但是可以以另一逻辑顺序执行这些操作。

24.根据本发明的一些实施例描述了一种半导体结构。该半导体结构包括多端子(multi-terminal)多电容(multi-capacitor)结构,其具有多于一个的端子以及多于一个的电容,以减少占用面积,提升设计弹性。

25.图1是根据本发明的一些实施例的半导体结构100的俯视图。可以向半导体结构100添加附加特征。对于不同的实施例,可以替换或消除下面描述的一些特征。为了简化该图,仅示出了半导体结构100的一部分。

26.如图1所示,根据一些实施例,半导体结构100包括基板102。基板102内部可以存在布线结构。在一些实施例中,基板102中的布线结构包括导电层、导电过孔、导电柱等,或者它们的组合。基板102中的布线结构可由金属形成,例如铜、铝或其组合。

27.基板102中的布线结构可以设置在金属间介电(inter-metal dielectric,imd)层中。在一些实施例中,imd层由有机材料如聚合物基材、非有机材料如氮化硅、氧化硅、氮氧化硅或其组合形成。基板102可具有第一表面和与第一表面相对的第二表面。需要说明的是,图中所示的基板102的配置仅为示例性的,并不用于限制本发明。可以在基板102中和基板102上形成任何期望的半导体元件。然而,为了简化图示,仅示出了平坦的基板102。

28.如图1所示,根据一些实施例,半导体结构100包括多个导电结构104。导电结构104可以设置在基板102的第一表面上并且可以电耦接到基板102的布线结构。在一些实施例中,导电结构104包括导电材料,例如金属。导电结构104可以是微凸块、受控塌陷芯片连接(controlled collapse chip connection,c4)凸块、球栅阵列(ball grid array,bga)球等或其组合。

29.根据一些实施例,半导体结构100包括第一半导体晶粒106和第二半导体晶粒108。第一半导体晶粒106和第二半导体晶粒108可以设置在基板102的第二表面上,并且仅出于说明目的而示出。例如,导电结构104设置在基板102的第一表面上,其中第一半导体晶粒106、第二半导体晶粒108以及多端子多电容结构110设置在在与基板102的第二表面之上。

30.第一半导体晶粒106和第二半导体晶粒108可以电耦接到基板102的布线结构。

31.根据一些实施例,第一半导体晶粒106和第二半导体晶粒108各自独立地包括系统单芯片(soc)晶粒、逻辑器件、存储器器件、射频(radio frequency,rf)器件等,或它们的组合。例如,第一半导体晶粒106和第二半导体晶粒108可以各自独立地包括微控制单元(micro control unit,mcu)晶粒、微处理器单元(microprocessor unit,mpu)晶粒、电源管理集成电路(power management integrated circuit,pmic)晶粒、全球定位系统(global positioning system,gps)设备、中央处理单元(central processing unit,cpu)芯片、图形处理单元(graphics processing unit,gpu)芯片、输入输出(input-output,io)芯片、动态随机存取存储器(dynamic random access memorydram)控制器、静态随机存取存储器(static random-access memory,sram)、高带宽存储器(high bandwidth memory,hbm)或其组合。

32.根据一些实施例,半导体结构100包括设置在基板102的第二表面上的第一电容器106c和第二电容器108c。第一电容器106c可以通过基板102的布线结构电耦接到第一半导

体晶粒106,并且第二电容器108c可以通过基板102的布线结构电耦接到第二半导体晶粒108。可以提供第一电容器106c和第二电容器108c以减少系统电流电阻(current-resistance,ir)降。

33.第一电容器106c和第二电容器108c各自占据空间。如图1所示,第一电容106c与第二电容108c例如分别占据六片(六个)导电结构104的面积。随着对更多功能和更小设备的需求不断增加,为不同的半导体组件集成不同的电容器具有挑战性。因此,本发明提供另一实施例以解决上述问题。

34.图2是根据本发明的一些其他实施例的半导体结构200的俯视图。需要说明的是,半导体结构200可以包括与图1所示的半导体结构100相同或相似的部件,为了简单起见,不再详细讨论这些部件。与图1的实施例中半导体结构100包括多个电容相比,以下实施例将这些电容替换为多端子多电容结构,以减少占用空间。

35.如图2所示,根据一些实施例,半导体结构200包括多端子多电容结构(或多端口多电容器结构)110。多端子多电容结构110例如可以占据六片(六个)导电结构104的面积。也就是说,不同的电源域可以共享一个多端子多电容结构110。因此,无需为每个不同的电压设计使用单独的电容器。因此,可以减少占用面积,可以保留更多的导电结构104,并且可以提供设计灵活性。

36.多端子多电容结构110可以包括并排布置的用于第一半导体晶粒106的电容器和用于第二半导体晶粒108的电容器。第一半导体晶粒106和第二半导体晶粒108也可以并排布置。第一半导体晶粒106的侧壁可以与第二半导体晶粒108的侧壁对齐。然而,本发明不限于此。例如,第一半导体晶粒106和第二半导体晶粒108可以垂直堆叠。

37.在一些实施例中,如图2所示,多端子多电容结构110在与基板102的第一表面基本上垂直的方向上与第一半导体晶粒106和第二半导体晶粒108部分地重叠。或者,多端子多电容结构110可以在基本上垂直于基板102的第一表面的方向上与第一半导体晶粒106或第二半导体晶粒108部分重叠。

38.如图2所示,多端子多电容结构110可以由导电结构104包围。在多端子多电容结构110的每一侧上,与多端子多电容结构110相邻的导电结构104的数量可以相同或不同。多端子多电容结构110和导电结构104的数量和配置仅出于说明的目的而示出。

39.如图2所示,两个半导体晶粒,第一半导体晶粒106和第二半导体晶粒108共享一个多端子多电容结构110,但本发明不限于此。例如,多于两个半导体晶粒可以在与基板102的第一表面基本垂直的方向上共享多端子多电容结构110,以及在该方向上与多端子多电容结构110部分重叠。或者,多于一个多端子多电容结构可用于多个半导体晶粒。根据一些实施例,半导体结构200还包括一个或多个无源元件(未示出),例如电阻器、电容器、电感器或其组合。

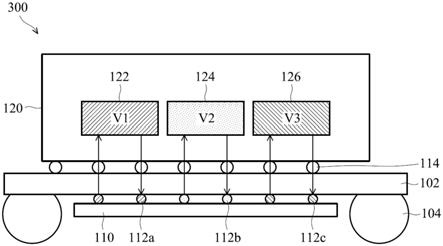

40.图3是根据本发明的一些实施例的半导体结构300的截面图。需要说明的是,半导体结构300可以包括与图2所示的半导体结构200相同或相似的元件,为简单起见,不再赘述。在以下实施例中,三个半导体晶粒共享多端子多电容结构。

41.如图3所示,根据一些实施例,半导体结构300包括第一半导体晶粒122、第二半导体晶粒124和第三半导体晶粒126,它们分别具有第一电压域vl、第二电压域v2和第三电压域v3。在一些实施例中,第一半导体晶粒122、第二半导体晶粒124和第三半导体晶粒126可

以包括在封装结构(或称为半导体封装、半导体封装结构)120中。在一些其他实施例中,第一半导体晶粒122、第二半导体晶粒124和第三半导体晶粒126可以包括在封装结构120中。第三半导体晶粒126可以是分开的,例如不在封装结构120中。

42.第一半导体晶粒122、第二半导体晶粒124和第三半导体晶粒126可以包括相似或不同的部件。第一半导体晶粒122、第二半导体晶粒124和第三半导体晶粒126可以类似于图2所示的第一半导体晶粒106和/或第二半导体晶粒108,在此不再赘述。根据一些实施例,封装结构120还包括一个或多个无源元件(未示出),例如电阻器、电容器、电感器或其组合。

43.如图3所示,根据一些实施例,半导体结构300包括在封装结构120和基板102之间的多个导电结构114。第一半导体晶粒122、第二半导体晶粒124和第三半导体晶粒126可以通过导电结构114电耦接到基板102的布线结构。在一些实施例中,导电结构114包括导电材料,例如金属。导电结构114可以是微凸块、受控塌陷芯片连接(c4)凸块、球栅阵列(bga)球等或其组合。导电结构114可以类似于或不同于导电结构104。如图3所示的布置结构,半导体晶粒与多端子多电容结构分别在基板102的两个相对的表面,并且导电结构104在多端子多电容结构的外围,可以节省面积占用,有利于半导体封装的尺寸小型化。

44.如图3所示,根据一些实施例,半导体结构300包括多端子多电容结构110。多端子多电容结构110可以包括用于第一半导体晶粒122、第二半导体晶粒124和第三半导体晶粒126的多个多端子电容器(未示出),可以分别称为第一多端子电容器、第二多端子电容和第三多端子电容。

45.在一些实施例中,第一多端子电容器、第二多端子电容器和第三多端子电容器分别包括第一端子112a、第二端子112b和第三端子112c。第一端子112a、第二端子112b和第三端子112c中的每一个都包括正极端子和接地端(接地端子),从而减小等效串联电阻(equivalent series resistor,sr)和等效串联电感(equivalent series inductance,sl)以减小系统ir压降。

46.第一半导体晶粒122可以通过第一端子112a、基板102的布线结构和导电结构114电耦接到第一多端子电容器。第二半导体晶粒124可以电耦接到通过第二端子112b、基板102的布线结构和导电结构114连接第二多端子电容器。第三半导体晶粒126可以通过第三端子112c、基板102的布线结构和导电结构114电耦接到第三多端子电容器。例如第一端子112a具有两个端子,分别为电容的两极的端子;第二端子112b和第三端子112c也是这样。具体来说,例如,第一半导体晶粒122可以通过两个第一端子112a、基板102的第一组布线结构和第一组导电结构114电耦接到第一多端子电容器。第二半导体晶粒124可以通过两个第二端子112n、基板102的第二组布线结构和第二组导电结构114电耦接到第二多端子电容器。第三半导体晶粒126可以通过两个第三端子112c、基板102的第三组布线结构和第三组导电结构114电耦接到第三多端子电容器。其中第一组布线结构、第二组布线结构、第三组布线结构相互之间是相互独立的,相互之间没有电性连接(例如电隔离);第一组导电结构、第二组导电结构、第三组导电结构相互之间是相互独立的,相互之间没有电性连接(例如电隔离)。这样每个半导体晶粒都是独立的连接到相互独立的多端子电容器(例如第一多端子电容器、第二多端子电容器等),相互之间独立工作。当然若有需求,各个多端子电容器之间也可以具有电性连接(例如两个多端子电容器连接到共同的电压端等等,可以通过布线结构之间的相互连接实现,或者导电结构114之间的相互连接实现,或者端子之间的相互连接实

现),这取决于具体需要,本发明在此并不做限制。在图3的实施例中,多端子多电容结构110具有三个电容器,分别与第一半导体晶粒122、第二半导体晶粒124、第三半导体晶粒126电连接,提供不同的电压域。多端子多电容结构110中的三个电容器相互之间可以没有电性连接,也可以各自均具有一个接到共同的接地的端子或接到相同电压的端子,三个电容器相互独立工作,集成在多端子多电容结构110。当然多端子多电容结构110可以具有更多数量的电容器,它们都可以独立工作,以满足不同的电容需求。此外本发明实施例中半导体晶粒的数量可以是4个、5个或更多,多端子多电容结构中的多端子电容器的数量可以是4个、5个或更多;其中半导体晶粒的数量与多端子电容器的数量无需相同,例如可以是半导体晶粒的数量更多,或者多端子电容器的数量更多。

47.如图3所示,根据一些实施例,多端子多电容结构110是连接盘侧电容器(land-side capacitor,lsc)。特别地,多端子多电容结构110和半导体晶粒122、124、126(或封装结构120)可以设置在基板102的相对侧上。多端子多电容结构110和导电结构104可以设置在基板102的同一侧上。半导体晶粒122、124、126(或封装结构120)可以部分地与多端子多电容结构110和导电结构104重叠。

48.或者,根据一些其他实施例,多端子多电容结构110可以是晶粒侧电容器(die-side capacitor,dsc)(未示出)。具体而言,多端子多电容结构110与半导体晶粒122、124、126(或封装结构120)可设置于基板102的同一侧。多端子多电容结构110及导电结构104可以设置在基板102的相对侧上。多端子多电容结构110可以与半导体晶粒122、124、126(或封装结构120)中的一个或多个相邻。半导体晶粒122、124、126(或封装结构120)和多端子多电容结构110可以部分地与导电结构104重叠。

49.如图3所示,第一半导体晶粒122、第二半导体晶粒124和第三半导体晶粒126布置成一排,其示出仅用于说明目的。例如,第一半导体晶粒122、第二半导体晶粒124和第三半导体晶粒126可以垂直堆叠。类似地,排列成一排的第一端子112a、第二端子112b和第三端子112c仅用于说明目的。下面描述一些示例性配置。

50.图4a是根据一些实施例的多端子多电容结构400a的俯视图。值得注意的是,多端子多电容结构400a可包括与图3所示的半导体结构300的多端子多电容结构110相同或相似的组件,并且为了为简单起见,将不再详细讨论这些组件。

51.在一些实施例中,第一端子112a包括第一正极端子vl和第一接地端子gndl,第二端子112b包括第二正极端子v2和第二接地端子gnd2,第三端子112c包括第三正极端子端子v3和第三接地端子gnd3。多端子多电容结构110还包括仅出于说明目的而示出的一些其他端子。端子112a、112b、112c中的相邻两个可以并排布置。包括端子112a、112b、112c的多端子电容器中的相邻两个也可以并排布置。

52.如图4a所示,第一正极端子vl、第二接地端子gnd2和第三正极端子v3可以沿着第一条线布置,并且第一接地端子gndl、第二正极端子v2和第三接地端子gnd3可以沿着第二条线布置。第一条线可以基本上平行于第二条线。图4a的实施例中,每个多端子电容器的两个电极连接到的位置均不同,以适应不同的需要。当然也可以是其中至少两个多端子电容器的两个电极中具有连接到相同电压端的方式,这取决于设计需求。

53.根据一些实施例,图5a中示出了多端子多电容结构400a的概念图。第一多端子电容器(包括第一正极v1和第一接地端gnd1)、第二多端子电容器(包括第二正极v2和第二接

地端gnd2)和第三多端子电容器(包括第三正极端子v3和第三接地端子gnd3)可以是分开的。特别地,第一多端子电容器、第二多端子电容器和第三多端子电容器可以彼此电隔离。

54.图4b是根据一些实施例的多端子多电容结构400b的俯视图。需要说明的是,多端子多电容结构400b可包括与图4b所示的多端子多电容结构400a相同或相似的组件,为简单起见,这些组件不再详细讨论。

55.在一些实施例中,第一正极端子、第二正极端子、第三正极端子和第四正极端子相等,可以称为v4。在一些实施例中,第一接地端、第二接地端、第三接地端和第四接地端相等,可称为gnd4。相邻的两个端子可以并排布置。包括这些端子的多端子电容器中的相邻两个也可以并排布置。

56.如图4b所示,第一正极端子、第二正极端子、第三正极端子和第四正极端子v4可以沿着第一条线布置,并且第一接地端子、第二接地端子、第三接地端子,第四接地端子gnd4可以沿着第二条线布置。第一条线可以基本上平行于第二条线。图4b的实施例中,多个多端子电容器的两个电极中一个均连接到同一个参考电压,而另一个电极均连接到另一个相同的参考电压。例如其中一个电极均连接到电压v4,另一个电极均连接到电压gnd4。当然也可以其中至少一个多端子电容器的两个电极与其他的多端子电容器的两个电极的连接方式不同(例如将图4a的实施例与图4b的实施例结合使用,或者部分结合使用),这取决于设计需求。图4a-4b示出了多端子多电容结构100中的每个电容器的两个电极(或端子)不同的连接示例,其中每个电容器的两个电极(或端子)还可以具有其他的连接方式,并不限于图4a-4b所示的方式。多端子多电容结构100中的每个电容器的两个电极(或端子)均可以根据不同的需要自由的进行电性连接。

57.根据一些实施例,在图5b中示出了多端子多电容结构400b的六个端子的概念图。第一正极端子、第二正极端子和第三正极端子v4可以彼此电耦接。第一接地端子、第二接地端子和第三接地端子gnd4可以彼此电耦接。即,第一多端子电容器、第二多端子电容器和第三多端子电容器可以彼此电耦接。

58.图5c是根据一些实施例的多端子多电容结构的概念图。在一些实施例中,第一端子包括第一正极端子v1和第一接地端子,第二端子包括第二正极端子v2和第二接地端子,第三端子包括第三正极端子v3和第三接地端子。第一接地端子、第二接地端子和第三接地端子可以电耦接到公共接地端gnd5。图5a-5c示出了多端子多电容结构100中的每个电容器的两个电极(或端子)不同的连接示例,,其中每个电容器的两个电极(或端子)还可以具有其他的连接方式,并不限于图5a-5c所示的方式。多端子多电容结构100中的每个电容器的两个电极(或端子)均可以根据不同的需要自由的进行电性连接。图5a-5c所示的三个电容器之间,每个电容器的两个电极之间均没有电性连接,因此每个电容器之间是独立工作的。

59.图6是根据一些实施例的半导体结构的多端子多电容结构600的截面图。需要说明的是,多端子多电容结构600可以包括与图3所示的多端子多电容结构110相同或相似的组件,为了简单起见,这些组件不再详细讨论。

60.如图6所示,根据一些实施例,多端子多电容结构600包括半导体基板(基板)602。半导体基板602可以由硅、硅锗、锗、其他合适的半导体或其组合形成。需要说明的是,图中所示的半导体基板602的配置仅为示例性的,并不用于限制本发明。可以在半导体基板602之中和之上形成任何期望的半导体元件。然而,为了简化图示,仅示出了平坦的半导体基板

602。

61.如图6所示,根据一些实施例,多端子多电容结构600包括设置在半导体基板602上方的绝缘层604。绝缘层604可以覆盖半导体基板602的顶面。绝缘层604可以由氧化硅、氮化硅、氮氧化硅、其他合适的隔离材料或其组合形成。

62.如图6所示,多端子多电容结构600包括设置在绝缘层604上方的第一多端子电容器610a和第二多端子电容器610b。绝缘层604可以电隔离第一多端子电容器610a和第二多端子电容器610b。多端子电容器610a和第二多端子电容器610b从基板102分离。因此,可以将多个多端子电容器分组以形成一个电容器(即,多端子多电容结构600),其为不同的电压域提供去耦电容功能,从而减少电容的占用空间。此外,可以提高设计灵活性,还可以提供性能提升。

63.如图6所示,根据一些实施例,第一多端子电容器610a和第二多端子电容器610b中的每一个都包括导电层606、608、616。导电层606、608、616可以由金属形成,例如钨。根据一些实施例,第一多端子电容器610a和第二多端子电容器610b中的每一个包括导电层606和608之间的电容器单元612,并且包括导电层606和616之间以及导电层608和616之间的多个通孔614。通孔614可以由金属形成,例如铜。本发明中电容器单元612的组成方式具体如下,其中导电层606和608可以是电容器单元的两个电极,而导电层606和608之间具有绝缘层630(例如可以是高k(high-k)材料)。导电层606、608可以包括钨或其他金属等,导电层606和608之间还具有导电材料631(例如多晶硅等)和导电材料632(例如多晶硅等)。其中导电层608与导电材料631电性连接,导电层606与导电材料632电性连接,绝缘层630围绕导电材料631和导电材料632,并且绝缘层630将导电材料631与导电层606间隔开,绝缘层630还将导电材料632与导电层608间隔开,从而形成电容器单元。本发明中第一多端子电容器610a和第二多端子电容器610b每个中均可以具有多个电容器或电容器单元,图6中所示仅为示例,并非对本发明的限制(例如数量等限制)。此外本发明多端子多电容结构600除了第一多端子电容器610a和第二多端子电容器610b之外,还可以具有更多的多端子电容器,图6中所示仅为示例,并非对本发明的限制(例如数量等限制)。

64.如图6所示,根据一些实施例,多端子多电容结构600包括设置在绝缘层604上方并围绕第一多端子电容器610a和第二多端子电容器610b的介电层618。介电层618可由有机材料(例如聚合物基材)、非有机材料(例如氮化硅、氧化硅、氮氧化硅)或其组合形成。

65.如图6所示,根据一些实施例,多端子多电容结构600包括设置在导电层616上方的多个端子620。端子620可以被介电层618暴露。端子620可以由诸如金属的导电材料形成。

66.第一多端子电容器610a的端子620可以包括正极端子子和接地端子并且可以电耦接到半导体晶粒(例如图3中所示的第一半导体晶粒122)。第二多端子电容器610b的端子620可以包括正极端子子和接地端子并且可以电耦接到另一个半导体晶粒(例如图3中所示的第二半导体晶粒124)。每个多端子电容器(例如第一多端子电容器610a)的两个端子620可以分别是电容的两个电极。多端子多电容结构600中的多端子电容器(例如第一多端子电容器610a、第一多端子电容器610b等等)可以并排设置或阵列设置等等,以实现多端子多电容结构中多个电容的集成,满足不同的应用需求。

67.综上所述,与针对不同半导体的不同电压域使用单独的电容器相比,本发明采用包括多个电容器和多个端子的多端子多电容结构。端子包括正极端子和接地端子。因此,本

发明可以减少电容器所占用的空间,并且可以增加基板上保留的导电结构(例如导电结构104)。因此,本发明可以增加设计灵活性,并且可以更容易地设计。本发明还可以提供半导体封装性能的提升。此外,本发明可以减小等效串联电阻(esr)和等效串联电感(esl),从而降低系统ir压降。

68.本领域的技术人员将容易地观察到,在保持本发明教导的同时,可以做出许多该装置和方法的修改和改变。因此,上述公开内容应被解释为仅由所附权利要求书的界限和范围所限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1