一种基于钛酸镧的铁电忆阻器件及其制备方法

1.本发明属于铁电存储技术领域,涉及一种基于钛酸镧的铁电忆阻器件及其制备方法。

背景技术:

2.忆阻器是一个与磁通量和电荷量相关的无源电路元件。早在1971年,蔡少棠教授便从理论上预言了忆阻器的存在,直到2008年,惠普实验室首次制备了忆阻器器件,证实了蔡少棠教授有关忆阻器的学说。忆阻器具有非线性电学性质,并兼具结构简单、易于集成、速度快、功耗低、能与cmos电路兼容等优势。

3.现如今,忆阻器已经发展为具有纳秒级的开关速度,较低的能耗和较长的写入/擦除耐力。由于在许多复杂的学习中人脑消耗的能量(约20w)要比最先进的计算机消耗的能量(约1mw)小得多,忆阻器用来模拟生物大脑中神经形态的计算可能会对下一代人工智能产生深远影响。

4.铁电忆阻器作为忆阻器家族的新成员,相比于传统的氧化物忆阻器,具有更高的开关比,更稳定的阈值电压以及更快的读写速度等其他的优点。

5.但是铁电忆阻器作为类脑神经计算的新硬件实现方法,其模拟生物突触功能的性质还亟待研究。同时,铁电忆阻器的本身性能比较依赖沉积的铁电薄膜的性质,所以探寻新的材料以及其适合的生长方法来提高铁电忆阻器的器件性能也非常重要。

技术实现要素:

6.针对现有技术的不足,本发明提供一种基于钛酸镧(la2ti2o7)的铁电忆阻器件及其制备方法。

7.在众多的铁电材料中,钛酸镧(la2ti2o7)中蕴含氧空位,钛酸镧在常温下可以用射频磁控溅射进行沉积,铁电性能稳定,在多值存储和类脑计算上有很大的潜力。

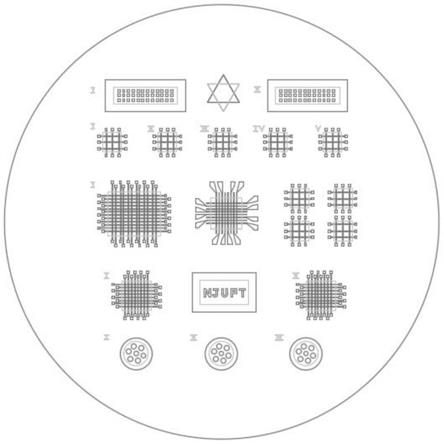

8.本发明采用的技术方案是:第一方面,提供一种基于钛酸镧的铁电忆阻器件,所述铁电忆阻器件设置在衬底上,所述铁电忆阻器件包括从下至上依次布设的底电极、阻变层和顶电极,所述底电极和顶电极的材质为tin,所述阻变层的材质为la2ti2o7;所述阻变层的底面与所述底电极的顶面相接触,所述阻变层的顶面与所述顶电极的底面相接触,所述铁电忆阻器件集成有1个区域的njupt字样的单一器件、2个区域的长方形单一器件、3个区域的圆形单一器件、9个3

×

3忆阻器阵列、3个8

×

8忆阻器阵列、1个12

×

12忆阻器阵列。

9.在一些实施例中,所述底电极、顶电极的厚度为100nm,阻变层的厚度为20nm。

10.在一些实施例中,所述底电极、阻变层和顶电极相互平行。

11.进一步地,在一些实施例中,在njupt字样的单一器件、长方形单一器件、圆形单一器件中,底电极、阻变层、顶电极竖直方向同中心轴设置。

12.在一些实施例中,在njupt字样的单一器件、长方形单一器件、圆形单一器件中,所

述底电极面积大于阻变层的面积。

13.进一步地,所述8

×

8忆阻器阵列包括一个第一8

×

8忆阻器阵列和两个第二8

×

8忆阻器阵列;其中第一8

×

8忆阻器阵列位于中心位置,第一8

×

8忆阻器阵列的尺寸为60um。

14.在一些实施例中,3

×

3忆阻器阵列、8

×

8忆阻器阵列、12

×

12忆阻器阵列的底电极与顶电极水平方向上相互垂直设置。

15.第二方面,提供一种基于钛酸镧的铁电忆阻器件的制备方法,所述方法包括:s1:在衬底上覆盖第一掩膜版,真空环境下,通过物理气相沉积一层tin作为底电极;s2:取下第一掩膜版,通过对准标记覆盖第二掩膜版,真空环境下,在底电极上氧化生长一层la2ti2o7作为阻变层;s3:取下第二掩膜版,通过对准标记覆盖第三掩膜版,真空环境下,在阻变层上通过物理气相沉积一层tin作为顶电极。

16.在一些实施例中,所述衬底采用硅片。

17.在一些实施例中,所述底电极、顶电极的厚度为100nm,阻变层的厚度为20nm。

18.与现有技术相比,本发明所述的技术方案,具有如下优点:1.本发明设计了新型的掩模版,将单一忆阻器件和忆阻器阵列集成在一个硅片衬底上,其次设计了尺寸更加小的忆阻器这阵列,拓宽了忆阻器件的应用场景。最后设计了njupt字样的忆阻单一器件,使得该忆阻器件更具代表意义。

19.2.本发明提供一种基于钛酸镧的铁电忆阻器件,阻变层为钛酸镧(la2ti2o7)。本发明制得的铁电忆阻器,具有良好的开关特性和稳定性,可用于多值存储,模拟人脑的神经元,具有旷阔的前景。

20.3.本发明提供的制备方法,能够用于制备基于钛酸镧(la2ti2o7)的铁电忆阻器件,该制备方法简单、高效,成本也低,适合在产业上推广使用。

附图说明

21.图1为本发明实施例的基于钛酸镧的铁电忆阻器件的整体图;图2为本发明实施例绘制的用于沉积底电极的第一掩膜版图;图3为本发明实施例绘制的用于沉积阻变层的第二掩膜版图;图4为本发明实施例绘制的用于沉积顶电极的第三掩膜版图;图5为本发明实施例中3

×

3铁电忆阻器阵列的制备及测试总框架图;图6为本发明实施例中的长方形单一铁电忆阻器件;图7为本发明实施例中的圆形单一铁电忆阻器件;图8为本发明实施例中njupt字样铁电忆阻器件的金相图;图9为本发明实施例中60um尺寸的8

×

8忆阻器阵列金相图;图10为本发明实施例铁电忆阻器阵列在双向直流扫描下得到的典型i-v曲线图;图11为本发明实施例铁电忆阻器阵列的retention测试结果图。

具体实施方式

22.下面结合附图和实施例,对本发明的技术方案进行详细说明,但本发明的具体实

施,并不限于此。

23.实施例1如图1所示,一种基于钛酸镧的铁电忆阻器件,所述铁电忆阻器件设置在衬底上,所述铁电忆阻器件包括从下至上依次布设的底电极、阻变层和顶电极,所述底电极和顶电极的材质为tin,所述阻变层的材质为la2ti2o7;所述阻变层的底面与所述底电极的顶面相接触,所述阻变层的顶面与所述顶电极的底面相接触,所述铁电忆阻器件集成有1个区域的njupt字样的单一器件、2个区域的长方形单一器件、3个区域的圆形单一器件、9个3

×

3忆阻器阵列、3个8

×

8忆阻器阵列、1个12

×

12忆阻器阵列。

24.在一些实施例中,所述底电极、阻变层和顶电极相互平行。

25.进一步地,在一些实施例中,在njupt字样的单一器件、长方形单一器件、圆形单一器件中,底电极、阻变层、顶电极竖直方向同中心轴设置。

26.在一些实施例中,在njupt字样的单一器件、长方形单一器件、圆形单一器件中,所述底电极面积大于阻变层的面积。

27.在一些实施例中,所述底电极、顶电极的厚度为100nm,阻变层的厚度为20nm。

28.进一步地,所述的基于钛酸镧的铁电忆阻器件,所述8

×

8忆阻器阵列包括一个第一8

×

8忆阻器阵列和两个第二8

×

8忆阻器阵列;其中第一8

×

8忆阻器阵列位于中心位置,第一8

×

8忆阻器阵列的尺寸为60um。

29.在一些实施例中,3

×

3忆阻器阵列、8

×

8忆阻器阵列、12

×

12忆阻器阵列的底电极与顶电极水平方向上相互垂直设置。

30.实施例2一种基于钛酸镧的铁电忆阻器件的制备方法,该方法包括两个部分:1.设计新型掩模版,器件类型包括:1个区域的njupt字样的单一器件、2个区域的长方形单一器件、3个区域的圆形单一器件、9个3

×

3忆阻器阵列、3个8

×

8忆阻器阵列、1个12

×

12忆阻器阵列。

31.2.制备一种基于钛酸镧的铁电忆阻器件,包括以下步骤:s1:采用去离子水对硅片先进行清洗再用烘干机进行烘干,在烘干之后的硅片上覆盖第一掩膜版(如图2所示),通过pvd物理气相沉积,真空下沉积一层厚度为100nm的tin作为底电极;s2:取下第一掩膜版,通过对准标记覆盖第二掩膜版(如图3所示),真空下氧化生长一层厚度为20nm的la2ti2o7的阻变层;s3:取下第二掩膜版,通过对准标记覆盖第三掩膜版(如图4所示),真空下沉积一层厚度为100nmtin作为顶电极。

32.所述忆阻器件包括由下至上三层结构,其中阵列依次为底电极、钛酸镧(la2ti2o7) 阻变层、顶电极,单一铁电忆阻器件的底电极、阻变层和顶电极相互平行,且底电极、阻变层、顶电极竖直方向同中心轴设置。

33.单一铁电忆阻器件结构底电极面积大于阻变层的面积。

34.本发明的测试仪器为为keithley 4200-scs,忆阻器阵列的制备及测试总框图如图5所示。

35.图6为本发明实施例中的长方形单一铁电忆阻器件;图7为本发明实施例中的圆形

单一铁电忆阻器件;图8为本发明实施例中njupt字样铁电忆阻器件的金相图;图9为本发明实施例中60um尺寸的铁电忆阻器阵列金相图。

36.图10为实施例提供的一种基于钛酸镧(la2ti2o7)的铁电忆阻器阵列的循环伏安曲线图,其中,横坐标是电压,纵坐标是电流。电压扫描从0v到4v,在电压扫描还未到4v时,大概3v左右时,基于钛酸镧(la2ti2o7)的铁电忆阻器通过set过程,保持稳定的阻值,在电压从0v到-10v扫描的过程中发生rset过程,回到高阻态,并能够保持稳定的阻值。

37.图11是基于钛酸镧(la2ti2o7)的铁电忆阻器阵列在高阻态和低阻态下维持时间,当铁电忆阻器在一个较小的电压作用下时,基于钛酸镧(la2ti2o7)的铁电忆阻器的低阻态阻值(4

×

104ω)可以持续超过200秒,高阻态阻值(4

×

105ω)也可持续超过200秒,且持续时间可进一步延长。其中,横坐标为时间,纵坐标为阻值。由图11可知,本发明基于钛酸镧(la2ti2o7)的铁电忆阻器的阻态稳定,并具有多阻值切换的良好性能。

38.综上,本发明基于钛酸镧(la2ti2o7)的铁电忆阻器的具有良好的导电性和稳定性,可用于多值存储,模拟人脑的神经元,具有旷阔的前景。此外,本发明的制备方法简单、高效,成本也低,适合在产业上推广使用。

39.以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1