半导体发光器件的制作方法

1.本发明涉及半导体技术领域,特别涉及一种半导体发光器件。

背景技术:

2.发光二极管(简称led)是一种常用的发光器件,具有低电压、低功耗、体积小、寿命长等优点,广泛应用于照明和显示等领域。led作为新一代光源,被广泛应用在照明、显示、背光乃至光通信等领域。倒装芯片作为更高光效的产品已经越来越受到市场的青睐,倒装芯片制程结构较多,工艺制程复杂,因此对可靠性有了更高的要求和挑战。

3.现阶段倒装led高光效芯片第二电极层pn-metal 层设计图形面积较大,覆盖了第一绝缘层约80%左右的面积,如图1至3所示,由于第二电极层的反射率相对传统支架的反射率较低,第二电极层的面积较大会降低芯片反射率,从而影响芯片的整体亮度。

4.有鉴于此,特提出本发明。

技术实现要素:

5.发明目的:针对现有技术中存在的问题,本发明提供一种半导体发光器件,在保证第一p型电极和第二p型电极正常的电性连接的情况下,通过在第二p型电极临近n型半导体层外缘的外侧面上设置内凹部,以实现减小第二电极层的面积,提高芯片的反射率,从而提高芯片整体亮度。

6.技术方案:本发明提供了一种半导体发光器件,包括从下至上依次设置的衬底、具有pn台阶的外延层、第一电极层、第一绝缘层和第二电极层;所述第一电极层包括至少一个第一p型电极和至少一个第一n型电极;所述第二电极层包括至少一个第二p型电极和至少一个第二n型电极;所述第一p型电极通过所述第一绝缘层上开设的第一通孔与所述第二p型电极电性连接,所述第一n型电极通过所述第一绝缘层上开设的第二通孔与所述第二n型电极电性连接;所述第二p型电极具有连接其上下表面的、临近所述n型半导体层外缘的外侧面;所述外侧面上设置有至少一个用于减小所述第二电极层面积的内凹部;各所述内凹部的总面积占所述第二电极层面积的5~20%。

7.优选地,所述内凹部设置于相邻的两个第一p型电极之间。

8.优选地,所述内凹部的长度l1小于与其相邻的两个第一p型电极之间的最大间距l2。这样设计是为了达到在不影响第一p型电极与第二p型电极电性连接的前提下,尽量增大内凹部的长度,内缩第二电极层的面积,提高芯片的反射率,从而提高芯片整体亮度。

9.优选地,所述内凹部的宽度w大于或等于所述第一p电极的直径d。

10.优选地,若所述发光元件整体为四方形,则所述外侧面为四方形的外侧面;四方形的外侧面中,至少有一侧的外侧面上具有连续的所述内凹部;或者,四方形的外侧面中,至少有相对的两侧的外侧面上具有连续的所述内凹部;或者,四方形的外侧面中,四侧的外侧面上均具有连续的所述内凹部。内凹部的设置,即是将位于第二电极层边缘位置的至少一对相邻两个第二p型电极之间的第二电极层去除,以实现内缩减小第二电极层的面积,达到

提高芯片的反射率、提高芯片整体亮度的目的。

11.优选地,各所述连续的内凹部分别位于两两所述第一p型电极之间。在各相邻两个第一p型电极之间都设置内凹部,能够最大限度的将内凹部数量增加,以减小第二电极层面积,以最大限度的提高芯片的反射率、提高芯片整体亮度;理论上来说,内凹部设置的越多,减小第二电极层面积的力度就越大,提高芯片的反射率、提高芯片整体亮度的效果就越明显;但是在实际应用中,如果内凹部的面积过大,即第二电极层的面积减小过多,会影响第二p型电极与第一p型电极的电性连接效果,而内凹部的面积较小,则第二电极层的面积减小不明显,提高芯片的反射率、提高芯片整体亮度的效果不明显,所以本技术中控制内凹部的面积占第一绝缘层面积的5-15%之间,这样既能保证第二p型电极与第一p型电极的电性连接,又能达到减小内缩第二电极层面积的效果,实现提高芯片的反射率、提高芯片整体亮度的目的。

12.进一步地,所述的半导体发光器件还包括位于所述第二电极层上的焊盘电极层,所述焊盘电极层包括与所述第二p型电极电性连接的p焊盘电极以及与所述第二n型电极电性连接的n焊盘电极。

13.进一步地,所述的半导体发光器件还包括位于所述第二电极层与所述焊盘电极层之间的第二绝缘层,以将所述第二p型电极与所述第二n型电极绝缘;所述p焊盘电极通过所述第二绝缘层上开设的第三通孔与所述第二p型电极电性连接,所述n焊盘电极通过所述第二绝缘层上开设的第四通孔与所述第二n型电极电性连接。

14.进一步地,在所述第二绝缘层与所述焊盘电极层之间,还设置有支撑层和第三绝缘层,所述支撑层位于所述第二绝缘层与所述第三绝缘层之间,所述第三绝缘层位于所述支撑层与所述焊盘电极层之间。现有的发光元件结构,如图1所示,第二p型电极延伸至n焊盘电极下方,二者中间通过第二绝缘层相互隔离,形成如虚线方框所示的区域。当第二绝缘层因为某些原因导致断裂或出现裂痕,均可能导致第二p型电极和n焊盘电极连通,导致漏电的发生,使现有发光元件使用时的可靠性降低;本技术通过增加不与第二电极层和焊盘电极相连接的支撑层,以及与焊盘电极相隔离的第三绝缘层,从而起到了隔离第二电极和第三电极的绝缘作用,从而避免了因第二绝缘层断裂而导致的漏电现象,增加了发光元件的可靠性。支撑层优选为金属层或金属氧化物层或者dbr反射层,金属层包括cr、ni、ti、pt和au的金属单层或者几种金属单层组成的复合金属层。

15.进一步地,所述的半导体发光器件还包括位于所述外延层与所述第一电极层之间的电流阻挡层和电流扩展层,所述电流扩展层位于所述电流阻挡层之上。

16.有益效果:本技术在保证第一p型电极和第二p型电极正常的电性连接的情况下,通过在第二p型电极临近n型半导体层外缘的外侧面上设置内凹部,并限定各内凹部的面积之和占第二电极层面积的5~20%,以实现明显减小第二电极层的面积,提高芯片的反射率,从而提高芯片整体亮度。

附图说明

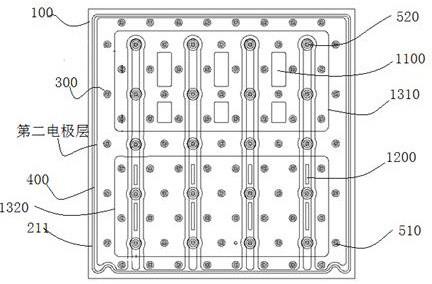

17.图1为现有技术中倒装发光元件的平面结构示意图;图2为现有技术中倒装发光元件的结构示意图;图3为现有技术中第二电极层的光罩图形平面图;

图4为实施方式1中的发光元件的平面结构示意图;图5为实施方式1中的发光元件的结构示意图;图6为实施方式1中第二电极层的光罩图形平面图;图7为实施方式1中发光元件的结构示意图;图8为实施方式2中的发光元件的平面结构示意图;图9为实施方式2中的发光元件的结构示意图;图10为实施方式3中的第二电极层的光罩图形平面图;附图标记:100-衬底;210-n型半导体层;211-pn台阶;220-多量子阱有源层;230-p型半导体层;300-电流阻挡层;400-电流扩展层;510-第一p型电极;511-第一通孔;520-第一n型电极;521-第二通孔;600-第一绝缘层;710-第二p型电极;720-第二n型电极;800-第二绝缘层;900-支撑层;1000-第三绝缘层;1100-第三通孔;1200-第四通孔;1310-p焊盘电极;1320-n焊盘电极;1410-内凹部;711-外侧面。 具体实施方式

18.下面结合附图对本发明进行详细的介绍。

19.实施方式1:本发明实施例所提供的一种发光元件,如图4和5所示,包括从下至上依次设置的衬底100、外延层、电流阻挡层300、电流扩展层400、第一电极层、第一绝缘层600、第二电极层、第二绝缘层800、焊盘电极层;第一电极层包括至少一个第一p型电极510和至少一个第一n型电极520;第二电极层包括至少一个第二p型电极710和至少一个第二n型电极720;焊盘电极层包括至少一个p型焊盘1310和至少一个n型焊盘1320。第二p型电极710具有连接其上下表面且临近n型半导体层210外缘的外侧面711。

20.如图6所示,本实施方式中,发光元件整体为四方形,则第二p型电极710的外侧面711为四方形的外侧面;为了减小反射率较低的第二电极层的面积,提高芯片的反射率,进而提高芯片的整体亮度,该第二p型电极710的四方形外侧面711中,一对相对两侧的外侧面711上具有连续的内凹部1410;各连续的内凹部1410分别位于两两第一p型电极510之间。即,去除第二p型电极710的外侧面711相邻两个第二p型电极710之间的第二电极层即形成了上述内凹部1410,各内凹部1410的面积之和占第二电极层面积的7.7%。

21.实际应用中,可以开设方形的内凹部1410,内凹部1410的长度l1小于与其相邻的两个第一p型电极510之间的最大间距l2;内凹部1410的宽度w大于或等于第一p型电极510的直径d(如图7)。这样设计是为了达到在不影响第一p型电极510与第二p型电极710电性连接的前提下,尽量增大内凹部1410的长度,内缩第二电极层的面积,提高芯片的反射率,从而提高芯片整体亮度。

22.本实施方式中发光元件的其他结构如常规发光元件所设置。具体如下:外延层设置于衬底100的表面,包括依次层叠设置于衬底100表面的n型半导体层

210、发光层220和p型半导体层230;还包括pn台阶211,pn台阶211的上台阶面为p型半导体层230,下台阶面为n型半导体层210,上台阶面和下台阶面之间连接形成pn台阶211的侧面;n型半导体层210,形成在衬底100上以覆盖衬底;p型半导体层230,形成以覆盖n型半导体层210上用于n电极区域之外的n型半导体层210上的区域,用于与n型半导体层210协同发光;电流阻挡层300和电流扩展层400依次设置于p型半导体层230的表面;第一电极层包括形成在p型半导体层230上的第一p型电极510和形成在n型半导体层210上的用于n电极区域的第一n型电极520;第一p型电极510与电流扩展层400相连接;第一n型电极520与pn台阶211的下台阶面相连接;第一p型电极510与第一n型电极520彼此隔离;第一绝缘层600覆盖第一n型电极520、电流扩展层400、pn台阶211的侧面、第一p型电极510、以及第一n型电极520与pn台阶211的侧面之间的下台阶面;第一绝缘层600用于将第一n电极与第一p电极绝缘,第一绝缘层600上设置有直通第一p型电极510的第一通孔511和直通第一n型电极520的第二通孔521;第二电极层包括第二p型电极710和第二n型电极720,第二p型电极710和第二n型电极720彼此绝缘隔离;第二p型电极710通过第一通孔511与第一p型电极510相连接;第二n型电极720通过第二通孔521与第一n型电极520相连接;第二绝缘层800设置于第二电极层表面;第三通孔1100和第四通孔1200贯穿第二绝缘层800分别直通第二p型电极710和第二n型电极720;焊盘电极层包括至p焊盘电极1310和n焊盘电极1320,p焊盘电极1310和n焊盘电极1320彼此隔离;p焊盘电极1310和第二p型电极710通过第三通孔1100电性连接,n焊盘电极1320和第二n型电极720通过第四通孔1200电性连接。

23.其中,衬底100可以包括但不限于蓝宝石衬底。此外,也可以选择图形化的衬底。

24.其中,n型半导体层210的材质可以为n型掺杂的氮化镓,p型半导体层230的材质可以为p型掺杂的氮化镓,但不仅限于这两种半导体类型。

25.其中,发光层220包括交替层叠设置的量子阱和量子垒,但是不限于此。发光层220包括但不限于红光发光层、黄光发光层、绿光发光层或蓝光发光层。量子阱包括但不限于ingan量子阱或alingan量子阱。

26.其中,电流阻挡层300包括但不限于sio2,电流阻挡层300的厚度一般为1500-5000a。。

27.其中,电流扩展层400占发光元件的面积的70%~90%,包括但不限于ito、zito、zio、gio、zto、fto、azo和gzo中的一种。电流扩展层400的厚度为100

ꢀå

~500

ꢀå

,例如可以为100

ꢀå

、150

ꢀå

、200

ꢀå

、300

ꢀå

、500

ꢀå

。电流扩展层400可以通过磁控溅射或蒸镀的方式进行沉积得到。

28.其中,第一通孔511和第二通孔521之间互相分离,无任何延伸交叉;如图5所示,第三通孔1100和第四通孔1200之间互相分离,无任何延伸交叉,从而保证上层电极和下层异质电极的分离,切断可能的漏电路径。

29.其中,第一绝缘层600为dbr反射层,dbr反射层可以为交替沉积sio2和ti3o5形成。第一绝缘层600的厚度为2μm~6μm,其中3.5μm~5.5μ最优。

30.其中,第二绝缘层800和/或第三绝缘层1000包括氧化硅、氮化硅和氮氧化硅中的

至少一种。第二绝缘层800和/或第三绝缘层1000的厚度为5k

å

~15k

å

,例如为6 k

å

、8 k

å

、13 k

å

、15k

å

。

31.其中,焊盘电极层中,p焊盘电极1310可以为1个、2个或者多个;n焊盘电极1320可以为1个、2个或者多个。焊盘电极的包括cr、ni、ti、pt和au中的金属单层、或者几种金属和/或合金的复合层。al的厚度为5k

å

~20k

å

,pt的厚度为0.5k

å

~3k

å

,ti的厚度为0.5~3k

å

,ni的厚度为3k

å

~12k

å

,au的厚度为1k

å

~5k

å

。焊盘电极为包括sn成分的bump电极,即p焊盘电极1310和n焊盘电极1320可以为凸点的bump电极,电极成分为sn。凸点电极可以采用印刷、电镀或蒸镀等方法制得。bump电极的高度≥5μm,锡膏高度≥20μm。

32.本发明实施例还提供了所述的发光元件的制备方法,具体包括以下步骤:s1、提供一衬底100,并在所述衬底100上依次沉积n型半导体层210、发光层220和p型半导体层230以形成外延层;s2、使用光刻胶形成mesa 图层的图案,以mesa 图层为掩模对外延层进行icp刻蚀,刻蚀深度10000-14000 a形成pn台阶211并去除光刻胶;s3、在外延层上沉积sio2,并通过光刻得到电流阻挡层300,去除光刻胶;电流阻挡层300位于p型半导体层230和电流扩展层400之间,起到协助电流扩展的作用,电流阻挡层300的厚度一般为1500-5000a。

33.s4、在外延层上沉积电流扩展层400,使用光刻胶进行电流扩展层400光刻,形成所需电流扩展层图层,以电流扩展层图层为掩模对电流扩展层400进行刻蚀,去除光刻胶漏出底层电流扩展层400,电流扩展层400的厚度在100-500a;s5、使用光刻胶先进行光刻,沉积制作第一电极层,第一电极层包括第一p型电极510和第一n型电极520,第一p型电极510是覆盖在电流阻挡层300和电流扩展层400叠加的膜层上,再去除光刻胶,第一电极层材料为cr ,ni,al ,ti,au和pt等一种金属或几种金属的组合,第一电极层的厚度可以为2-5μm;s6、沉积sio2及ti3o5交替组成的dbr布拉格反射层,即第一绝缘层600,第一绝缘层600厚度一般在2~6um,太薄会缺少反射效果,太厚会导致刻蚀时间过长,整个第一绝缘层600厚度在3-8μm;s7、使用光刻胶进行第一绝缘层600光刻,在光刻胶上形成第一绝缘层图形,然后进行icp刻蚀,在第一p型电极510和第一n型电极520上方光刻分别得到第一通孔511和第二通孔521;s8、然后沉积第二电极层后再去除光刻胶;其中,第二p型电极710通过第一通孔511与第一p型电极510相连通,第二n型电极720通过第二通孔521与第一n型电极520相连通;第二电极层在保证正常连接第一电极层的情况下面积尽可能的设计较小。第二电极层材料为cr ,ni,al ,ti,au和pt等一种金属或几种金属的组合,第二电极层的厚度可以为2-5μm。

34.s9、在第二p型电极710和第二n型电极720上覆盖第二绝缘层800。该第二绝缘层800利用pecvd沉积氧化硅或氮化硅或氮氧化硅等绝缘材料,第二绝缘层800厚度为5000-15000a。

35.s10、刻蚀得到贯穿第二绝缘层800的第三通孔1100和第四通孔1200;s11、通过黄光和沉积制备焊盘电极,形成p焊盘电极1310 和n焊盘电极1320;其

中,p焊盘电极1310通过第三通孔1100与所述第二p型电极710相连接,n焊盘电极1320通过第四通孔1200与所述第二n型电极720相连接;焊盘电极为cr,ni,al ,ti,au和pt等一种金属或几种金属的组合,p焊盘电极1310 和n焊盘电极1320的厚度可以为2-5μm。

36.实施方式2:本实施方式为实施方式1的进一步改进,主要改进之处在于,实施方式1中,第二p型电极710延伸至n焊盘电极1320下方,二者中间通过第二绝缘层800相互隔离,形成如图4中虚线方框所示的区域。当第二绝缘层800因为某些原因导致断裂或出现裂痕,均可能导致第二p型电极710和n焊盘电极1320连通,导致漏电的发生,使现有发光元件使用时的可靠性降低。而本实施方式中,在第二绝缘层800与焊盘电极之间,增加不与第二电极层和焊盘电极层相连接的支撑层900,以及与焊盘电极层相隔离的第三绝缘层1000。

37.如图8和9所示,支撑层900设置于第二绝缘层800和焊盘电极层之间;第三绝缘层1000完全覆盖第二绝缘层800和支撑层900形成的表面;支撑层900通过第二绝缘层800与第二电极层绝缘隔离;并且支撑层900通过第三绝缘层1000与焊盘电极层绝缘隔离。支撑层900包括p区支撑层和n区支撑层;p区支撑层覆盖第二p型电极710的区域,起阻挡第二p型电极710的作用;n区支撑层覆盖第二n型电极720的区域,起阻挡第二n型电极720的作用。第三通孔1100和第四通孔1200同时贯穿第二绝缘层800和第三绝缘层1000后分别直通第二p型电极710和第二n型电极720。

38.支撑层900可以为任意材质,为保证更好的支撑效果,以及适用于成熟的芯片制备工艺,支撑层900的材质优选为金属层,金属层包括cr、ni、ti、pt和au的金属单层或者几种金属单层组成的复合金属层。支撑层900的材质优选为导光性较好的金属氧化物,如氧化铟锡、氧化锌、氧化锡。支撑层900的材质优选为具有绝缘性质的dbr反射层,如sio2/tio

2 dbr反射层。支撑层900的厚度<2μm,支撑层900的面积占发光元件的面积的50%~80%,使得电极反射率在60%~95%,为保证后续薄膜覆盖,该层金属电极角度要求为30

°

~75

°

。

39.本实施方式通过增加支撑层900和第三绝缘层1000,使得焊盘电极层的p焊盘电极1310、n焊盘电极1320与支撑层900、支撑层900与第二电极层均不连通,且彼此绝缘,而焊盘电极层与第二电极层通过贯穿第二绝缘层800和第三绝缘层1000的通孔导电连通。并且第三绝缘层1000与第二绝缘层800采用同一光刻进行开孔刻蚀,实现了将支撑层900从各个面都包裹在绝缘的sio2薄膜中,从而实现了支撑层900与各层电极互不相连,起到异性电极的绝缘隔离作用,有效避免因绝缘层断裂导致的发光元件漏电,增加了发光元件的可靠性。

40.本实施方式中的发光元件的制备方法与实施方式1也是大致相同,区别点仅在于,在s10中,在刻蚀第二绝缘层800得到第三通孔1100和第四通孔1200之前,还在第二绝缘层800上依次沉积支撑层900和第三绝缘层1000,然后再在第二p型电极710和第二n型电极720上方无支撑层900的区域,同时刻蚀第二绝缘层800和第三绝缘层1000得到第三通孔1100和第四通孔1200。第三通孔1100和第四通孔1200距离支撑层900边缘的最小距离>5μm,保证支撑层900各个面完全包裹于第二绝缘层800和第三绝缘层1000中,隔绝支撑层900与任何金属电极的导电连通。

41.与实施方式1相比,本实施方式中的发光元件的可靠性明显提升(测试结果见下表1)。

42.除此之外,本实施方式与实施方式1完全相同,此处不做赘述。

43.实施方式3:本实施方式与实施方式1大致相同,不同点仅在于,本实施方式中,第二电极层中,第二p型电极710的四个外侧面中,四个外侧面上均具有连续的内凹部,各内凹部1410的面积之和占第二电极层面积的12.5%。如图10,即,尽量多的去除边缘位置的相邻两个第二p型电极710之间的第二电极层。与实施方式1相比,本实施方式中的发光元件的反射率进一步提高,整体亮度进一步提高(测试结果见下表1)。

44.除此之外,本实施方式与实施方式1完全相同,此处不做赘述。

45.对比例本对比例与实施方式1的区别仅在于,第二电极层中,第二p型电极710的四个外侧面中均没有开设用于减小第二电极层面积的任何内凹部1410,,其第二电极层光罩平面图如图3所示。

46.将实施方式1、2和3以及对比例中所述的发光元件在测试电流为65ma的相同测试条件下进行对比试验,本发明实施方式1、2和3提供的发光元件的发光亮度相较于比较例分别提升了0.2%和0.3%。通过测试条件为-45℃-125℃ ,每次15min 冷热冲击,确认各条件死灯的冲击循环次数,测试实施方式1、2和3以及对比例中所述的发光元件的可靠性可知,实施方式2中的发光元件的冲击循环次数最高,因此可靠性最高。

47.表1 亮度(mw)可靠性(cycle)实施方式1168.13250实施方式2168.24130实施方式3168.73320对比例167.83278上述实施方式只为说明本发明的技术构思及特点,其目的在于让熟悉此项技术的人能够了解本发明的内容并据以实施,并不能以此限制本发明的保护范围。凡根据本发明精神实质所做的等效变换或修饰,都应涵盖在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1