显示面板和包括该显示面板的显示装置的制作方法

1.发明构思的实施总体上涉及一种显示面板和包括该显示面板的显示装置。具体地,发明构思的实施总体上涉及一种包括屏蔽图案的显示面板和包括该显示面板的显示装置。

背景技术:

2.常规的显示装置包括显示面板,并且在显示面板中设置有包括有源图案的晶体管。通过提供到显示面板的信号和电压可以在显示面板内部生成电场。包括在显示面板的有机膜层中的有机材料可能因电场而极化。极化的有机材料可能影响显示面板的有源图案的电性质。因此,可能改变晶体管的电特性。另外,极化现象可能因入射在显示面板上的光而被进一步促进。因此,常规显示装置的显示质量可能劣化。

技术实现要素:

3.实施例提供了一种具有提高的显示质量的显示面板。

4.实施例提供了一种包括所述显示面板的显示装置。

5.根据实施例的显示面板可以包括:基底;第一阻挡层,设置在基底上;屏蔽图案,设置在第一阻挡层上;第二阻挡层,覆盖屏蔽图案,并且设置在第一阻挡层上;第一有源图案,设置在第二阻挡层上,并且在平面图中与屏蔽图案叠置;栅电极,设置在第一有源图案上;发射控制线,设置在第一有源图案上,并且在平面图中与栅电极的一侧相邻;以及上补偿控制线,设置在发射控制线上,并且在平面图中与栅电极的另一侧相邻。

6.根据实施例,屏蔽图案可以包括:第一图案;以及第二图案,连接到第一图案,并且第一图案和第二图案关于穿过第一图案和第二图案的中间的对称线对称。

7.根据实施例,第一图案可以包括在平面图中与栅电极叠置的第一部分。

8.根据实施例,第一部分可以在平面图中与栅电极完全叠置。

9.根据实施例,显示面板还可以包括设置在上补偿控制线上并且被提供有高电力电压的高电力电压线。第一图案还可以包括在平面图中与高电力电压线叠置的第二部分。

10.根据实施例,基底可以包括有机膜层。

11.根据实施例,屏蔽图案可以包括非晶硅。

12.根据实施例,显示面板还可以包括设置在发射控制线上的第二有源图案。第一有源图案可以包括多晶硅,并且第二有源图案可以包括氧化物半导体。

13.根据实施例,可以在第一有源图案中掺杂正离子,并且可以在屏蔽图案中掺杂正离子。

14.根据实施例,可以在第一有源图案中掺杂正离子,并且可以在屏蔽图案中掺杂负离子。

15.根据实施例,恒定电压可以施加到屏蔽图案。

16.根据实施例,屏蔽图案可以是电浮置的。

17.根据实施例,显示面板还可以包括:第三阻挡层,设置在基底下面;以及有机膜层,设置在第三阻挡层下面。

18.根据实施例,第一阻挡层的厚度可以小于第二阻挡层的厚度。

19.根据实施例,第三阻挡层的厚度可以等于第一阻挡层的厚度与第二阻挡层的厚度之和。

20.根据实施例,显示面板还可以包括:第二有源图案,设置在发射控制线上;以及下补偿控制线,设置在栅电极与第二有源图案之间。上补偿控制线可以在平面图中与下补偿控制线叠置,并且可以电连接到下补偿控制线。

21.根据另一实施例的显示面板可以包括:基底;第一阻挡层,设置在基底上;屏蔽图案,设置在第一阻挡层上,并且具有岛形状;第二阻挡层,覆盖屏蔽图案,并且设置在第一阻挡层上;第一有源图案;设置在第二阻挡层上,并且在平面图中与屏蔽图案叠置;栅电极,设置在第一有源图案上;发射控制线,设置在第一有源图案上,并且在平面图中与栅电极的一侧相邻;以及上补偿控制线,设置在第二有源图案上,并且在平面图中与栅电极的另一侧相邻。

22.根据实施例,屏蔽图案可以包括:第一部分,在平面图中与栅电极叠置;以及第二部分,在平面图中与上补偿控制线叠置。

23.根据实施例的显示装置可以包括显示面板。显示面板可以包括:基底;第一阻挡层,设置在基底上;屏蔽图案,设置在第一阻挡层上;第二阻挡层,覆盖屏蔽图案,并且设置在第一阻挡层上;第一有源图案,设置在第二阻挡层上,并且在平面图中与屏蔽图案叠置;栅电极,设置在第一有源图案上;发射控制线,设置在第一有源图案上,并且在平面图中与栅电极的一侧相邻;以及上补偿控制线,设置在第二有源图案上,并且在平面图中与栅电极的另一侧相邻。

24.根据实施例,显示装置还可以包括:光学传感器,设置在显示面板下面,并且在平面图中与指纹识别区域叠置;以及空气层,设置在显示面板与光学传感器之间,并且在平面图中与指纹识别区域叠置。屏蔽图案可以在平面图中与指纹识别区域叠置。

25.因此,根据本发明构思的实施例的显示面板可以包括设置在基底与有源图案之间并且具有网格结构的屏蔽图案,基底包括有机膜层。屏蔽图案可以对有源图案进行屏蔽使其免受包括在有机膜层中的极化的有机材料影响。因此,由于有机材料引起的电效应(例如,背沟道的形成)可以不施加到有源图案,并且包括有源图案的晶体管的电特性可以不被改变。因此,可以提高显示面板的显示质量。

26.将理解的是,前面的总体描述和以下的详细描述都是示例,并且旨在提供对所要求保护的发明构思的进一步解释。

附图说明

27.附图与描述一起示出了发明构思的实施例,附图被包括以提供对发明构思的进一步理解并且被并入本说明书中且构成本说明书的一部分。

28.图1是示出根据实施例的显示装置的平面图。

29.图2是示出图1的显示装置的框图。

30.图3是示出包括在图2的显示装置中的像素电路和有机发光二极管的电路图。

31.图4是沿着图1的线i-i'截取的剖视图。

32.图5、图6、图7、图8、图9、图10、图11、图12、图13、图14、图15和图16是示出根据实施例的显示装置的布局图。

33.图17是示出沿着图16的线ii-ii'截取的示例的剖视图。

34.图18是示出沿着图16的线ii-ii'截取的另一示例的剖视图。

35.图19、图20、图21和图22是示出根据另一实施例的显示装置的布局图。

36.图23、图24、图25、图26、图27和图28是示出根据又一实施例的显示装置的布局图。

37.图29、图30、图31、图32、图33、图34和图35是示出根据又一实施例的显示装置的布局图。

具体实施方式

38.根据以下结合附图的详细描述,将更清楚地理解说明性的非限制性的实施例。

39.图1是示出根据实施例的显示装置的平面图。图2是示出图1的显示装置的框图。图3是示出包括在图2的显示装置中的像素电路和有机发光二极管的电路图。图4是沿着图1的线i-i'截取的剖视图。

40.参照图1和图2,根据本发明构思的实施例的显示装置10可以包括显示区域da和非显示区域nda。指纹识别区域fa设置在显示区域da中。显示区域da可以具有拥有在第一方向d1上延伸的短边和在与第一方向d1交叉的第二方向d2上延伸的长边的矩形形状。非显示区域nda可以被设置为围绕显示区域da。显示区域da可以被设置为围绕指纹识别区域fa。显示面板100可以与显示区域da和指纹识别区域fa叠置。数据驱动器200、栅极驱动器300、发射驱动器400和时序控制器500可以设置在非显示区域nda中。

41.第一像素结构px1和第二像素结构px2可以设置在显示面板100中。第一像素结构px1和第二像素结构px2中的每个可以电连接到数据线dl、栅极线gl和发射控制线eml。

42.数据线dl可以电连接到数据驱动器200并且可以沿着第二方向d2延伸。数据线dl可以传输数据电压(例如,图3中的数据电压data)。

43.栅极线gl可以连接到栅极驱动器300并且可以沿着第一方向d1延伸。栅极线gl可以传输栅极信号(例如,图3中的第一栅极信号gw、第二栅极信号gc、第三栅极信号gi和第四栅极信号gb)。

44.发射控制线eml可以连接到发射驱动器400并且可以沿着第一方向d1延伸。发射控制线eml可以传输发射控制信号(例如,图3中的发射控制信号em)。例如,发射控制信号em的激活时段可以是显示装置10的发射时段,发射控制信号em的非激活时段可以是显示装置10的非发射时段。

45.栅极驱动器300可以接收来自时序控制器500的栅极控制信号gctrl,并且可以生成栅极信号。例如,栅极信号可以包括第一栅极信号gw、第二栅极信号gc、第三栅极信号gi和第四栅极信号gb。

46.数据驱动器200可以接收来自时序控制器500的输出图像数据odta和数据控制信号dctrl,并且可以生成数据电压data。发射驱动器400可以接收来自时序控制器500的发射驱动控制信号ectrl,并且可以生成发射控制信号em。时序控制器500可以接收来自外部装置的控制信号ctrl和输入图像数据idat,并且可以控制数据驱动器200、栅极驱动器300和

发射驱动器400。

47.例如,数据驱动器200和时序控制器500可以设置在柔性印刷电路板上,栅极驱动器300可以安装在与显示区域da的左侧相邻的非显示区域nda中,发射驱动器400可以安装在与显示区域da的右侧相邻的非显示区域nda中。然而,设置数据驱动器200、栅极驱动器300、发射驱动器400和时序控制器500的位置不限于此。

48.参照图2和图3,第一像素结构px1可以包括像素电路pc和有机发光二极管oled。第二像素结构px2可以具有与第一像素结构px1的电路结构基本相同的电路结构。在实施例中,第一像素结构px1和第二像素结构px2可以关于穿过第一像素结构px1和第二像素结构px2的中间的对称线对称。

49.像素电路pc可以包括第一晶体管t1、第二晶体管t2、第三晶体管t3、第四晶体管t4、第五晶体管t5、第六晶体管t6和第七晶体管t7以及存储电容器cst。像素电路pc可以电连接到有机发光二极管oled,并且可以向有机发光二极管oled提供驱动电流。

50.有机发光二极管oled可以包括第一端子(例如,阳极端子)和第二端子(例如,阴极端子)。第一端子可以连接到第六晶体管t6和第七晶体管t7,第二端子可以接收低电力电压elvss。有机发光二极管oled可以生成具有与驱动电流对应的亮度的光。

51.存储电容器cst可以包括第一端子和第二端子。存储电容器cst的第一端子可以连接到第一晶体管t1,存储电容器cst的第二端子可以接收高电力电压elvdd。存储电容器cst可以在第一栅极信号gw的非激活时段保持第一晶体管t1的栅极端子的电压电平。

52.第一晶体管t1可以包括栅极端子、第一端子(例如,源极端子)和第二端子(例如,漏极端子)。第一晶体管t1的栅极端子可以连接到存储电容器cst的第一端子。第一晶体管t1的第一端子可以连接到第二晶体管t2,并且可以接收数据电压data。第一晶体管t1的第二端子可以连接到第六晶体管t6。第一晶体管t1可以基于第一晶体管t1的栅极端子与第一端子之间的电压差来生成驱动电流。例如,第一晶体管t1可以被称为驱动晶体管。

53.第二晶体管t2可以包括栅极端子、第一端子(例如,源极端子)和第二端子(例如,漏极端子)。第二晶体管t2的栅极端子可以通过栅极线gl接收第一栅极信号gw。

54.第二晶体管t2可以响应于第一栅极信号gw而导通或截止。例如,当第二晶体管t2是pmos晶体管时,第二晶体管t2可以在第一栅极信号gw具有正电压电平时截止,并且可以在第一栅极信号gw具有负电压电平时导通。第二晶体管t2的第一端子可以通过数据线dl接收数据电压data。当第二晶体管t2导通时,第二晶体管t2的第二端子可以向第一晶体管t1的第一端子提供数据电压data。例如,第二晶体管t2可以被称为开关晶体管。

55.第三晶体管t3可以包括栅极端子、下栅极端子、第一端子(例如,源极端子)和第二端子(例如,漏极端子)。第三晶体管t3的栅极端子和下栅极端子可以接收第二栅极信号gc。第三晶体管t3的第一端子可以连接到第一晶体管t1的第二端子。第三晶体管t3的第二端子可以连接到第一晶体管t1的栅极端子。

56.第三晶体管t3可以响应于第二栅极信号gc而导通或截止。例如,当第三晶体管t3是nmos晶体管时,第三晶体管t3可以在第二栅极信号gc具有正电压电平时导通,并且可以在第二栅极信号gc具有负电压电平时截止。

57.在其中第三晶体管t3响应于第二栅极信号gc而导通的时段期间,第三晶体管t3可以使第一晶体管t1二极管连接。第三晶体管t3可以补偿第一晶体管t1的阈值电压。例如,第

三晶体管t3可以被称为补偿晶体管。

58.第四晶体管t4可以包括栅极端子、下栅极端子、第一端子(例如,源极端子)和第二端子(例如,漏极端子)。第四晶体管t4的栅极端子和下栅极端子可以接收第三栅极信号gi。第四晶体管t4的第一端子可以连接到第一晶体管t1的栅极端子。第四晶体管t4的第二端子可以接收栅极初始化电压vint。

59.第四晶体管t4可以响应于第三栅极信号gi而导通或截止。例如,当第四晶体管t4是nmos晶体管时,第四晶体管t4可以在第三栅极信号gi具有正电压电平时导通,并且可以在第三栅极信号gi具有负电压电平时截止。

60.在其中第四晶体管t4响应于第三栅极信号gi而导通的时段期间,栅极初始化电压vint可以被提供到第一晶体管t1的栅极端子。因此,第四晶体管t4可以使第一晶体管t1的栅极端子初始化为栅极初始化电压vint。例如,第四晶体管t4可以被称为栅极初始化晶体管。

61.第五晶体管t5可以包括栅极端子、第一端子(例如,源极端子)和第二端子(例如,漏极端子)。第五晶体管t5的栅极端子可以接收发射控制信号em。第五晶体管t5的第一端子可以接收高电力电压elvdd。第五晶体管t5的第二端子可以连接到第一晶体管t1。当第五晶体管t5响应于发射控制信号em而导通时,第五晶体管t5可以向第一晶体管t1提供高电力电压elvdd。

62.第六晶体管t6可以包括栅极端子、第一端子(例如,源极端子)和第二端子(例如,漏极端子)。第六晶体管t6的栅极端子可以接收发射控制信号em。第六晶体管t6的第一端子可以连接到第一晶体管t1。第六晶体管t6的第二端子可以连接到有机发光二极管oled。当第六晶体管t6响应于发射控制信号em而导通时,第六晶体管t6可以向有机发光二极管oled提供驱动电流。

63.第七晶体管t7可以包括栅极端子、第一端子(例如,源极端子)和第二端子(例如,漏极端子)。第七晶体管t7的栅极端子可以接收第四栅极信号gb。第七晶体管t7的第一端子可以连接到有机发光二极管oled。第七晶体管t7的第二端子可以接收阳极初始化电压aint。

64.当第七晶体管t7响应于第四栅极信号gb而导通时,第七晶体管t7可以向有机发光二极管oled提供阳极初始化电压aint。因此,第七晶体管t7可以使有机发光二极管oled的第一端子初始化为阳极初始化电压aint。例如,第七晶体管t7可以被称为阳极初始化晶体管。

65.在实施例中,第一晶体管t1、第二晶体管t2、第五晶体管t5、第六晶体管t6和第七晶体管t7可以是pmos晶体管,第三晶体管t3和第四晶体管t4可以是nmos晶体管。因此,pmos晶体管的第一有源图案可以包括掺杂有正离子的多晶硅,nmos晶体管的第二有源图案可以包括氧化物半导体。另外,分别用于导通第二晶体管t2、第五晶体管t5、第六晶体管t6和第七晶体管t7的第一栅极信号gw、发射控制信号em和第四栅极信号gb可以具有负电压电平,分别用于导通第三晶体管t3和第四晶体管t4的第二栅极信号gc和第三栅极信号gi可以具有正电压电平。

66.同时,图3中示出的像素电路pc的连接结构是示例并且可以不同地改变。

67.参照图1和图4,显示装置10可以包括显示面板100、光学传感器lsm和设置在显示

面板100上方和下方的功能层。例如,功能层可以包括垫层csl、保护膜pfl、空气层arl、偏振层pol和窗win。另外,粘合层可以设置在功能层之间,并且粘合层可以包括光学透明粘合剂(oca)。

68.显示面板100可以与显示区域da和指纹识别区域fa叠置。如上所述,显示面板100可以包括第一像素结构px1和第二像素结构px2。例如,第一像素结构px1和第二像素结构px2可以与指纹识别区域fa叠置。

69.保护膜pfl可以设置在显示面板100下面。保护膜pfl可以与显示区域da叠置,并且可以不与指纹识别区域fa叠置。例如,可以在保护膜pfl中形成与指纹识别区域fa叠置的开口。保护膜pfl可以包括塑料材料,并且可以支撑显示面板100。

70.空气层arl可以设置在显示面板100下面。空气层arl可以与指纹识别区域fa叠置。例如,空气层arl可以形成在开口中。光可以经由空气层arl容易地传输到光学传感器lsm。

71.垫层csl可以设置在保护膜pfl下面。垫层csl可以与显示区域da叠置,并且可以不与指纹识别区域fa叠置。换句话说,与指纹识别区域fa叠置的开口可以形成在垫层csl中。垫层csl可以包括弹性体,并且可以保护显示面板100免受外部冲击。

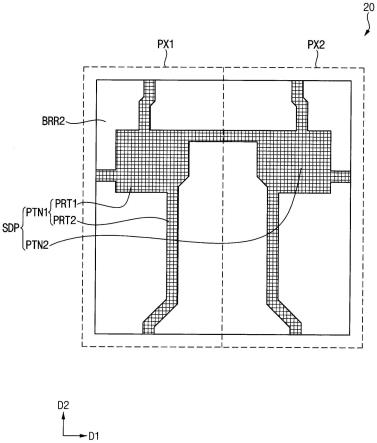

72.光学传感器lsm可以设置在保护膜pfl下面。光学传感器lsm可以与指纹识别区域fa叠置。换句话说,光学传感器lsm可以设置在形成于垫层csl中的开口中。光学传感器lsm可以识别用户的指纹。例如,从显示面板100发射的光可以被用户的手指反射,光学传感器lsm可以检测从用户的手指反射的光。为了使光学传感器lsm检测光,光学传感器lsm可以通过空气层arl暴露。

73.偏振层pol可以设置在显示面板100上。偏振层pol可以减少外部光的反射。

74.窗win可以设置在偏振层pol上。窗win可以由玻璃或塑料等制成,并且可以保护显示面板100免受外部冲击。

75.同时,由于空气层arl设置在显示面板100下面,光可以入射到与指纹识别区域fa叠置的显示面板100。例如,从外部入射并从光学传感器lsm反射的光11以及/或者从显示面板100发射并从光学传感器lsm反射的光12可以入射到显示面板100。

76.常规的显示装置包括显示面板,包括有源图案的晶体管设置在显示面板中。通过提供到显示面板的信号和电压可以在显示面板内部生成电场。包括在显示面板的有机膜层中的有机材料可能因电场而极化。极化的有机材料可能影响显示面板的有源图案的电性质。因此,晶体管的电特性可能被改变。另外,极化现象可能因入射在显示面板上的光而被进一步促进。因此,常规的显示装置的显示质量可能劣化。

77.根据实施例的显示装置10可以包括设置在显示面板100内部的屏蔽图案。屏蔽图案可以防止极化的有机材料影响第一有源图案和第二有源图案的电性质。因此,可以不改变晶体管的电特性。因此,可以提高显示装置10的显示质量。下面将对其进行详细描述。

78.图5至图16是示出根据实施例的显示装置的布局图。图17是示出沿着图16的线ii-ii'截取的示例的剖视图。图18是示出沿着图16的线ii-ii'截取的另一示例的剖视图。

79.参照图5,根据本发明构思的实施例的显示装置20可以包括第一像素结构px1和被设置为与第一像素结构px1相邻的第二像素结构px2。第二像素结构px2可以具有与第一像素结构px1的电路结构基本相同的电路结构。在实施例中,第一像素结构px1和第二像素结构px2可以关于穿过第一像素结构px1和第二像素结构px2的中间的对称线对称。

80.参照图6、图7、图8、图9和图17,第一像素结构px1可以包括第一有机膜层pi1、第一阻挡层brr1、第二有机膜层pi2、第二阻挡层brr2、屏蔽图案sdp和第三阻挡层brr3。

81.第一有机膜层pi1可以包括有机材料。例如,第一有机膜层pi1可以包括聚酰亚胺。

82.第一阻挡层brr1可以设置在第一有机膜层pi1上。第一阻挡层brr1可以包括无机材料。例如,第一阻挡层brr1可以包括氧化硅或氮化硅等。

83.第二有机膜层pi2可以设置在第一阻挡层brr1上。例如,第二有机膜层pi2可以包括与第一有机膜层pi1相同的材料。

84.第二阻挡层brr2可以设置在第二有机膜层pi2上。第二阻挡层brr2可以包括与第一阻挡层brr1相同的材料。例如,第一有机膜层pi1、第一阻挡层brr1、第二有机膜层pi2和第二阻挡层brr2中的至少一者可以构成显示面板100的基底。

85.在实施例中,屏蔽图案sdp可以设置在第二有机膜层pi2与第一有源图案1100之间。例如,屏蔽图案sdp可以设置在第二阻挡层brr2上。

86.在实施例中,屏蔽图案sdp可以包括硅半导体。例如,屏蔽图案sdp可以包括非晶硅或多晶硅。另外,屏蔽图案sdp可以掺杂有正离子或负离子。例如,正离子可以是iii族元素(例如,硼)等。负离子可以是v族元素(例如,磷)等。

87.在实施例中,可以向屏蔽图案sdp提供恒定电压(即,dc电压)。在另一实施例中,屏蔽图案sdp可以是电浮置的。在另一实施例中,可以向屏蔽图案sdp提供ac电压。

88.在实施例中,屏蔽图案sdp可以包括第一图案ptn1和第二图案ptn2。第一图案ptn1可以包括第一部分prt1和第二部分prt2。第一图案ptn1和第二图案ptn2可以关于穿过第一图案ptn1和第二图案ptn2的中间的对称线对称。

89.第一部分prt1可以与稍后将描述的栅电极(例如,图11中的第一栅电极1221)完全叠置。例如,第一部分prt1的形状可以与第一栅电极1221的形状基本相同,并且第一部分prt1的尺寸可以大于或等于第一栅电极1221的尺寸。

90.第二部分prt2可以与稍后将描述的高电力电压线(例如,图16中的高电力电压线1720)完全叠置。例如,第二部分prt2可以沿着高电力电压线1720设置以与高电力电压线1720完全叠置。

91.在实施例中,可以根据在屏蔽图案sdp中掺杂的正离子或负离子的掺杂浓度来设定屏蔽图案sdp的第三厚度th3。例如,当屏蔽图案sdp掺杂有具有约10

12

的浓度的硼时,屏蔽图案sdp的第三厚度th3可以为约500埃。

92.在实施例中,如图7和图8中所示,屏蔽图案sdp可以具有网格形状。例如,多个屏蔽图案sdp可以设置在第二阻挡层brr2上。屏蔽图案sdp可以以特定单元重复地布置。由于屏蔽图案sdp具有网格结构,因此屏蔽图案sdp可以有效地抑制有机材料的极化。

93.第三阻挡层brr3可以覆盖屏蔽图案sdp,并且可以设置在第二阻挡层brr2上。第三阻挡层brr3可以包括与第一阻挡层brr1相同的材料。

94.在实施例中,第一阻挡层brr1的第一厚度th1可以等于第二阻挡层brr2的第二厚度th2与第三阻挡层brr3的第四厚度th4之和。另外,第二阻挡层brr2的第二厚度th2可以比第三阻挡层brr3的第四厚度th4薄。例如,第一阻挡层brr1的第一厚度th1可以为约5000埃,第二阻挡层brr2的第二厚度th2可以为约500埃,第三阻挡层brr3的第四厚度th4可以为约4500埃。因此,第三厚度th3可以等于第二厚度th2。

95.由于第二阻挡层brr2的第二厚度th2比第三阻挡层brr3的第四厚度th4薄,因此屏蔽图案sdp与第一栅电极1221之间的距离可以相对增加。因此,可以防止屏蔽图案sdp与第一栅电极1221之间的耦合现象(coupling phenomenon)。另外,由于第二阻挡层brr2具有第二厚度th2,因此第二阻挡层brr2可以保护在形成屏蔽图案sdp的工艺中可能被损坏的第二有机膜层pi2。

96.缓冲层bfr可以设置在第三阻挡层brr3上。缓冲层bfr可以防止金属原子或杂质扩散到第一有源图案中。另外,缓冲层bfr可以在用于形成第一有源图案的结晶工艺期间控制热传导的速率。

97.参照图10和图17,第一有源图案1100可以设置在缓冲层bfr上。第一有源图案1100可以与屏蔽图案sdp叠置。例如,至少第一有源图案1100的沟道形成区域可以设置在屏蔽图案sdp上。在实施例中,第一有源图案1100可以包括硅半导体。例如,第一有源图案1100可以包括非晶硅或多晶硅等。

98.在实施例中,可以使用稍后将描述的第一导电图案1200作为自对准掩模来将正离子或负离子选择性地注入到除了沟道区域之外的第一有源图案1100中。例如,当第一晶体管t1、第二晶体管t2、第五晶体管t5、第六晶体管t6和第七晶体管t7是pmos晶体管时,第一有源图案1100可以包括正离子注入于其中的源极区域、正离子注入于其中的漏极区域和未掺杂有杂质的沟道区域。

99.第一栅极绝缘层gi1可以覆盖第一有源图案1100,并且可以设置在缓冲层bfr上。第一栅极绝缘层gi1可以包括绝缘材料。例如,第一栅极绝缘层gi1可以包括氧化硅、氮化硅或氮氧化硅等。

100.参照图11和图17,第一导电图案1200可以设置在第一栅极绝缘层gi1上。第一导电图案1200可以包括第一栅极线1210、第一栅电极1221、第二栅电极1222和第二栅极线1230。

101.第一栅极线1210可以设置在第一有源图案1100上,并且可以沿着第一方向d1延伸。在实施例中,在平面图中,第一栅极线1210可以被设置为与第一栅电极1221的一侧相邻。第一栅极线1210可以与第一有源图案1100一起构成第五晶体管t5和第六晶体管t6。发射控制信号em可以提供到第一栅极线1210。例如,第一栅极线1210可以被称为发射控制线。

102.第一栅电极1221可以与第一图案ptn1的第一部分prt1和第一有源图案1100叠置。第一栅电极1221可以与第一有源图案1100一起构成包括在第一像素结构px1中的第一晶体管t1。

103.第二栅电极1222可以在第一方向d1上与第一栅电极1221间隔开。第二栅电极1222可以与第二图案ptn2和第一有源图案1100叠置。第二栅电极1222可以与第一有源图案1100一起构成包括在第二像素结构px2中的第一晶体管t1。

104.第二栅极线1230可以设置在第一有源图案1100上,并且可以沿着第一方向d1延伸。例如,第二栅极线1230可以与第一有源图案1100一起构成第二晶体管t2。第一栅极信号gw可以提供到第二栅极线1230。

105.另外,第二栅极线1230可以与第一有源图案1100一起构成第七晶体管t7。第四栅极信号gb可以提供到第二栅极线1230。例如,第一栅极信号gw和第四栅极信号gb可以具有基本相同的波形。

106.例如,第一导电图案1200可以包括金属、合金、导电金属氧化物和透明导电材料

等。例如,第一导电图案1200可以包括银(ag)、包含银的合金、钼(mo)、包含钼的合金、铝(al)、包含铝的合金、氮化铝(aln)、钨(w)、氮化钨(wn)、铜(cu)、镍(ni)、铬(cr)、氮化铬(crn)、钛(ti)、钽(ta)、铂(pt)、钪(sc)、氧化铟锡(ito)和氧化铟锌(izo)等。

107.第二栅极绝缘层gi2可以覆盖第一导电图案1200,并且可以设置在第一栅极绝缘层gi1上。第二栅极绝缘层gi2可以包括绝缘材料。

108.同时,第一晶体管t1、第二晶体管t2、第五晶体管t5、第六晶体管t6和第七晶体管t7可以基本与参照图3描述的第一晶体管t1、第二晶体管t2、第五晶体管t5、第六晶体管t6和第七晶体管t7对应。例如,第一栅电极1221可以与参照图3描述的第一晶体管t1的栅极端子对应。然而,上述对应关系对于本领域技术人员来说将是明显的。

109.参照12和图17,第二导电图案1300可以设置在第二栅极绝缘层gi2上。第二导电图案1300可以包括存储电容器电极1310、第三栅极线1320、第四栅极线1330和栅极初始化电压线1340。

110.存储电容器电极1310可以沿着第一方向d1延伸。在实施例中,存储电容器电极1310可以与第一栅电极1221一起构成包括在第一像素结构px1中的存储电容器cst。例如,存储电容器电极1310可以与第一栅电极1221叠置,高电力电压elvdd可以提供到存储电容器电极1310。另外,存储电容器电极1310可以与第二栅电极1222一起构成包括在第二像素结构px2中的存储电容器cst。例如,存储电容器电极1310可以与第二栅电极1222叠置。

111.在实施例中,暴露第一栅电极1221和第二栅电极1222的顶表面的开口可以形成在存储电容器电极1310中。

112.第三栅极线1320可以沿着第一方向d1延伸。在实施例中,在平面图中,第三栅极线1320可以被设置为和与第一栅电极1221的所述一侧相对的另一侧相邻。在实施例中,第三栅极线1320可以向第三晶体管t3提供第二栅极信号gc。例如,第三栅极线1320可以与第三晶体管t3的下栅极端子对应。第三栅极线1320可以被称为下补偿控制线。

113.第四栅极线1330可以沿着第一方向d1延伸。在实施例中,第四栅极线1330可以向第四晶体管t4提供第三栅极信号gi。例如,第四栅极线1330可以与第四晶体管t4的下栅极端子对应。

114.栅极初始化电压线1340可以沿着第一方向d1延伸。在实施例中,栅极初始化电压线1340可以向第四晶体管t4提供栅极初始化电压vint。例如,栅极初始化电压线1340可以电连接到稍后将描述的第二有源图案(例如,图13中的第二有源图案1400)。

115.例如,第二导电图案1300可以包括金属、合金、导电金属氧化物或透明导电材料等。

116.第一层间绝缘层ild1可以覆盖第二导电图案1300,并且可以设置在第二栅极绝缘层gi2上。第一层间绝缘层ild1可以包括绝缘材料。

117.参照图13和图17,第二有源图案1400可以设置在第一层间绝缘层ild1上。例如,第二有源图案1400可以与第三栅极线1320、第四栅极线1330和栅极初始化电压线1340叠置。

118.在实施例中,第二有源图案1400可以与第一有源图案1100设置在不同的层上。换句话说,第二有源图案1400可以与第一有源图案1100分开地形成。例如,第一有源图案1100可以包括硅半导体,第二有源图案1400可以包括氧化物半导体。

119.在实施例中,第一像素结构px1可以包括作为硅基晶体管的第一晶体管t1、第二晶

体管t2、第五晶体管t5、第六晶体管t6和第七晶体管t7,以及作为氧化物基晶体管的第三晶体管t3和第四晶体管t4。例如,第一晶体管t1、第二晶体管t2、第五晶体管t5、第六晶体管t6和第七晶体管t7可以是pmos晶体管,第三晶体管t3和第四晶体管t4可以是nmos晶体管。

120.第三栅极绝缘层gi3可以覆盖第二有源图案1400,并且可以设置在第一层间绝缘层ild1上。第三栅极绝缘层gi3可以包括绝缘材料。

121.参照图14和图17,第三导电图案1500可以设置在第三栅极绝缘层gi3上。第三导电图案1500可以包括第五栅极线1510和第六栅极线1520。

122.第五栅极线1510可以沿着第一方向d1延伸。例如,第五栅极线1510可以与第三栅极线1320叠置,并且第五栅极线1510可以电连接到第三栅极线1320。在实施例中,第五栅极线1510可以向第三晶体管t3提供第二栅极信号gc。因此,第五栅极线1510可以与第三晶体管t3的栅极端子对应。第五栅极线1510可以被称为上补偿控制线。

123.第六栅极线1520可以沿着第一方向d1延伸。例如,第六栅极线1520可以与第四栅极线1330叠置,并且可以电连接到第四栅极线1330。在实施例中,第六栅极线1520可以向第四晶体管t4提供第三栅极信号gi。因此,第六栅极线1520可以与第四晶体管t4的栅极端子对应。

124.第二层间绝缘层ild2可以覆盖第三导电图案1500,并且可以设置在第一层间绝缘层ild1上。第二层间绝缘层ild2可以包括绝缘材料。

125.参照图15和图17,第四导电图案1600可以设置在第二层间绝缘层ild2上。第四导电图案1600可以包括第一高电力电压图案1611、第二高电力电压图案1612、第一阳极图案1621、第二阳极图案1622、第一补偿连接图案1631、第二补偿连接图案1632、第一初始化连接图案1641、第二初始化连接图案1642、阳极初始化电压线1650、第一数据图案1661、第二数据图案1662和栅极初始化电压图案1670。

126.第一高电力电压图案1611和第二高电力电压图案1612可以向第一有源图案1100传输高电力电压evldd。在实施例中,第一高电力电压图案1611和第二高电力电压图案1612可以电连接高电力电压线(例如,图16中的高电力电压线1720)和第一有源图案1100。例如,第一高电力电压图案1611和第二高电力电压图案1612可以接触高电力电压线1720和第一有源图案1100。

127.第一阳极图案1621可以向包括在第一像素结构px1中的有机发光二极管oled提供阳极初始化电压aint或驱动电流。例如,第一阳极图案1621可以接触第一有源图案1100和第三阳极图案(例如,图16中的第三阳极图案1731)。

128.第二阳极图案1622可以向包括在第二像素结构px2中的有机发光二极管oled提供阳极初始化电压aint或驱动电流。例如,第二阳极图案1622可以接触第一有源图案1100和第四阳极图案(例如,图16的第四阳极图案1732)。

129.第一补偿连接图案1631可以电连接包括在第一像素结构px1中的第一晶体管t1的第二端子和第三晶体管t3的第一端子。例如,第一补偿连接图案1631可以接触第一有源图案1100和第二有源图案1400。

130.第二补偿连接图案1632可以电连接包括在第二像素结构px2中的第一晶体管t1的第二端子和第三晶体管t3的第一端子。例如,第二补偿连接图案1632可以接触第一有源图案1100和第二有源图案1400。

131.第一初始化连接图案1641可以电连接包括在第一像素结构px1中的第一晶体管t1的栅极端子和第四晶体管t4的第一端子。例如,第一初始化连接图案1641可以接触第二有源图案1400和第一栅电极1221。

132.第二初始化连接图案1642可以电连接包括在第二像素结构px2中的第一晶体管t1的栅极端子和第四晶体管t4的第一端子。例如,第二初始化连接图案1642可以接触第二有源图案1400和第二栅电极1222。

133.阳极初始化电压线1650可以向第七晶体管t7提供阳极初始化电压aint。例如,阳极初始化电压线1650可以接触第一有源图案1100。

134.第一数据图案1661可以向包括在第一像素结构px1中的第二晶体管t2提供数据电压data。例如,第一数据图案1661可以接触第一有源图案1100和第一数据线(例如,图16中的第一数据线1711)。

135.第二数据图案1662可以向包括在第二像素结构px2中的第二晶体管t2提供数据电压data。例如,第二数据图案1662可以接触第一有源图案1100和第二数据线(例如,图16中的第二数据线1712)。

136.栅极初始化电压图案1670可以向第四晶体管t4提供栅极初始化电压vint。例如,栅极初始化电压图案1670可以向第二有源图案1400提供栅极初始化电压vint。栅极初始化电压图案1670可以接触栅极初始化电压线1340和第二有源图案1400。

137.第一过孔绝缘层via1可以覆盖第四导电图案1600,并且可以设置在第二层间绝缘层ild2上。第一过孔绝缘层via1可以包括有机绝缘材料。例如,第一过孔绝缘层via1可以包括光致抗蚀剂、聚丙烯酸树脂、聚酰亚胺树脂或丙烯酸树脂等。

138.参照图16和图17,第五导电图案1700可以设置在第一过孔绝缘层via1上。第五导电图案1700可以包括第一数据线1711、第二数据线1712、高电力电压线1720、第三阳极图案1731和第四阳极图案1732。

139.第一数据线1711可以沿着第二方向d2延伸。在实施例中,第一数据线1711可以向包括在第一像素结构px1中的第二晶体管t2提供数据电压data。例如,第一数据线1711可以接触第一数据图案1661。

140.第二数据线1712可以沿着第二方向d2延伸。在实施例中,第二数据线1712可以向包括在第二像素结构px2中的第二晶体管t2提供数据电压data。例如,第二数据线1712可以接触第二数据图案1662。

141.高电力电压线1720可以沿着第二方向d2延伸。在实施例中,高电力电压线1720可以向第一高电力电压图案1611和第二高电力电压图案1612提供高电力电压elvdd。例如,高电力电压线1720可以接触第一高电力电压图案1611和第二高电力电压图案1612。

142.第三阳极图案1731可以向包括在第一像素结构px1中的有机发光二极管oled提供阳极初始化电压aint或驱动电流。例如,第三阳极图案1731可以接触第一阳极图案1621。

143.第四阳极图案1732可以向包括在第二像素结构px2中的有机发光二极管oled提供阳极初始化电压aint或驱动电流。例如,第四阳极图案1732可以接触第二阳极图案1622。

144.第二过孔绝缘层via2可以覆盖第五导电图案1700,并且可以设置在第一过孔绝缘层via1上。第二过孔绝缘层via2可以包括有机绝缘材料。例如,第二过孔绝缘层via2可以包括光致抗蚀剂、聚丙烯酸树脂、聚酰亚胺树脂或丙烯酸树脂等。

145.参照图17,屏蔽图案sdp可以与第一有源图案1100、第一栅电极1221和高电力电压线1720叠置。在平面图中,第一栅极线1210可以被设置为与第一栅电极1221的一侧相邻,第三栅极线1320和第五栅极线1510可以被设置为与第一栅电极1221的另一侧相邻。另外,正离子可以掺杂在屏蔽图案sdp中。

146.如上所述,发射控制信号em可以提供到第一栅极线1210,第二栅极信号gc可以提供到第三栅极线1320和第五栅极线1510。为了使第五晶体管t5和第六晶体管t6导通,发射控制信号em可以具有负电压电平。同时,为了使第三晶体管t3截止,第二栅极信号gc可以具有负电压电平。

147.在常规的显示装置中,由于发射控制信号em和第二栅极信号gc同时具有相同的负电压电平,因此可能在第二有机膜层pi2中形成电场。因此,第二有机膜层pi2中的有机材料可能被极化。背沟道(backchannel)可能因极化的有机材料而形成在第一有源图案1100中。因此,第一晶体管t1的电特性(例如,阈值电压、电子迁移率等)可能被改变。因此,包括其电特性被改变的第一晶体管t1的第一像素结构px1和第二像素结构px2可能发射与数据电压data不对应的亮度,并且显示装置的显示质量可能劣化。

148.然而,显示装置20可以包括设置在第二有机膜层pi2与第一有源图案1100之间的屏蔽图案sdp。屏蔽图案sdp可以对第一有源图案1100进行屏蔽使其免受极化的有机材料影响。因此,可以不在第一有源图案1100中形成背沟道,并且可以不改变第一晶体管t1的电特性。因此,可以提高显示装置20的显示质量。

149.另外,屏蔽图案sdp可以具有网格结构。例如,屏蔽图案sdp可以彼此连接,并且可以以特定单元重复布置。由于屏蔽图案sdp具有网格结构,因此屏蔽图案sdp可以有效地抑制有机材料的极化。

150.同时,参照图4描述的入射在显示面板100上的光(例如,图4中的光11或光12)可能进一步促进有机材料的极化现象。因此,在实施例中,屏蔽图案sdp可以与指纹识别区域fa叠置,而可以不与显示区域da叠置。换句话说,屏蔽图案sdp可以仅形成在与指纹识别区域fa叠置的显示面板100中,而可以不形成在不与指纹识别区域fa叠置的显示面板100中。

151.参照图18,负离子可以掺杂在屏蔽图案sdp'中。

152.图19至图22是示出根据另一实施例的显示装置的布局图。例如,图19是示出屏蔽图案的布局图,图20是示出屏蔽图案和第一有源图案的布局图,图21是示出屏蔽图案、第一有源图案和第一导电图案的布局图,图22是示出屏蔽图案、第一有源图案、第一导电图案和第五导电图案的布局图。

153.参照图19至图22,根据另一实施例的显示装置30可以包括第一像素结构px1和被设置为与第一像素结构px1相邻的第二像素结构px2。例如,第一像素结构px1和第二像素结构px2可以关于穿过第一像素结构px1和第二像素结构px2的中间的对称线对称。然而,除了屏蔽图案sdp的形状之外,第一像素结构px1和第二像素结构px2可以与包括在显示装置20中的第一像素结构px1和第二像素结构px2基本相同。例如,第一像素结构px1和第二像素结构px2可以包括上述第一有机膜层pi1、第一阻挡层brr1、第二有机膜层pi2、第二阻挡层brr2、缓冲层bfr、第一有源图案1100、第一栅极绝缘层gi1、第一导电图案1200、第二栅极绝缘层gi2、第二导电图案1300、第一层间绝缘层ild1、第二有源图案1400、第三栅极绝缘层gi3、第三导电图案1500、第二层间绝缘层ild2、第四导电图案1600、第一过孔绝缘层via1、

第五导电图案1700和第二过孔绝缘层via2。在下文中,将主要描述屏蔽图案sdp的形状。

154.如图19中所示,包括在显示装置30中的屏蔽图案sdp可以设置在第二阻挡层brr2上。在实施例中,屏蔽图案sdp可以沿着第二方向d2延伸,并且可以在第一方向d1上间隔开。

155.屏蔽图案sdp可以包括第一图案ptn1和第二图案ptn2。第一图案ptn1可以包括第一部分prt1和第二部分prt2。第一图案ptn1和第二图案ptn2可以关于穿过第一图案ptn1和第二图案ptn2的中间的对称线对称。

156.如图20中所示,第一部分prt1可以与第一有源图案1100叠置。如图21中所示,第一部分prt1可以与第一栅电极1221完全叠置。换句话说,第一部分prt1的形状可以与第一栅电极1221的形状基本相同,第一部分prt1的尺寸可以大于或等于第一栅电极1221的尺寸。如图22中所示,第二部分prt2可以与高电力电压线1720叠置。例如,第二部分prt2可以沿着高电力电压线1720设置。

157.屏蔽图案sdp可以对第一有源图案1100进行屏蔽使其免受第二有机膜层pi2的极化的有机材料影响。因此,可以不在第一有源图案1100中形成背沟道,并且可以不改变第一晶体管t1的电特性。因此,可以提高显示装置30的显示质量。

158.图23至图28是示出根据又一实施例的显示装置的布局图。例如,图23是示出屏蔽图案的布局图,图24是示出屏蔽图案和第一有源图案的布局图,图25是示出屏蔽图案、第一有源图案和第一导电图案的布局图,图26是示出屏蔽图案、第一有源图案、第一导电图案和第二导电图案的布局图,图27是示出屏蔽图案、第一有源图案、第一导电图案、第二导电图案和第二有源图案的布局图,图28是示出屏蔽图案、第一有源图案、第一导电图案、第二导电图案、第二有源图案和第三导电图案的布局图。

159.参照图23至图28,根据又一实施例的显示装置40可以包括第一像素结构px1和被设置为与第一像素结构px1相邻的第二像素结构px2。例如,第一像素结构px1和第二像素结构px2可以关于穿过第一像素结构px1和第二像素结构px2的中间的对称线对称。然而,除了屏蔽图案sdp的形状之外,第一像素结构px1和第二像素结构px2可以与包括在显示装置20中的第一像素结构px1和第二像素结构px2基本相同。例如,第一像素结构px1和第二像素结构px2可以包括上述第一有机膜层pi1、第一阻挡层brr1、第二有机膜层pi2、第二阻挡层brr2、缓冲层bfr、第一有源图案1100、第一栅极绝缘层gi1、第一导电图案1200、第二栅极绝缘层gi2、第二导电图案1300、第一层间绝缘层ild1、第二有源图案1400、第三栅极绝缘层gi3、第三导电图案1500、第二层间绝缘层ild2、第四导电图案1600、第一过孔绝缘层via1、第五导电图案1700和第二过孔绝缘层via2。在下文中,将主要描述屏蔽图案sdp的形状。

160.如图23中所示,包括在显示装置40中的屏蔽图案sdp可以设置在第二阻挡层brr2上。在实施例中,屏蔽图案sdp可以具有岛形状。

161.屏蔽图案sdp可以包括第一图案ptn1和第二图案ptn2。第一图案ptn1可以包括第一部分prt1和第二部分prt2。第一图案ptn1和第二图案ptn2可以关于穿过第一图案ptn1和第二图案ptn2的中间的对称线对称。第一图案ptn1和第二图案ptn2可以彼此连接。

162.如图24中所示,第一部分prt1可以与第一有源图案1100叠置。如图25中所示,第一部分prt1可以与第一栅电极1221完全叠置。换句话说,第一部分prt1的尺寸可以大于或等于第一栅电极1221的尺寸。如图26至图28中所示,第二部分prt2可以与第三栅极线1320、第二有源图案1400和第五栅极线1510叠置。

163.屏蔽图案sdp可以对第一有源图案1100进行屏蔽使其免受第二有机膜层pi2的极化的有机材料影响。因此,可以不在第一有源图案1100中形成背沟道,并且可以不改变第一晶体管t1的电特性。因此,可以提高显示装置40的显示质量。

164.另外,屏蔽图案sdp可以对第二有源图案1400进行屏蔽使其免受极化的有机材料影响。因此,可以不在第二有源图案1400中形成背沟道,并且可以不改变第三晶体管t3的电特性。因此,可以提高显示装置40的显示质量。

165.图29至图35是示出根据又一实施例的显示装置的布局图。例如,图29是示出屏蔽图案的布局图,图30是示出屏蔽图案和第一有源图案的布局图,图31是示出屏蔽图案、第一有源图案和第一导电图案的布局图,图32是示出屏蔽图案、第一有源图案、第一导电图案和第二导电图案的布局图,图33是示出屏蔽图案、第一有源图案、第一导电图案、第二导电图案和第二有源图案的布局图,图34是示出屏蔽图案、第一有源图案、第一导电图案、第二导电图案、第二有源图案和第三导电图案的布局图,图35是示出屏蔽图案、第一有源图案、第一导电图案、第二导电图案、第二有源图案、第三导电图案和第五导电图案的布局图。

166.参照图29至图35,根据又一实施例的显示装置50可以包括第一像素结构px1和与第一像素结构px1相邻的第二像素结构px2。例如,第一像素结构px1和第二像素结构px2可以关于穿过第一像素结构px1和第二像素结构px2的中间的对称线对称。然而,除了屏蔽图案sdp的形状之外,第一像素结构px1和第二像素结构px2可以与包括在显示装置20中的第一像素结构px1和第二像素结构px2基本相同。例如,第一像素结构px1和第二像素结构px2可以包括上述第一有机膜层pi1、第一阻挡层brr1、第二有机膜层pi2、第二阻挡层brr2、缓冲层bfr、第一有源图案1100、第一栅极绝缘层gi1、第一导电图案1200、第二栅极绝缘层gi2、第二导电图案1300、第一层间绝缘层ild1、第二有源图案1400、第三栅极绝缘层gi3、第三导电图案1500、第二层间绝缘层ild2、第四导电图案1600、第一过孔绝缘层via1、第五导电图案1700和第二过孔绝缘层via2。在下文中,将主要描述屏蔽图案sdp的形状。

167.如图29中所示,包括在显示装置50中的屏蔽图案sdp可以设置在第二阻挡层brr2上。在实施例中,屏蔽图案sdp可以具有网格结构。

168.屏蔽图案sdp可以包括第一图案ptn1和第二图案ptn2。第一图案ptn1可以包括第一部分prt1、第二部分prt2和第三部分prt3。例如,第二部分prt2可以沿着第二方向d2延伸,第三部分prt3可以沿着第一方向d1延伸。第一图案ptn1和第二图案ptn2可以关于穿过第一图案ptn1和第二图案ptn2的中间的对称线对称。

169.如图30中所示,第一部分prt1可以与第一有源图案1100叠置。如图31中所示,第一部分prt1可以与第一栅电极1221完全叠置。换句话说,第一部分prt1的形状可以与第一栅电极1221的形状基本相同,第一部分prt1的尺寸可以大于或等于第一栅电极1221的尺寸。如图32至图34中所示,第三部分prt3可以与第三栅极线1320、第二有源图案1400和第五栅极线1510叠置。如图35中所示,第二部分prt2可以与高电力电压线1720叠置。例如,第二部分prt2可以沿着高电力电压线1720设置。

170.屏蔽图案sdp可以对第一有源图案1100进行屏蔽使其免受第二有机膜层pi2的极化的有机材料影响。因此,可以不在第一有源图案1100中形成背沟道,并且可以不改变第一晶体管t1的电特性。因此,可以提高显示装置50的显示质量。

171.另外,屏蔽图案sdp可以对第二有源图案1400进行屏蔽使其免受极化的有机材料

影响。因此,可以不在第二有源图案1400中形成背沟道,并且可以不改变第三晶体管t3的电特性。因此,可以提高显示装置50的显示质量。

172.尽管这里已经描述了某些示例性实施例和实施方式,但是其他实施例和修改将通过该描述而明显。因此,发明构思不限于这些实施例,而是限于所附权利要求的更广泛的范围以及对本领域普通技术人员将明显的各种明显的修改和等同布置。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1