平面型SiCMOSFET器件的制作方法

本发明涉及半导体集成电路制造领域,特别是涉及一种平面型sic mosfet器件。

背景技术:

1、sic跟si相比,具有非常优越的材料特性,这主要表现在其禁带宽度是3.2电子伏特(ev),跟硅的1.12相比,高了接近3倍。其临界击穿场强是硅的10倍。如果要实现相同的耐压,sic的漂移区长度可以做到硅的1/10,其掺杂浓度也可以提高几十倍。同时高的禁带宽度,本征载流子浓度低,这使得sic器件即使在250度甚至300度的结温下,其本征载流子的数目依然低于常温下(25度)的si器件本征载流子数目。sic器件的高温漏电得到了大幅降低。限制其工作温度的主要是封装而不是器件本身。

2、基于此sic mosfet得到了越来越广泛的应用,市场前景巨大。

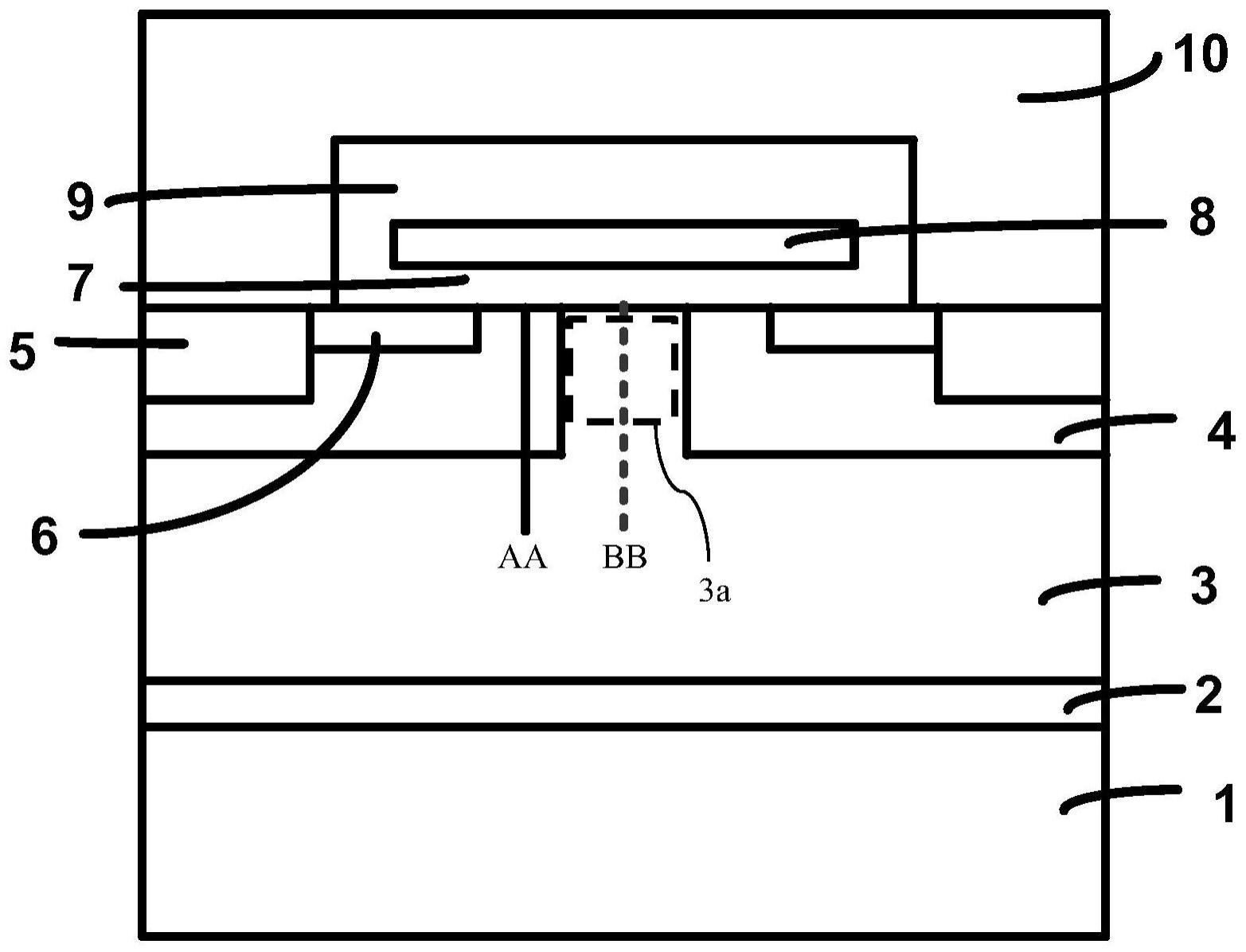

3、如图1所示,是现有平面型sic mosfet器件的剖面结构示意图;以n型sic mosfet为例进行介绍,现有平面型sic mosfet器件包括:

4、n型重掺杂的sic衬底101,sic衬底101的电阻率通常在20mω*cm左右。与之相对的si器件的衬底电阻率可以做到1mω*cm以下。这是因为太高的衬底掺杂浓度会增加器件的缺陷。因此sic衬底101的衬底电阻是远远高于si器件的。为了降低衬底电阻,通常希望把sic衬底101的厚度做的越薄越好。此外,衬底厚度越薄,器件的热阻越低;

5、在sic衬底101上面形成有sic材料形成的n型掺杂的缓冲(buffer)层102,buffer层102的掺杂浓度很高,在1e18/cm3附近;buffer层102是通过外延生长形成,故buffer层102的缺陷密度是优于衬底的。buffer层102的厚度通常在1μm附近。

6、在所述buffer层102表面上形成有n型掺杂的sic外延层103,sic外延层103的掺杂浓度决定了器件的击穿电压。器件的击穿电压越高,sic外延层103的厚度越厚,sic外延层103的掺杂浓度越低。对于目前1200v的sic mosfet,sic外延层103的厚度通常在8μm~13μm之间,sic外延层103掺杂浓度通常在5e15/cm3~2e16/cm3之间。sic外延层103目前通常是单层的,也可以是双层外延。对于双层外延,靠近表面的掺杂浓度高,降低mosfet的jfet效应。

7、在所述sic外延层103中形成有p型掺杂的沟道区104,沟道区104的设计是sicmosfet的难点。这是因为sic mosfet的沟道区104的载流子迁移率很低,通常情况下不到硅器件的1/10;因此我们希望把沟道长度lc做的越短越好。但是为了保证一定的阈值电压,沟道区104的掺杂浓度特别是表面的掺杂浓度不能太高。

8、此外,sic mosfet的漂移区掺杂浓度也大幅提高,漂移区由所述沟道区104外的所述sic外延层103组成,这要求沟道区104的掺杂浓度和沟道长度lc都需要提高,否则会有非常严重的短沟道效应。

9、相邻的所述沟道区104之间的区域通常会具有jfet效应,相邻的所述沟道区104之间的距离wj也是一个难点。沟道区104和n型漂移区之间会有一个耗尽,也就是jfet效应,会降低导电区域。这个距离wj如果太小,jfet效应太严重,器件的比导通电阻会急剧增加。如果距离wj太大,器件的步进(pitch)增加,原胞的密度降低,器件的比导通电阻也会增加。为了在沟道之间距离较小时,依然有比较低的比导通电阻,通常会在增加一个抗jfet注入(anti-jfet implant),抗jfet注入在相邻的所述沟道区104之间形成抗jfet注入区。但是这个jfet注入区会增加栅氧107的电场强度。对于sic mosfet来说,因为sic的临界击穿场强高达3mv/cm以上;栅氧107的材料通常为sio2,此外因为所述sic外延层103和栅氧107的界面处,sic材料和sio2介电常数的差异会使栅氧107的sio2材料内的电场强度会提高2倍以上。这很容易达到或者超过sio2的临界击穿电压。造成器件的损坏或者是长期工作性能的退化。为此,如何对沟道区104进行设计以及相邻沟道区104之间抗jfet区域的掺杂浓度的设计,是一个难点,也是本发明需要解决的问题。总之本发明主要是解决,如何设计合理的道区104的掺杂浓度,降低器件的短沟道效应;以及如何设计抗jfet区域的掺杂浓度,让器件在导通电阻比较低的时候,表面的击穿场强依然能够做到比较低。

10、在所述沟道区104的选定区域的表面区域中形成有n型重掺杂的源区106以及p型重掺杂的体接触区105。体接触区105的掺杂浓度高,可以降低器件寄生三极管的基区电阻,防止器件发生骤回(snapback)。

11、由正面金属层组成的源极金属110通过源区通孔和底部的体接触区105和所述源区106连接,所述源区通孔和底部的体接触区105和所述源区106实现欧姆接触,所述沟道区104则通过所述体接触孔105连接到所述源区通孔和所述源极金属110。

12、栅氧107通常是sio2。sic mosfet的驱动电亚通常需要超过18v,甚至达到20v。这么高的驱动电压要求的栅氧厚度通常比较厚。目前sic平面型mosfet,栅氧的厚度通常是也就是50nm。

13、栅极导电材料层108形成于栅氧107的表面上,由栅氧107和栅极导电材料层108叠加形成栅极结构。被栅极结构所覆盖的所述沟道区104的表面会在器件导通时形成导电沟道。栅极导电材料层108通常采用n型重掺杂的多晶硅栅。

14、层间膜109实现源极金属10和栅极导电材料层108之间的隔离。层间膜109通常也是sio2,厚度通常在0.4μm~2.0μm之间。

技术实现思路

1、本发明所要解决的技术问题是提供一种平面型sic mosfet器件,沟道区的掺杂既能满足阈值电压的要求,又能满足降低器件的短沟道效应的要求,同时,抗jfet区既能满足降低器件的比导通电阻的要求,又能防止增加抗jfet表面的电场强度从而增加器件的可靠性。

2、为解决上述技术问题,本发明提供的平面型sic mosfet器件包括:

3、形成于第一导电类型掺杂的sic外延层的选定区域中的沟道区,被栅极结构所覆盖的所述沟道区的表面用于形成导电沟道;所述沟道区外的所述sic外延层组成漂移区。

4、在两个相邻的所述沟道区之间的所述漂移区表面形成有抗jfet区。

5、所述栅极结构也延伸到所述抗jfet区的表面上。

6、所述栅极结构由形成栅介质层和栅极导电材料层叠加而成。

7、所述沟道区由二个以上注入峰值位置不同的第二导电类型掺杂的第一离子注入区叠加而成。

8、所述抗jfet区由一个以上注入峰值位置不同的第一导电类型掺杂的第二离子注入区叠加而成。

9、所述沟道区中的各所述第一离子注入区设置为:

10、注入峰值位置越深,注入峰值越大;注入峰值位置越浅,注入峰值越小。

11、平面型sic mosfet器件的阈值电压由注入峰值位置最浅的所述第一离子注入区调节,由注入峰值位置次浅以下的各所述第一离子注入区来降低短沟道效应。

12、所述抗jfet区的各所述第二离子注入区的注入峰值位置和注入剂量设置为:

13、各所述第二离子注入区的注入峰值位置深于所述沟道区中的最浅的注入峰值位置,以降低所述栅介质层和所述sic外延层界面处的电场强度。

14、各所述第二离子注入区的注入峰值位置浅于所述沟道区中的最深的注入峰值位置,以使器件的击穿电压得到保证。

15、各所述第二离子注入区的注入峰值大于所述沟道区中的注入峰值位置最浅的所述第一离子注入区的注入峰值,各所述第二离子注入区的注入峰值小于所述沟道区中的注入峰值位置最深的所述第一离子注入区的注入峰值,以实现降低jfet效应从而降低器件的比导通电阻。

16、进一步的改进是,所述沟道区由二个注入峰值位置不同的第二导电类型掺杂的第一离子注入区叠加而成。

17、进一步的改进是,所述抗jfet区由一个第一导电类型掺杂的第二离子注入区组成。

18、进一步的改进是,所述抗jfet区由二个注入峰值位置不同的第一导电类型掺杂的第二离子注入区叠加而成,两个所述第二离子注入区的注入峰值大小相同或不同。

19、进一步的改进是,所述沟道区由三个注入峰值位置不同的第二导电类型掺杂的第一离子注入区叠加而成。

20、进一步的改进是,所述抗jfet区由一个第一导电类型掺杂的第二离子注入区组成。

21、进一步的改进是,所述抗jfet区的所述第二离子注入区的注入峰值位置位于所述沟道区的最浅注入峰值位置和次浅注入峰值位置之间;或者,所述抗jfet区的所述第二离子注入区的注入峰值位置位于所述沟道区的次浅注入峰值位置和最深注入峰值位置之间。

22、进一步的改进是,在所述沟道区的选定区域的表面区域中还形成有第一导电类型重掺杂的源区,所述栅极结构也延伸到所述源区表面上。

23、进一步的改进是,在所述沟道区的选定区域的表面区域中还形成有第二导电类型重掺杂的体接触区。

24、进一步的改进是,所述体接触区和所述源区的表面通过穿过层间膜的源接触孔连接到由正面金属层组成的源极。

25、进一步的改进是,所述平面型sic mosfet器件包括多个器件单元;

26、由2个相邻的所述器件单元组成一个原胞,在所述原胞中,两个所述器件单元共用所述抗jfet区,两个所述器件单元的沟道区对称设置在所述抗jfet区的两侧,两个所述器件单元的所述栅极结构在所述抗jfet区的表面上方连接形成一个整体结构。

27、进一步的改进是,所述平面型sic mosfet器件包括多个器件单元;

28、由2个相邻的所述器件单元组成一个原胞,在所述原胞中,两个所述器件单元共用所述抗jfet区,两个所述器件单元的沟道区对称设置在所述抗jfet区的两侧,两个所述器件单元的所述栅极结构在所述抗jfet区的表面上方具有间隔,以降低输入电容。

29、进一步的改进是,所述平面型sic mosfet器件包括多个器件单元,由1个所述器件单元组成一个原胞;

30、在各所述沟道区的顶部仅设置一个所述栅极结构并会形成一个所述导电沟道;

31、各所述器件单元的所述栅极结构的第二侧从所述沟道区的第二侧延伸到邻近的所述抗jfet区表面上且和邻近的所述沟道区的第一侧具有间隔;

32、各所述器件单元的所述栅极结构的第一侧和所述沟道区的第一侧之间形成有所述源区和所述体接触区。

33、进一步的改进是,所述sic外延层形成于sic衬底上且所述sic外延层和所述sic衬底之间具有第一导电类型掺杂的缓冲层。

34、进一步的改进是,平面型sic mosfet器件为n型器件,第一导电类型为n型,第二导电类型为p型;或者,所述平面型sic mosfet器件为p型器件,第一导电类型为p型,第二导电类型为n型。

35、进一步的改进是,p型掺杂杂质包括铝,n型掺杂杂质包括氮。

36、本发明中,沟道区和抗jfet区都是采用离子注入区组成,本发明对沟道区和抗jfet区的离子注入区进行了特别的设置,主要是:

37、将沟道区的离子注入区分成多个第一离子注入区叠加而成,这样各个第一离子注入区的注入峰值的大小和位置能分别调节,而本发明则根据满足器件的阈值电压要求和降低短沟道效应的要求分别设置各个第一离子注入区的注入峰值的大小和位置,最后能使沟道区的掺杂既能满足阈值电压的要求,又能满足降低器件的短沟道效应的要求。

38、而抗jfet区的第二离子注入区的注入峰值的大小和位置则是根据沟道区的各第一离子注入区的注入峰值的大小和位置进行设置,在保证抗jfet区的第二离子注入区的注入峰值位置位于沟道区的最浅的第一离子注入区的注入峰值位置底部的条件下,能使抗jfet区的表面区域的电场强度降低,也即能降低栅介质层和sic外延层界面处的电场强度,从而能提高器件的可靠性;在保证抗jfet区的第二离子注入区的注入峰值位置位于沟道区的最深的第一离子注入区的注入峰值位置之上的条件下,能使器件的击穿电压得到保证;抗jfet区的第二离子注入区的注入峰值的大小并结合注入峰值的位置设置则能满足抗jfet效应的要求,使器件的比导通电阻降低。

39、另外,在半导体制造领域中,离子注入工艺对应的注入峰值是指离子注入后在注入区域中的掺杂浓度最大值,注入峰值的大小也就是注入区域中的掺杂浓度最大值本身,和离子注入的注入剂量相对应于;注入峰值的位置也即注入区域中的掺杂浓度最大值对应的深度位置,也简称为注入峰值位置,和离子注入的注入能量相对应。

- 还没有人留言评论。精彩留言会获得点赞!