半导体装置的制作方法

半导体装置

1.相关申请

2.本技术享有以日本专利申请2021-150262号(申请日:2021年9月15日)为基础申请的优先权。本技术通过参考此基础申请包括基础申请的所有内容。

技术领域

3.实施方式涉及半导体装置。

背景技术:

4.功率转换器等中使用的半导体装置要求高可靠性。例如,对于高电压、高电流的破坏耐量大是重要的。

技术实现要素:

5.实施方式提供一种提高了可靠性的半导体装置。

6.实施方式的半导体装置具备半导体部、第一电极、第二电极以及控制电极。所述半导体部包含第一导电型的第一半导体层、第二导电型的第二半导体层、所述第一导电型的第三半导体层、所述第二导电型的第四半导体层、以及所述第二导电型的第五半导体层。所述第一电极设置于所述半导体部的背面上,所述第二电极设置于所述半导体部的表面上。所述第一半导体层在所述第一电极与所述第二电极之间延伸,所述第二半导体层设置于所述第一半导体层与所述第二电极之间。所述第三半导体层部分地设置于所述第二半导体层与所述第二电极之间。所述第四半导体层设置于所述第一半导体层与所述第一电极之间。所述控制电极配置于在所述半导体部设置的沟槽的内部,位于所述半导体部与所述第二电极之间,通过第一绝缘膜而与所述半导体部电绝缘,并通过第二绝缘膜而与所述第二电极电绝缘。另外,所述控制电极构成为,从所述半导体部的所述表面侧延伸到所述第一半导体层中,所述第二半导体层经由所述第一绝缘膜与所述控制电极相对,所述第三半导体层与所述第一绝缘膜相接。进而,所述半导体部包含有源区域和终端区域,所述有源区域包含所述控制电极、所述第二半导体层及所述第三半导体层,所述终端区域包围所述有源区域。所述第五半导体层在所述终端区域中设置于所述第一半导体层中,在沿着所述第一半导体层与所述第四半导体层的边界的第一方向上延伸。在从所述第一电极朝向所述第二电极的第二方向上,从所述第五半导体层到所述半导体部的所述表面的第一距离比从所述第五半导体层到所述半导体部的所述背面的第二距离长。

附图说明

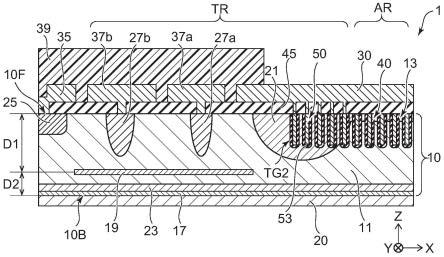

7.图1是表示实施方式的半导体装置的示意剖视图。

8.图2是表示实施方式的半导体装置的另一示意剖视图。

9.图3是表示实施方式的半导体装置的示意俯视图。

10.图4是表示实施方式的半导体装置的结构的示意图。

11.图5的(a)~(d)是表示实施方式的半导体装置的制造过程的示意剖视图。

12.图6的(a)及(b)是表示实施方式的半导体装置的特性的示意图。

13.图7的(a)及(b)是表示实施方式的半导体装置的特性的示意剖面图。

14.图8的(a)及(b)是表示实施方式的半导体装置的特性的另一示意剖视图。

15.图9是表示实施方式的半导体装置的特性的曲线图。

16.图10是表示实施方式的半导体装置的另一特性的曲线图。

17.图11的(a)及(b)是表示实施方式的半导体装置的又一特性的曲线图。

18.图12是表示实施方式的半导体装置的其他特性的曲线图。

19.图13的(a)及(b)是表示实施方式的变形例的半导体装置的示意图。

具体实施方式

20.以下,参照附图对实施方式进行说明。对附图中的相同部分标注相同的附图标记并适当省略其详细的说明,对不同的部分进行说明。另外,附图是示意性或概念性的,各部分的厚度与宽度的关系、部分间的大小的比率等未必与现实的相同。另外,即使在表示相同部分的情况下,也存在根据附图而彼此的尺寸、比率不同地进行表示的情况。

21.进而,使用各图中所示的x轴、y轴及z轴,对各部分的配置及结构进行说明。x轴、y轴、z轴相互正交,分别表示x方向(第一方向)、y方向、z方向(第二方向)。另外,有时将z方向作为上方并将其相反方向作为下方进行说明。

22.实施方式中记载的半导体层的杂质浓度例如能够通过tof-sims(time of flight-and ion mass spectrometry)进行测定。另外,杂质浓度的相对高低例如也能够根据利用scm(scanning capacitance microscopy)求出的载流子浓度的高低来进行判断。另外,杂质区域的深度、厚度等距离例如能够通过tof-sims来求出。另外。杂质区域的深度、厚度、宽度、间隔等距离例如能够根据scm像和afm图像(atomic force microscope image)的合成图像求出。

23.图1及图2是表示实施方式的半导体装置1的示意剖视图。半导体装置1是igbt(insulated gate bipolar transistor:绝缘栅双极晶体管)。半导体装置1包含有源区域ar和终端区域tr。图1是表示有源区域ar的结构的剖视图。图2是表示终端区域tr的结构的剖视图。

24.如图1所示,半导体装置1包含半导体部10、第一电极20、第二电极30以及控制电极40。第一电极20设置于半导体部10的背面10b上。第二电极30设置于半导体部10的表面10f之上。半导体部10例如是硅。第一电极20例如是集电极电极。第二电极30例如是发射极电极。

25.控制电极40配置于在半导体部10的表面侧设置的沟槽tg1的内部。控制电极40设置于半导体部10与第二电极30之间。控制电极40通过第一绝缘膜43而与半导体部10电绝缘。另外,控制电极40通过第二绝缘膜45而与第二电极30电绝缘。第一绝缘膜43例如是栅极绝缘膜。第二绝缘膜45例如是层间绝缘膜。第一绝缘膜43及第二绝缘膜45例如是硅氧化膜。

26.如图1所示,半导体部10例如包含第一导电型的第一半导体层11、第二导电型的第二半导体层13、第一导电型的第三半导体层15以及第二导电型的第四半导体层17。以下,将第一导电型设为n型并将第二导电型设为p型来进行说明。

27.第一半导体层11在第一电极20与第二电极30之间延伸。第一半导体层11例如是n型基底层。控制电极40从半导体部10的表面侧延伸到第一半导体层11中。

28.第二半导体层13设置于第一半导体层11与第二电极30之间。第二半导体层13例如是p型基底层。第二半导体层13以隔着第一绝缘膜43与控制电极40相对的方式设置。

29.第三半导体层15部分地设置于第二半导体层13与第二电极30之间。第三半导体层15例如是n型发射极层。第三半导体层15以与第一绝缘膜43相接的方式设置。第二电极30与第二半导体层13以及第三半导体层15电连接。

30.第四半导体层17设置于第一半导体层11与第一电极20之间。第四半导体层17例如是p型集电极层。第一电极20与第四半导体层17电连接。

31.如图2所示,半导体部10还包含第二导电型的第五半导体层19、第二导电型的第六半导体层21、第一导电型的第七半导体层23、第一导电型的第八半导体层25以及第二导电型的第九半导体层27a及27b。

32.第六半导体层21设置于半导体部10的表面侧,位于有源区域ar与终端区域tr的边界。第六半导体层21在从第一电极20朝向第二电极30的方向、例如z方向上设置于第一半导体层11与第二电极30之间。第六半导体层21例如是p型保护环。第六半导体层21以与第二半导体层13相连的方式设置。

33.第五半导体层19在终端区域tr中设置于第一半导体层11中。第五半导体层19设置为在沿着半导体部10的背面10b的方向例如x方向上延伸的板状。在此,“板状”是指例如沿x方向及y方向延伸、且z方向的厚度比x方向及y方向的长度薄的形状。

34.第五半导体层19例如以在z方向上从第五半导体层19到半导体部10的表面10f的第一距离d1比从第五半导体层19到半导体部10的背面10b的第二距离d2长的方式设置。另外,第五半导体层19设置于与第二导电型的第四半导体层17分离的位置,在第一导电型的第一半导体层11中以成为浮游电位的方式设置。

35.第七半导体层23设置于第一半导体层11与第四半导体层17之间。第七半导体层23例如是n型缓冲层。第七半导体层23包含浓度比第一半导体层11的第一导电型杂质的浓度高的第一导电型杂质,与第一半导体层11电连接。第五半导体层19设置于与第七半导体层23分离的位置。

36.此外,在上述的例子中,第四半导体层17以从有源区域ar向终端区域tr延伸的方式设置,但实施方式并不限定于此。例如,第四半导体层17也可以是不在终端区域tr中延伸、而第七半导体层23在终端区域tr中与第一电极20连接的结构。

37.第八半导体层25在半导体部10的表面侧设置于与第六半导体层21分离的位置。第八半导体层25是所谓的eqpr(equivalent potential ring)层。第八半导体层25包含浓度比第一半导体层11的第一导电型杂质的浓度高的第一导电型杂质,与第一半导体层11电连接。

38.第九半导体层27a及27b在半导体部10的表面侧设置于第六半导体层21与第八半导体层25之间。第九半导体层27a及27b例如是p型保护环。第九半导体层27a及27b相互分离,设置于与第六半导体层21以及第八半导体层25分离的位置。第九半导体层27a设置于第六半导体层21与第九半导体层27b之间。第九半导体层27a及27b并不限定于该例。例如,也可以是设置有3个以上的第九半导体层的结构。

39.第一半导体层11包含位于第五半导体层19与第九半导体层27a之间以及第五半导体层19与第九半导体层27b之间的部分。另外,第一半导体层11包含分别位于第九半导体层27a及27b之间、第六半导体层21与第九半导体层27a之间、第八半导体层25与第九半导体层27b之间的部分。

40.半导体装置1还具备第三电极35、第四电极37a、第四电极37b以及第五电极50。第三电极35、第四电极37a及37b在终端区域tr中例如隔着第二绝缘膜45而设置于半导体部10上。第二绝缘膜45沿着半导体部10的表面10f从有源区域ar向终端区域tr延伸。实施方式并不限定于该例,例如,终端区域tr的表面也可以被与第二绝缘膜45不同的层间绝缘膜覆盖。另外,也可以在第二绝缘膜45之上设置其他的层间绝缘膜。进而,也可以与第九半导体层27的数量相应地设置3个以上的第四电极37。

41.第三电极35设置于第八半导体层25之上。第三电极35例如是eqpr电极。第三电极35与第八半导体层25电连接。

42.第四电极37a及37b设置于第二电极30与第三电极35之间。第四电极37a及37b相互分离,与第二电极30以及第三电极35分离地设置。第四电极37a及37b例如是场板电极。

43.第四电极37a设置于第九半导体层27a之上。第四电极37b设置于第九半导体层27b之上。第四电极37a及37b例如经由设置于第二绝缘膜45的接触孔而与第九半导体层27a及27b分别电连接。

44.第五电极50设置于半导体部10与第二电极30之间。第五电极50配置于在半导体部10的表面侧设置的沟槽tg2的内部,并通过第三绝缘膜53而与半导体部10电绝缘。第三绝缘膜53例如是硅氧化膜。第五电极50例如在第六半导体层21中延伸,与第二电极30电连接。另外,第五电极50也可以以在第九半导体层27a及27b之中延伸的方式设置。

45.图3是表示实施方式的半导体装置1的示意俯视图。图3是表示半导体部10的表面10f的俯视图。

46.如图3所示,终端区域tr以包围有源区域ar的方式设置。有源区域ar包含第二半导体层13、第三半导体层15和控制电极40。终端区域tr包含第五半导体层19、第六半导体层21、第八半导体层25、第九半导体层27a及27b(参照图2)。如图3所示,第五半导体层19、第六半导体层21、第八半导体层25、第九半导体层27a及27b在x方向或者y方向上延伸。

47.第六半导体层21以沿着有源区域ar与终端区域tr的边界包围有源区域ar的方式设置。第九半导体层27a及27b分别以包围第六半导体层21的方式设置,在第六半导体层21的外侧包围有源区域ar。

48.第五半导体层19在第六半导体层21与第八半导体层25之间以包围有源区域ar的方式设置。第五半导体层19以在与半导体部10的表面10f平行的俯视观察时与第六半导体层21以及第八半导体层25分离的方式设置。在俯视半导体部10时,第五半导体层19以从第八半导体层25例如离开5微米(μm)的方式设置。

49.另外,图3是例示,第五半导体层19并不限定于上述的方式。第五半导体层19例如不需要是包围有源区域ar的一个环状的图案,也可以分割为多个部分。另外,第五半导体层19的宽度不需要是均匀的,也可以在有源区域ar的角部比其他部分更宽地形成。

50.图4是表示实施方式的半导体装置的结构的示意图。图4示出了半导体部10的z方向上的杂质浓度分布的一例。图4表示第一半导体层11及第七半导体层23的第一导电型杂

质的浓度分布。另外,图4表示第四半导体层17及第五半导体层19的第二导电型杂质的浓度分布。

51.如图4所示,第五半导体层19的第二导电型杂质的峰值浓度比第一半导体层11的第一导电型杂质的浓度高。另外,第五半导体层19的第二导电型杂质的峰值浓度比第四半导体层17的第二导电型杂质的浓度低。

52.第一半导体层11的第一导电型杂质的浓度例如处于1

×

10

12

~1

×

10

14

cm-3

的浓度范围。第四半导体层17的第二导电型杂质的浓度例如为1

×

10

19

cm-3

。第五半导体层19的第二导电型杂质的浓度例如为1

×

10

16

cm-3

。第七半导体层23的第一导电型杂质的浓度例如为1

×

10

17

~1

×

10

18

cm-3

。

53.另外,第五半导体层19的第二导电型杂质的峰值浓度比第九半导体层27a及27b的第二导电型杂质的浓度(未图示)低。第九半导体层27a及27b的第二导电型杂质的浓度例如为1

×

10

19

cm-3

。第五半导体层19的第二导电型杂质的峰值浓度低于第四半导体层17的第二导电型杂质的浓度以及第九半导体层27a及27b的第二导电型杂质的浓度的理由是,在后述的半导体装置1从接通状态转移到断开状态时,第五半导体层19耗尽,第四半导体层17以及第九半导体层27a及27b不耗尽。

54.从第五半导体层19到半导体部10的表面10f的z方向的第一距离d1是从第五半导体层19中的第二导电型杂质的浓度峰的位置到半导体部10的表面10f的距离。另外,从第五半导体层19到半导体部10的背面10b的z方向的第二距离d2是从第五半导体层19中的第二导电型杂质的浓度峰的位置到半导体部10的背面10b的距离。

55.半导体部10的z方向上的厚度、即从半导体部10的背面10b到表面10f的距离例如为50μm以上且500μm以下。第四半导体层17的z方向的厚度例如为0.2μm。第七半导体层23的z方向的厚度例如为1μm。第五半导体层19与第七半导体层23之间的z方向的距离例如为7μm。另外,第五半导体层19的z方向的厚度例如为4μm。即,第二距离d2例如为10μm。

56.接着,参照图5的(a)~(d),说明半导体装置1的制造方法。图5的(a)~(d)是表示实施方式的半导体装置1的制造过程的示意剖视图。

57.如图5的(a)所示,在半导体部10的表面侧形成第二半导体层13、第六半导体层21、第八半导体层25、第九半导体层27a、第九半导体层27b、控制电极40以及第五电极50。半导体部10例如为n型硅晶片。

58.在半导体部10的表面侧形成了沟槽tg1及tg2之后,形成覆盖其内表面的第一绝缘膜43(参照图1)及第三绝缘膜53。第一绝缘膜43及第三绝缘膜53例如是通过对半导体部10进行热氧化而形成的硅氧化膜。接着,在沟槽tg1及tg2的内部形成控制电极40及第五电极50。控制电极40及第五电极50例如是具有导电性的多晶硅。

59.进而,在半导体部10的表面侧离子注入第二导电型杂质、例如硼(b),由此形成第二半导体层13、第六半导体层21、第九半导体层27a及27b。第二半导体层13、第六半导体层21、第九半导体层27a及27b通过对被离子注入的第一导电型杂质进行热处理而使其活化及扩散而形成。

60.接着,在半导体部10的表面侧离子注入第一导电型杂质、例如磷(p),由此形成第三半导体层15(参照图1)及第八半导体层25。第三半导体层15及第八半导体层25通过利用热处理使被离子注入的第一导电型杂质活化而形成。

61.进而,在半导体部10的表面10f上形成第二绝缘膜45。第二绝缘膜45例如是使用cvd(chemical vapor deposition:化学气相沉积)形成的硅氧化膜。在第二绝缘膜45形成有分别与第五电极50、第九半导体层27a及27b连通的接触孔。接着,例如通过蚀刻或研磨使半导体部10变薄至规定的厚度。

62.如图5的(b)所示,在半导体部10的背面侧,部分地离子注入第一导电型的杂质、例如硼(b)。第一导电型杂质在终端区域tr中被离子注入到规定的深度。例如,硼离子b

2+

以5mev的加速能量被进行离子注入。

63.进而,将成为第四半导体层17以及第七半导体层23的第二导电型杂质例如硼(b)以及第一导电型杂质例如磷(p)离子注入到半导体部10的背面侧。接着,被离子注入的杂质例如通过1000℃以下的热处理而被活化,如图5的(c)所示,形成第四半导体层17、第五半导体层19及第七半导体层23。

64.如图5的(d)所示,在半导体部10的背面上形成第一电极20。第一电极20例如是包含钛(ti)及铝(al)的金属层。另外,在半导体部10的表面侧形成第二电极30、第三电极35、第四电极37a及37b。第二电极30、第三电极35、第四电极37a及37b例如是包含氮化钛(tin)、钨(w)以及铝(al)的金属层。进而,在半导体部10的终端区域tr的表面侧形成树脂层39。树脂层39以覆盖第四电极37a及37b的方式设置。树脂层39例如是聚酰亚胺树脂。

65.半导体装置1通过在第一电极20与第二电极30之间施加规定的电压(集电极电压),并在第二电极30与控制电极40之间施加控制电压(栅极电压)来进行动作。

66.例如,当控制电压高于控制电极40的阈值时,在第二半导体层13与第一绝缘膜43的界面感应出第一导电型的反型层。由此,从第二电极30经由第三半导体层15以及反型层向第一半导体层11注入第一导电型载流子(电子)。与此对应,从第四半导体层17经由第七半导体层23向第一半导体层11注入第二导电型载流子(空穴)。

67.第一导电型载流子从第一半导体层11经由第七半导体层23以及第四半导体层17向第一电极20排出。另外,第二导电型载流子从第一半导体层11经由第二半导体层13向第二电极30排出。由此,成为在第一电极20与第二电极30之间流动电流(集电极电流)的导通状态。

68.另一方面,若控制电压低于控制电极40的阈值,则在第二半导体层13与第一绝缘膜43之间感应出的反型层消失。因此,从第二电极30向第一半导体层11的第一导电型载流子的注入停止,从第一电极20向第一半导体层11的第二导电型载流子的注入也停止。之后,第一导电型载流子从第一半导体层11向第一电极20的排出以及第二导电型载流子从第一半导体层11向第二电极30的排出继续,第一半导体层11被耗尽化。由此,半导体装置1成为截止状态。以下,对半导体装置1从接通状态向断开状态转移(关断)后的特性进行说明。

69.图6是表示实施方式的半导体装置1的特性的示意图。图6表示半导体装置1关断时的终端区域tr的表面10f侧附近的电场分布。

70.如图6所示,终端区域tr的电场分布例如在第六半导体层21的外缘21e、第九半导体层27a的外缘27ae以及第九半导体层27b的外缘27be分别具有峰值。

71.这样,通过以包围有源区域ar的方式设置第九半导体层27a及27b,由此能够使终端区域tr的电场在横向上伸长。由此,能够缓和与有源区域ar相连的第六半导体层21的外缘21e的电场集中,提高终端区域tr的耐压。

72.进而,通过在第一半导体层11中设置第五半导体层19,由此使第九半导体层27a的外缘27ae的电场强度高于第六半导体层21的外缘21e的电场强度及第九半导体层27b的外缘27be的电场强度。

73.图7的(a)及(b)是表示实施方式的半导体装置1的特性的示意剖视图。图7的(a)表示比较例的半导体装置2的雪崩击穿时的电子电流ie的路径。在半导体装置2的终端区域未设置第五半导体层19。图7的(b)表示半导体装置1的雪崩击穿时的电子电流ie的路径。

74.在半导体装置1及2关断时,若使在第一电极20与第二电极30之间施加的电压vce上升,则例如在终端区域tr产生雪崩击穿。雪崩击穿在终端区域tr中的电场强度高的部分产生。如图6所示,如果第九半导体层27a的外缘27ae的电场强度比其他部分高,则在第九半导体层27a的外缘27ae产生雪崩击穿。换言之,第九半导体层27a的外缘27ae成为击穿点。

75.在图7的(a)所示的半导体装置2中,由于雪崩击穿而产生的电子电流ie从第九半导体层27a的外缘27ae通过第七半导体层23以及第四半导体层17而流向第一电极20。

76.在图7的(b)所示的半导体装置1中,电子电流ie避开第五半导体层19而向第八半导体层25的方向流动。因此,电子电流ie的路径变长,电阻变大。

77.图8的(a)及(b)是表示实施方式的半导体装置1的特性的另一示意剖视图。图8的(a)表示比较例的半导体装置2的雪崩击穿时的电子电流ie的路径。图8的(b)表示半导体装置1的雪崩击穿时的电子电流ie的路径。

78.在图8的(a)及(b)中,表示第一半导体层11中的电流密度。显示中的颜色的浓淡表示电流密度的大小关系。如该图中的箭头所示,电子电流ie沿着电流密度高的区域流动。

79.图9是表示实施方式所涉及的半导体装置1以及2的特性的示意剖视图。图9是表示关断时的电压/电流特性的曲线图。横轴是在第一电极20与第二电极30之间施加的电压vce。纵轴是在第一电极20与第二电极30之间流动的电流ice。图9中的“eb”表示半导体装置1的特性,“ce”表示半导体装置2的特性。

80.如图9所示,在半导体装置2中,使电压vce上升,若达到击穿电压vb1则产生雪崩击穿。此时,电流ice流动,并且第一半导体层11中的空间电荷(电子及空穴)的密度增加。因此,第一半导体层11中的电流路径的电阻变小,发生电压vce下降的所谓的骤回(snapback)。若发生骤回,则电流ice的上升加速,有时因过电流而导致元件破坏。

81.在半导体装置1中,若电压vce达到击穿电压vb2,则产生雪崩击穿。进而,随着电压vce的上升,电流ice也逐渐上升。若电流ice达到isnp,则电压vce开始降低,发生骤回。

82.在半导体装置1中,电子电流ie的路径变长,其电阻变大。因此,在雪崩击穿刚开始之后,电压vce不会降低,在电流ice达到isnp的电平之后,发生骤回。即,电子电流ie的路径中的电阻作为所谓的镇流电阻发挥功能,能够抑制电流ice的加速上升。这样,在半导体装置1中,与半导体装置2相比,击穿电压vb降低,但能够抑制骤回。换言之,在半导体装置1中,能够提高转折(break over)耐量。

83.图10是表示实施方式的半导体装置1的其他特性的曲线图。图10是表示第五半导体层19的第二导电型杂质的浓度与击穿电压vb的关系的曲线图。横轴是第五半导体层19的杂质浓度。纵轴是击穿电压vb。

84.图10中的3个曲线图将从半导体部10的背面10b到第五半导体层19的第二距离d2作为参数进行表示。例如,在第二距离d2为5μm以及10μm的情况下,在第五半导体层19的杂

质浓度为5

×

10

15

cm-3

以下的区域中,击穿电压vb大致恒定。若第五半导体层19的杂质浓度超过5

×

10

15

cm-3

,则击穿电压vb降低。换言之,若第五半导体层19的杂质浓度超过5

×

10

15

cm-3

,则电子电流ie避开第五半导体层19而流动,能够提高转折耐量。

85.另一方面,在d2为30μm的情况下,击穿电压vb随着第五半导体层19的杂质浓度的上升而变高,当第五半导体层19的杂质浓度超过7

×

10

15

cm-3

时,击穿电压vb降低。

86.图11的(a)及(b)是表示实施方式的半导体装置1的又一特性的曲线图。图11的(a)是表示从半导体部10的背面10b到第五半导体层19的第二距离d2与击穿电压vb的关系的曲线图。图11的(a)的纵轴为击穿电压vb。图11的(b)是表示第二距离d2与isnp的关系的图表。图11的(b)的纵轴是未设置第五半导体层19的情况下的isnp0与isnp的比。

87.如图11的(a)所示,击穿电压vb随着第二距离d2变长而变高。另一方面,如图11的(b)所示,当第二距离d2大于10μm时,isnp急剧降低。若isnp变小,则容易发生骤回,转折(break over)耐量降低(参照图9)。即,若第二距离d2超过10μm,则失去提高转折耐量的效果。因此,第二距离d2优选为10μm以下。此外,第二距离d2被设置为能够获得期望的击穿电压vb。

88.图12是表示实施方式的半导体装置1的其他特性的曲线图。图12是表示被蓄积在终端区域tr中的外部电荷与击穿电压vb之间的关系的曲线图。横轴为电荷量,纵轴为击穿电压vb。

89.在覆盖终端区域tr的树脂层39(参照图2)中,例如从外部侵入的金属离子容易蓄积。由这样的金属离子引发的外部电荷对终端区域tr中的电场分布产生影响。例如,若在第三电极35与第四电极37b之间蓄积正电荷,则终端区域tr中的电场的横向的伸长被抑制。因此,第九半导体层27b的外缘27be(参照图6)中的电场强度上升,存在击穿电压vb降低的情况。

90.图12中所示的“eb”表示半导体装置1的特性。另外,“ce”表示比较例的半导体装置2(参照图7的(a))的特性。

91.如图12所示,在半导体装置2中,若正电荷的量变多,则击穿电压vb降低。与此相对,在半导体装置1中,即使正电荷的量变多,击穿电压vb也不会降低。即,在半导体装置1中,通过设置第五半导体层19,能够抑制第九半导体层27b的外缘27be处的电场的上升。

92.这样,在半导体装置1中,能够提高充电(charge)鲁棒性,防止终端区域tr中的耐压的降低。

93.图13的(a)及(b)是表示实施方式的变形例的半导体装置3的示意图。图13的(a)是表示半导体装置3的终端区域tr的结构的剖视图。图13的(b)表示半导体部10的杂质浓度分布。横轴是从半导体部10的背面10b起的深度。纵轴为杂质浓度。

94.如图13的(a)所示,第一半导体层11包含第一区域11a及第二区域11b。第一区域11a例如是n型基底区域。第二区域11b例如是n型缓冲区域。第二区域11b设置于第一区域11a与第四半导体层17之间。第五半导体层19设置于第二区域11b中。第二区域11a例如通过对半导体部10的背面侧进行质子照射而形成(参照图5的(b))。

95.如图13的(b)所示,第二区域11b包含浓度比第一区域11a的第一导电型杂质的浓度高的第一导电型杂质。第二区域11b例如从半导体部10的背面10b形成至例如20μm的深度。第二区域11b中的第二导电型杂质的深度方向上的浓度分布例如具有多个浓度峰。第五

半导体层19设置于第二区域11b中的第二导电型杂质的浓度峰之间。

96.第二区域11b的多个浓度峰包括位于第四半导体层17与第五半导体层19之间的第一峰和位于第一区域11a与第五半导体层19之间的第二峰。第一峰处的第二导电型杂质的浓度比第五半导体层19的第二导电型杂质的浓度高。另外,第二峰处的第二导电型杂质的浓度比第五半导体层19的第二导电型杂质的浓度低。

97.另外,第二区域11b也可以形成为第二导电型杂质的分布具有1个浓度峰。在该情况下,第五半导体层19设置于第二导电型杂质的浓度峰与第四半导体层17之间。

98.在该例子中,也是通过在终端区域tr设置第五半导体层19,能够提高转折耐量,提高充电鲁棒性。

99.对本发明的几个实施方式进行了说明,但这些实施方式是作为例子而提出的,并不意图限定发明的范围。这些新的实施方式能够以其他各种方式实施,在不脱离发明的主旨的范围内,能够进行各种省略、置换、变更。这些实施方式及其变形包含在发明的范围或主旨内,并且包含在权利要求书所记载的发明及其均等的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1