一种基于SIP封装的数字信号处理器的制作方法

一种基于sip封装的数字信号处理器

技术领域

1.本实用新型属于数字信号处理技术领域,具体地说,是涉及一种基于sip封装的数字信号处理器。

背景技术:

2.dsp(数字信号处理器)是由大规模或超大规模集成电路芯片组成的用来完成高速实时数字信号处理任务的处理器。

3.sip封装(system in a package系统级封装)是一种电子器件封装方案,将多种功能芯片,包括处理器、存储器等功能芯片集成在一个封装内,从而实现一个基本完整的功能。sip封装与soc(system on a chip系统级芯片)相对应,不同的是系统级封装是采用不同芯片进行并排或叠加的封装方式,而soc则是高度集成的芯片产品。

4.数字信号处理器d20101属于单核架构,客户普遍采用板载多颗d20101板间和板内走线互联来提高数据通信速率和数据处理能力;链路口属于高速接口,对pcb走线要求高,时钟和数据走线要保持等长,受制于板卡结构和相关器件的布局,线宽、线距等客观因素存在,等长和阻抗是pcb设计中比较困难的点,使得系统性能遇到瓶颈。

技术实现要素:

5.本实用新型的目的在于提供一种基于sip封装的数字信号处理器,通过并排方式将四颗dsp组装到一起,四颗dsp之间通过链路口互联,封装内部走线短,走线密度高,稳定性好,节省了空间并提高系统整体带宽和计算能力,并保留单dsp的链路口和外部口,便于用户板卡快速集成。

6.本实用新型采用以下技术方案予以实现:

7.提出一种基于sip封装的数字信号处理器,包括单面布局于基板顶层上的四颗dsp裸芯片;其中;四颗dsp裸芯片的ebiu共享总线、中断信号、标识信号、复位倍频信号均单独引出;四颗dsp裸芯片之间通过链路口互联,并且每颗dsp裸芯片均引出一路链路口;四颗dsp裸芯片的jtag调试接口串接,测试数据经第一颗dsp裸芯片输入,经过第二、第三颗dsp裸芯片后从第四颗dsp裸芯片输出;其中,四颗dsp裸芯片的仿真信号并联到一根信号线引出一个引脚,tms、tck、trst也分别并联引出引脚;sip封装电源均布局于基板底层;裸芯片键合采用引线键合把金属引线连接到焊盘上,采用金丝热超声波法,将热、压力和超声波施加于毛细管劈刀进行连接;四颗dsp裸芯片的数据分配结构为:选用其中一颗dsp裸芯片作为主核,其他裸芯片作为子核,链路口配置为链式dma,主核设置一个带中断的外部端口dma,当主机处理器通过外部dma请求管脚来请求外部端口dma并在外部端口dma完成后,互联链路口发送dma的寄存器自动加载,将主核中的数据传送到子核;四颗dsp裸芯片的数据收拢结构为:四颗dsp裸芯片引出的链路口与主机处理器互联,把计算结果送到主机存储器。

8.进一步的,所述四颗dsp裸芯片包括dsp0、dsp1、dsp2和dsp3;每颗dsp裸芯片包括

四组双向链路口link0、link1、link2和link3,其中,link0均引出,link1、link2和link3均用于裸芯片间互联;四颗dsp裸芯片之间通过链路口互联,包括:dsp0的link1和dsp1的link2连接,link2和dsp3的link1连接,link3和dsp0的link3连接;dsp1的link1和dsp2的link2连接,link3和dsp3的link3连接;dsp2的link1和dsp3的link2连接。

9.进一步的,sip封装电源包括数字内核电压vdd、数字引脚电源vdd_io和模拟电源vdd_a,其中模拟电源包括时钟模拟电源avdd_pll和链路口模拟电源avdd_link;数字内核电压vdd对应dsp裸芯片位置布设,呈t状结构;数字引脚电源vdd_io对应dsp裸芯片除数字内核电压vdd以外的区域布设;模拟电源vdd_a布设于dsp裸芯片边缘区域。

10.进一步的,键合线采用wire bonding压焊工艺。

11.进一步的,所述基板采用8层叠层构成;其中,1层为大量信号走线及地平面,2层设为少量信号走线及地平面,3层为大量信号走线及地平面,4层为少量信号走线、电源以及地平面,5层为电源平面,6层为少量信号走线、电源及地平面,7层为电源平面,8层为电源以及地平面。

12.与现有技术相比,本实用新型的优点和积极效果是:本实用新型提出的基于sip封装的数字信号处理器,四颗dsp裸芯片单面布局于基板的顶层,电源单面布局于基板的底层;ebiu共享总线均单独引出,便于sip封装后的数字信号处理器之间级联,中断信号、标志信号、复位倍频信号也均单独引出,作为sip封装的数字信号处理器的中断、标识和复位控制引脚;四颗dsp裸芯片彼此之间通过链路口互联,且每颗dsp裸芯片均单独引出一路链路口作为sip封装的数字信号处理器之间互联的通路;四颗dsp裸芯片的jtag调试接口串接在一起,以四核形式来调试;芯片键合采用引线键合把金属引线连接到焊盘上,采用金丝热超声波法,将热、压力和超声波施加于毛细管劈刀,使其在最佳状态下连接;sip封装采用bga封装形式,数据分配和收拢结构设计为由主核从主机存储器接收数据并分配给子核,以及各子核通过引出的链路口把计算结果送到主机存储器;通过上述结构提出的数字信号处理器,结合了 sip封装内部走线短、走线密度高的优点,节省了空间并提高了系统整体带宽和计算能力,提高了数字信号处理器的稳定性,降低了系统成本与功耗;此外,保留了单dsp裸芯片的链路口,便于用户板卡快速集成。

13.结合附图阅读本实用新型实施方式的详细描述后,本实用新型的其他特点和优点将变得更加清楚。

附图说明

14.图1 为本实用新型提出的sip封装集成结构示意图;

15.图2为本实用新型提出的sip封装中各裸芯片ebiu共享总线结构示意图;

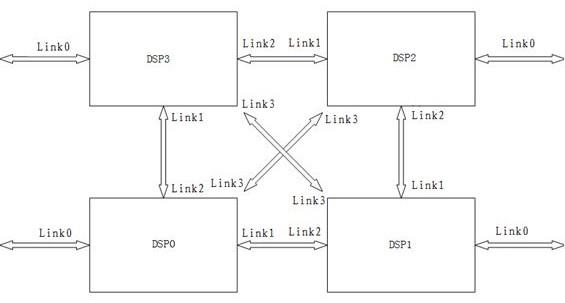

16.图3为本实用新型中各裸芯片链路口连接结构示意图;

17.图4为本实用新型中各裸芯片中断、标识、复位倍频信号引出结构示意图;

18.图5为本实用新型中sip封装电源分布结构示意图;

19.图6为本实用新型中基板结构示意图。

具体实施方式

20.下面结合附图对本实用新型的具体实施方式作进一步详细的说明。

21.本实用新型提出的基于sip封装的数字信号处理器,针对板载pcb走线缺点,将四颗dsp裸芯片组装在一起,以d20101为例,彼此间通过松耦合连接方式互联,即sip封装内部将四颗d20101链路口互联,封装内部走线更短,走线密度更高,稳定性根号,且保留单dsp裸芯片的链路口和外部口,便于用户板卡快速集成,使得该sip封装的数字信号处理器也适用于更多的dsp裸芯片集成。

22.具体的,如图1所示,四颗dsp裸芯片dsp0、dsp1、dsp2和dsp单面布局于基板顶层top,而sip封装电源布设于基板底层bottom。

23.整体的设计包括内部互联资源、电源、芯片键合方式、基板和封装形式。

24.内部互联资源包括ebiu共享总线、链路口交互通路、中断或标识信号以及调试接口。

25.其中,以d20101为例, ebiu共享总线包括32或64位数据总线、32位地址总线以及各种控制信号,可配置64、332总线宽度,可对存储器、多处理器或主机接口独立配置;并且支持eprom和flash接口协议;支持sdram接口协议;支持主机接口协议;支持慢速设备;支持多处理器分布式总线仲裁。针对四颗d20101 的ebiu共享总线,考虑到共享簇总线驱动能力、芯片启动方式、外部存储等使用特点,一共四套均单独引出,便于后期多个sip封装的数字信号处理器芯片之间级联,如图2所示,且可以并行访问sdram(同步动态随机存取内存)等外设。

26.每颗dsp裸芯片包括四组双向链路口link0、link1、link2和link3,每组包括4位独立输入和输出通道,并采用lvds技术。通信过程中,在链路口时钟上升沿和下降沿对数据进行锁存和驱动;每组链路口的吞吐率可达500mb/s,四组链路口同时工作是的数据吞吐率可达1gb/s。针对四颗d20101之间,通过链路口互联,并且每颗d20101均引出一组链路口,作为sip封装的数字信号处理器之间互联的通路。

27.在如图3所示的实施例中,link0均引出,link1、link2和link3均用于裸芯片间互联;四颗dsp裸芯片之间通过链路口互联,包括:dsp0的link1和dsp1的link2连接,link2和dsp3的link1连接,link3和dsp0的link3连接;dsp1的link1和dsp2的link2连接,link3和dsp3的link3连接;dsp2的link1和dsp3的link2连接。

28.四颗dsp裸芯片的irq中断信号、标志信号flag、复位倍频信号等均单独引出,作为sip封装的数字信号处理器的中断、标志、复位控制引脚,如图4所示。

29.dsp裸芯片支持 ieee 1149.1协议的jtag扫描链路,sip封装内部将四颗d20101调试接口串接在一起,以四核形式来调试;测试数据经第一颗dsp裸芯片输入,经过第二、第三颗dsp裸芯片后从第四颗dsp裸芯片输出;其中,四颗dsp裸芯片的仿真信号并联到一根信号线引出一个引脚,tms、tck、trst也分别并联引出引脚。

30.如图5所示,sip封装电源包括数字内核电压vdd、数字引脚电源vdd_io和模拟电源vdd_a,其中模拟电源包括时钟模拟电源avdd_pll和链路口模拟电源avdd_link;数字内核电压vdd对应dsp裸芯片位置布设,呈t状结构;数字引脚电源vdd_io对应dsp裸芯片除数字内核电压vdd以外的区域布设;模拟电源vdd_a布设于dsp裸芯片边缘区域。每种电源都有充足的空间分布;设计保证有足够的电源供应,避免由于电压供应不足而造成系统不稳定,以及电流密度过大造成局部温度过高而产生事故。

31.由于需要扇出的引脚数量较多,封装选择bga封装形式,根据工作环境气密性需求

分析采用塑料封装形式。

32.裸芯片键合,采用传统的引线键合把金属引线连接到焊盘上,采用强度更高的金丝热超声波法,将热、压力和超声波施加于毛细管劈刀,使其在最佳状态下进行连接。

33.具体的,键合线外层均匀排布,采用wire bonding压焊工艺,键合金属引线材质为金丝,该材质导电性好,且化学性很稳定,耐腐蚀性强;裸芯片键合由两次键合构成:

34.1、一次键合,金丝穿过毛细管劈刀正中央的小孔,提高金丝末端的温度,金丝融化后形成金丝球,打开夹持金属丝的夹钳(用于收放金属引线),施加热、压力和超声波振动,当毛细管劈刀接触焊盘时,形成的金丝球粘合到加热的焊盘上;

35.一次键合后,将毛细管劈刀提升到比预先测量的环路高度略高的位置,并移动到二次键合的焊盘上,形成一个引线环(loop)。

36.2、二次键合,向毛细管劈刀施加热、压力和超声波振动,并将第二次形成的金丝球碾压在pcb焊盘上,完成针脚式键合;针脚式键合后,当引线连续断裂时,进行拉尾线以形成一尾线,收紧毛细管劈刀的夹钳(即夹住引线)、断开金属引线,结束二次金丝球键合。

37.基板根据塑料封装形式,其材料选用有机基板,根据信号线密度和电源分布,采用8层基板。其中,1层为大量信号走线及地平面,2层设为少量信号走线及地平面,3层为大量信号走线及地平面,4层为少量信号走线、电源以及地平面,5层为电源平面,6层为少量信号走线、电源及地平面,7层为电源平面,8层为电源以及地平面;如图6所示,层叠结构中,根据板材和铜箔厚度,采用盲埋孔结构为1 1 4 1 1 。

38.该sip封装的数字信号处理器的数据分配和收拢,一般外部主机fpga或其他处理器,会将外部信号采集模块缓存的数据及时分配到主核,然后主核将数据分配到各个子核,最终计算结果汇总到主核上拢到主机。

39.具体的,四颗dsp裸芯片的数据分配结构为:选用其中一颗dsp裸芯片作为主核,其他裸芯片作为子核,链路口配置为链式dma,主核设置一个带中断的外部端口dma,当主机处理器通过外部dma请求管脚来请求外部端口dma并在外部端口dma完成后,互联链路口发送dma的txtcb寄存器自动加载,将主核ram 中的数据传送到子核;一次外部总线端口dma读到特定长度数据,同时dma中断服务程序isr,会将数据存放到主核内部ram连续地址上,紧接着配置链路口tcb寄存器使能链路口dma,链路口dma tcb寄存器加载后立即执行,把数据从主核传送到子核,这其中,子核链路口接收dma设置为链式dma,因为子核要连续地接收来自主核的数据。

40.四颗dsp裸芯片的数据收拢结构为:四颗dsp裸芯片引出的链路口与主机处理器互联,把计算结果送到主机存储器。

41.以d20101为例,其主频为600mhz,内部sram存储24mbit,峰值计算能力3.6gflops、4.8gmacs、14.4gops,io带宽5gb/s;通过上述sip封装后,性能上是d20101的四倍,即内部存储扩展为96mbit,峰值计算能力为14.4gfops、19.2gmacs、57.6gops,io带宽提高为8gb/s。

42.另外,通过sip封装解决了板载多颗d20101布局、布线的设计瓶颈,提高了板卡工作的稳定性。

43.应该指出的是,上述说明并非是对本实用新型的限制,本实用新型也并不仅限于上述举例,本技术领域的普通技术人员在本实用新型的实质范围内所做出的变化、改型、添加或替换,也应属于本实用新型的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1