一种错位封装结构的制作方法

1.本实用新型涉及电子技术领域,具体涉及一种错位封装结构。

背景技术:

2.电子产品自始至终都是朝着更小的尺寸、更轻的质量、更快的速度、更高的频率、更低的成本、更高的可靠性方向演进。

3.然后,当芯片的规格变小后,在封装过程中因为封装件的规格也相应变小,所以在焊接等步骤时非常容易导致s极与d极短路。

技术实现要素:

4.为了解决上述问题,本实用新型提供一种错位封装结构,适用于多种不同型号的芯片,可以减小出现短路的概率。

5.本实用新型所采用的技术方案是:

6.一种错位封装结构,包括半导体元件、第一压片、第二压片;

7.所述半导体元件包括第一表面以及第二表面,所述第一表面与第二表面相对设置;所述第一压片和所述第二压片四周上设置有多个连接筋,所述第一压片与所述第一表面连接,所述第二压片与所述第二表面连接,连接后所述第一压片上的任一连接筋都不在所述第二压片任一连接筋的正上方。

8.优选地,所述连接筋均匀设于所述第一压片和所述第二压片四周。

9.优选地,封装后的所述第一压片上的连接筋位于所述第二压片两个连接筋的正上方。

10.优选地,封装后的所述第一压片和所述第二压片之间的垂直距离小于0.15mm。

11.优选地,所述第一压片上的连接筋的厚度与所述第一压片的厚度相同。

12.优选地,所述第二压片上的连接筋的厚度与所述第二压片的厚度相同。

13.优选地,所述第一压片上的连接筋和所述第二压片上的连接筋大小一致。

14.优选地,所述第一压片上的连接筋和所述第二压片上的连接筋的宽度为0.2-0.4mm。

15.优选地,所述第一压片的面积大于所述第一表面的面积。

16.优选地,所述第二压片的面积大于所述第二表面的面积。

17.与现有技术相比,本实用新型的错位封装结构,通过调整用于封装元件的第一压片和第二压片上连接筋的位置,使封装后压片外露部分的连接位置错开,在各压片上连接筋数量不变的情况下,增大了第一压片和第二压片上连接筋之间的直线距离,降低了短路风险。

附图说明

18.为了更清楚地说明本技术实施方式中的技术方案,下面将对本技术实施方式中所

需要使用的附图进行说明。

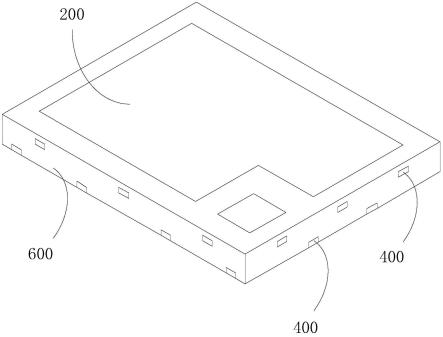

19.图1是本实用新型实施例提供的一种错位封装结构封装后的结构示意图;

20.图2是本实用新型实施例提供的一种错位封装结构的爆炸示意图;

21.图3是本实用新型实施例提供的一种错位封装结构封装后的前视图;

22.图4是本实用新型实施例提供的一种散热结构的俯视示意图;

23.图5是本实用新型实施例提供的一种散热结构的结构示意图;

24.图6是本实用新型实施例提供的一种散热结构的前视示意图。

具体实施方式

25.为了使本实用新型的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本实用新型进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本实用新型,并不用于限定本实用新型。

26.本实用新型实施例中的“第一”、“第二”等术语,仅为区别相关技术特征,不表示先后顺序。应该理解这样使用的数据在适当情况下可以互换,以便这里描述的本技术的实施例。此外,术语“包括”和“具有”以及他们的任何变形,意图在于覆盖不排他的包含,例如,包含了一系列步骤或单元的过程、方法、系统、产品或设备不必限于清楚地列出的那些步骤或单元,而是可包括没有清楚地列出的或对于这些过程、方法、产品或设备固有的其它步骤或单元。

27.在本技术中,术语“上”、“下”、“内”、“中”、“外”、“前”、“后”等指示的方位或位置关系为基于附图所示的方位或位置关系。这些术语主要是为了更好地描述本技术及其实施例,并非用于限定所指示的装置、元件或组成部分必须具有特定方位,或以特定方位进行构造和操作。

28.并且,上述部分术语除了可以用于表示方位或位置关系以外,还可能用于表示其他含义,例如术语“上”在某些情况下也可能用于表示某种依附关系或连接关系。对于本领域普通技术人员而言,可以根据具体情况理解这些术语在本技术中的具体含义。

29.此外,术语“设置”、“连接”、“固定”应做广义理解。例如,“连接”可以是固定连接,可拆卸连接,或整体式构造;可以是机械连接,或电连接;可以是直接相连,或者是通过中间媒介间接相连,又或者是两个装置、元件或组成部分之间内部的连通。

30.实施例1

31.本实用新型实施例提供一种错位封装结构,主要是应用在功率器件封装元件中的芯片,例如应用在大功率晶体管,晶闸管,双向晶闸管gto(gate-turn-off thyristor,可关断晶闸管),mosfet(metal oxide semiconductor field effect transistor),igbt(insulated gatebipolar transistor)等中电子元件中的防水封装结构,当然只要是符合可应用本技术的元器件,都可以适用本实施例的错位封装结构。

32.如图1-3所示,包括半导体元件110、第一压片200、第二压片300;半导体元件110包括第一表面以及第二表面,第一表面与第二表面相对设置;第一压片200和第二压片300四周上设置有多个连接筋400,第一压片200与第一表面连接,第二压片300与第二表面连接,连接后第一压片200上的任一连接筋400都不在第二压片300任一连接筋400的正上方。

33.现有用于封装的上下压片多是采用同样的压片,这样封装后上压片的连接筋400

位于下压片的连接筋400的正上方,当半导体元件110的规格变小时,上下压片上的连接筋400之间的直线距离也会变小,例如,当小于0.15mm时,在后续应用(如pcb焊接)过程中,非常容易导致两个压片直接短路,影响半导体元件110的正常使用,甚至损毁。本技术的第一压片200上的任一连接筋400都不在第二压片300任一连接筋400的正上方,这样增大了上下压片上的连接筋400之间的直线距离。

34.连接筋400均匀设于第一压片200和第二压片300四周,均匀设置连接筋400使得每个连接筋400受力均匀,这样避免出现单一连接筋400受力过大出现损毁的情况。

35.封装后的第一压片200上的连接筋400位于第二压片300两个连接筋400的正上方。这样,在连接筋400的大小和数量不变的情况下,尽可能的增大了连接筋400之间的直线距离。

36.封装后的第一压片200和第二压片300之间的垂直距离小于0.15mm,这样如果上下压片采用同样的压片,这样封装后上压片的连接筋400位于下压片的连接筋400的正上方,上下压片上的连接筋400之间的直线距离也会小于0.15mm,所以在后续应用(如pcb焊接)过程中,非常容易导致两个压片直接短路,影响半导体元件110的正常使用。

37.第一压片200上的连接筋400的厚度与第一压片200的厚度相同,第二压片300上的连接筋400的厚度与第二压片300的厚度相同。在实际的生产活动中,考虑到生产压片的难易度,以及连接筋400的强度问题,连接筋400的厚度一般都是与压片的厚度相同。

38.第一压片200上的连接筋400和第二压片300上的连接筋400大小一致。

39.第一压片200上的连接筋400和第二压片300上的连接筋400的宽度为0.2-0.4mm。

40.第一压片200的面积大于第一表面的面积,第二压片300的面积大于第二表面的面积。

41.与现有技术相比,本实用新型的错位封装结构,通过调整用于封装元件的第一压片和第二压片上连接筋的位置,使封装后压片外露部分的连接位置错开,在各压片上连接筋数量不变的情况下,增大了第一压片和第二压片上连接筋之间的直线距离,降低了短路风险。

42.实施例2

43.本实施例提供一种散热结构,主要是应用在功率器件封装元件中的半导体元件,例如应用在大功率晶体管,晶闸管,双向晶闸管gto(gate-turn-off thyristor,可关断晶闸管),mosfet(metal oxide semiconductor field effect transistor),igbt(insulated gatebipolar transistor)等中电子元件中的散热结构。

44.如图4-6所示本实施例的散热结构100,包括半导体元件110、第一导电片140、第二导电片150、第三导电片160;半导体元件110包括第一表面以及第二表面,第一表面上设有s级120和g级130,第一导电片140设于s级120上,第二导电片150设于g级130上,第三导电片160设于第二表面上;s级120与g级130之间不相连且具有间隙。半导体元件110可以简单的理解为“芯片”或者是晶体硅层,还可以是其他可以实现以上两者功能的其他元件,一般是如图2所示的扁平矩形结构,还可以是扁平圆形等结构,具体的形状和构造是可以根据实际的需要和生产变化决定的。第一表面与第二表面一般是如图所示的相对设置的,但是不一定都是相对设置的,在不影响功能的前提下,还可以是相邻设置的。

45.第一导电片140、第二导电片150、第三导电片160材质为金属银,银的散热性能是

目前可以应用于芯片制造中较佳的,选择金属银作为导电片的材料,在提升了芯片的散热能力的同时,还可以用于电路导通。

46.第一、第二、第三导电片160可以是通过电镀形成的,还可以是压合等方法固定到半导体元件110上。通过这种双面设置,能够增大散热面积,提高芯片运行的性能。

47.第一导电片140的形状与s级120相同,面积小于s级120,第一导电片140居中设于s级120上。

48.第二导电片150的形状与g级130相同,面积小于g级130,第二导电片150居中设于g级130上。

49.第三导电片160的面积与第二表面的面积相同。

50.s级120的边缘距离第一表面的边缘大于等于0.3mm,当距离第一表面边缘的距离大于或者等于0.6mm时,可以适应高压的需求。

51.g级130的边缘距离第一表面的边缘大于等于0.3mm,当距离第一表面边缘的距离大于或者等于0.6mm时,可以适应高压的需求。

52.s极120加上g极130的面积不小于第一表面的80%,具体涂银浆区域、和范围根据实际生产中芯片的规格大小以及芯片焊盘区决定。

53.尽可能的增大银的覆盖面积,可以增强后续芯片的散热能力以及减少电子传输的距离。

54.s极120与g级130的间距大于等于0.2mm,并且可以在s极120与g级130包含有绝缘填充物。通过绝缘填充物来保证s极120与g级130之间没有短路。

55.本实用新型的散热结构,通过在设置s极120和g极130的第一表面上设置面积尽可能大的第一、第二导电片,并将第三导电片全覆盖第二表面,进而增大了散热面积,提升了散热能力,进而提高芯片运行的性能;s极与g极之间设置合理的间隔距离可以减少出现短路的可能性。

56.通过实施例2可以更好的理解实施例1。

57.以上所述,仅为本实用新型较佳的具体实施方式,但本实用新型的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本实用新型揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本实用新型的保护范围之内。因此,本实用新型的保护范围应该以权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1