制造具有改进的切割特性的半导体结构的方法与流程

1.本发明涉及集成领域,并且更具体地,涉及电子产品、相关的半导体产品以及它们的制造方法。

背景技术:

2.目前,硅无源集成技术可以用于工业设计。例如,由murata integrated passive solutions开发的pics技术允许将高密度电容部件集成到硅基板中。根据该技术,可以将数十个甚至数百个无源部件有效地集成到硅芯片中。

3.在p.banerjee等人的他们题为“nanotubular metal-insulator-metal capacitor arrays for energy storage(用于能量存储的纳米管金属-绝缘体-金属电容器阵列)”(在2009年5月的natural technology(自然技术)中发表)的工作中,描述了在多孔区域比如阳极氧化铝(aao)中形成的金属-绝缘体-金属(mim)结构。通常,多孔区域通过对金属层、比如铝层进行阳极氧化产生。阳极氧化将铝层转化成aao。连续的金属、绝缘体并且然后金属的层遵循多孔区域的轮廓,使得mim结构嵌入在多孔区域的孔的内部。

4.通常,如上所述的aao嵌入式结构形成在基板、比如硅晶片的顶部上。在实践中,如图1中所示,aao嵌入式结构形成在晶片的指定电路区域中。晶片然后沿着指定的切割路线被切割,以获得其上具有aao嵌入式结构的芯片。

5.已经表明的是,在芯片的边缘处存在aao区域保护了电路区域免受湿气流入,并且降低了顶部电极与(由铝层提供的)底部电极之间的泄漏的风险,上述现象经常在后续工艺步骤比如晶片凸块中观察到。因此,在实践中,如图1中所示,沿着晶片的指定切割区域形成留空(即,其中没有嵌入的电路)的aao区域。晶片沿着穿过切割区域的切割路线被切割。

6.可以用于切割图1中所示的晶片的常用技术被称为“研磨前切割”(dbg)。根据dbg,晶片最初在芯片的最终目标厚度(即,晶片没有被完全切割)之前(沿着切割路线)被开槽至一定深度水平。然后,晶片从底部减薄至最终目标厚度,这导致芯片分离。

7.因为芯片分离发生在研磨工艺期间,所以由dbg产生的芯片具有良好的机械应力,并且还表现出减少背面碎裂(碎裂是芯片的部件从芯片脱离的现象)。然而,顶面碎裂较难消除。例如,图2示出了在利用dbg切割之后的晶片、比如图1中所示的晶片的俯视图。如所示出的,所得到的芯片在边缘处遭受清晰可见的碎裂。此外,这种顶面碎裂似乎不受所使用的切割刀片的影响。

8.另一种可以使用的切割技术是利用激光开槽(lg),然后像在dbg中一样进行研磨。根据该混合技术,可以显著减少或消除背面和顶面碎裂。然而,激光开槽的应用削弱了所得到的芯片的机械强度。例如,图3示出了通过使用混合lg-dbg工艺切割晶片结构得到的芯片的扫描电子显微镜(sem)图像。如所示出的,激光开槽导致边缘aao区域的一些熔化,并且支承基板也可能出现破裂和损坏。

技术实现要素:

9.本发明提出了一种制造半导体结构的方法,包括:

10.在硅晶片上限定电路区域和切割区域;

11.在硅晶片上形成第一金属层;

12.在第一金属层上形成第二金属层;

13.在第一金属层的顶表面的位于硅晶片的电路区域上方的区域上形成阻挡层;

14.在第二金属层的位于电路区域上方的第一区域中形成第一多孔结构,并且在第二金属层的位于切割区域上方的第二区域中形成第二多孔结构,其中,第一多孔结构包括第一组孔,所述第一组孔从第一多孔结构的顶表面延伸至阻挡层,并且其中,第二多孔结构包括第二组孔,所述第二组孔从第二多孔结构的顶表面延伸至硅晶片;

15.在第一多孔结构的第一组孔中形成金属-绝缘体-金属(mim)叠层;以及

16.蚀刻第二多孔结构的第二组孔蚀刻以暴露硅晶片的切割区域。

17.在第二组孔被蚀刻以暴露切割区域的情况下,硅晶片可以沿着穿过切割区域的切割路线更容易地被切割。具体地,可以在减少的分层、碎裂和支承基板中的破裂的情况下执行硅晶片的切割。

18.在实施方式中,该方法还包括沿着穿过切割区域的切割路线切割硅晶片。该切割可以作为dbg或混合lg-dbg工艺的一部分来执行。所得到的结构是具有aao嵌入式电路的半导体结构,该半导体结构具有改进的机械轮廓,包括减少的分层、碎裂和支承基板中的破裂。

19.此外,由于上面的制造方法,所得到的结构受益于第二多孔结构的一部分在该第二多孔结构的边缘处的持续存在,这保护了电路区域免受湿气流入的影响,并且降低了后续工艺步骤、特别是晶片凸块中泄漏的风险。

20.在一个实施方式中,该方法包括:

21.在第二金属层上形成第一掩模层,该第一掩模层具有在第二金属层的第一区域上方的第一开口和在第二金属层的第二区域上方的第二开口;以及

22.对第二金属层的第一区域和第二区域进行阳极氧化,以形成第一多孔结构和第二多孔结构。

23.阻挡层保护位于硅晶片的电路区域上方的区域中的第一金属层。具体地,阻挡层可以用于阻止阳极氧化的进程到达电路区域上的第一金属层。相反,在第一金属层的位于硅晶片的切割区域上方的等效表面上没有形成等效的阻挡层。因此,在实施方式中,第二多孔结构延伸到第一金属层的位于第二金属层的第二区域下面的区域中。

24.在形成阻挡层的情况下,该方法包括在第一金属层和阻挡层上形成第二金属层。

25.在另一实施方式中,该方法可以包括将第一金属层图案化成在第一金属层中、在硅晶片的切割区域上形成开口。该方法然后还可以包括在第一金属层、阻挡层和硅晶片的切割区域上形成第二金属层。在第一金属层被如此图案化的情况下,在形成第二金属层之前,可以以更少的步骤执行阳极氧化过程,因为在这种情况下,第一多孔结构和第二多孔结构的形成将需要大致相等深度的层的阳极氧化。

26.在一个实施方式中,该方法包括:

27.在第一掩模层、第一多孔结构和第二多孔结构上沉积第二掩模层;

28.将第二掩模层图案化成在第二掩模层中、在第一多孔结构的第一组孔上形成开口;以及

29.在第二掩模层上沉积mim叠层。

30.第二掩模层确定了第一多孔结构和第二多孔结构中的哪些孔填充有mim叠层。

31.在一个实施方式中,第二掩模层确保mim叠层仅形成在第一多孔结构的第一组孔、即落入电路区域中的孔的内部,并且所述孔基本上具有期望的方向性并形成为能够可靠地嵌入mim电路。

32.第二多孔结构可以包括位于第二多孔结构的第二组孔的两侧的侧向孔。

33.在一个实施方式中,第二掩模层覆盖第二多孔结构的第二组孔。在另一实施方式中,第二掩模层完全覆盖第二多孔结构的第二组孔和侧向孔。

34.在另一实施方式中,第二掩模层包括位于第二多孔结构的侧向孔中的至少一些侧向孔上的开口。替代性地或另外地,开口可以形成在第二多孔结构的第二组孔中的与侧向孔相邻的一些孔上。

35.同样地,该方法还可以包括将mim叠层形成在第一多孔结构的第一组孔中以及第二多孔结构的侧向孔中的至少一些侧向孔和/或第二多孔结构的第二组孔中的与侧向孔相邻的至少一些孔中。mim叠层形成在第二多孔结构的侧向孔中的一些孔和/或第二多孔结构的第二组孔的与侧向孔相邻的一些孔中使得半导体结构具有改进的机械强度,特别是在边缘处具有改进的机械强度。

36.在实施方式中,该方法包括移除第二多孔结构的全部第二组孔上的mim叠层和第二掩模层。

37.在另一实施方式中,该方法包括移除第二多孔结构的第二组孔的中央子组上的mim叠层和第二掩模层。

附图说明

38.根据参照附图仅通过说明而非限制的方式给出的本发明的某些实施方式的以下描述,本发明的其他特征和优点将而变得明显,在附图中:

39.图1图示了包括阳极氧化铝(aao)嵌入式结构的示例晶片结构的横截面图。

40.图2示出了使用“研磨前切割”(dbg)工艺切割的晶片结构。

41.图3示出了通过使用混合式激光开槽(lg)和dbg工艺对晶片结构进行切割得到的芯片的扫描电子显微镜(sem)图像。

42.图4a至图4p图示了根据实施方式的制造半导体结构的示例工艺的步骤。

43.图5a至图5d图示了根据实施方式的制造半导体结构的另一示例工艺的步骤。

44.图6a至图6d图示了根据实施方式的制造半导体结构的另一示例工艺的步骤。

具体实施方式

45.本发明的实施方式通过提出制造具有aao嵌入式电路的半导体结构的方法来解决现有技术的现有缺陷,该aao嵌入式电路具有改进的机械轮廓,包括减少的分层、碎裂和支承基板中的破裂。

46.图4a至图4p图示了根据实施方式的制造具有改进的机械轮廓的半导体结构的示

例工艺的步骤。具体地,图4a至图4p示出了与所图示的步骤相对应的半导体结构的竖向横截面图。

47.如图4中所示,该工艺开始于在硅晶片102上限定电路区域134和切割区域136。切割区域136与电路区域134邻近并且间隔开。

48.电路区域134与硅晶片102的意在构建功能电路的部段相对应。切割区域136与晶片102的不构建功能电路的部段相对应,并且一个或更多个切割路线被设计为穿过该部段。如上所述,切割路线是在晶片102已经被处理之后,晶片102沿着其被切割/切削以获得多个芯片或块的路线,其中,每个芯片或块包括给定的功能集成电路。

49.在图4a中,示出了电路区域134和切割区域136的横截面图。如本领域技术人员将理解的,电路区域134和切割区域136沿着垂直于图平面(进入和/或离开图平面)的平面延伸。

50.如本领域技术人员将理解的,在实施方式中,可以在晶片102上限定一个或更多个电路区域134以及一个或更多个切割区域136。

51.接下来,如图4b中所示,该工艺包括在硅晶片102上形成第一金属层104。第一金属层104可以由与诸如钛、氮化钛、钽、氮化钽之类的阻挡金属组合或不组合的铝、铜(cu)、银(ag)或铝铜(alcu)制成。在实施方式中,如图4b中所示,第一金属层104包括钛氮化钛(titin)层、alcu层和titin层的叠层。

52.接下来,如图4c中所示,该工艺包括在第一金属层104的顶表面的区域110上形成阻挡层108。如图4c中所示,区域110位于硅晶片102的电路区域134上方。

53.在实施方式中,区域110与电路区域134在第一金属层104的顶表面上的投影对应。因此,区域110和电路区域134具有相同的几何形状。在另一实施方式中,区域110可以延伸超出与电路区域134在第一金属层104的顶表面上的投影对应的区域。然而,区域110不包括第一金属层104的顶表面的位于硅晶片102的切割区域136上方的区域、即与切割区域136在第一金属层104的顶表面上的投影对应的区域。

54.在实施方式中,通过下述方式形成阻挡层108:在第一金属层104的整个顶表面上沉积阻挡层108的材料,并且然后将沉积的材料图案化成使得只有第一金属层104的区域110被沉积的材料覆盖。下面参照图4f进一步描述阻挡层108的作用。

55.接下来,如图4d中所示,该工艺包括在第一金属层104上形成第二金属层112。如所示出的,第一金属层104也位于阻挡层108的顶部上。

56.接下来,如图4e中所示,在第二金属层112上形成有第一掩模层114,然后该第一掩模层114图案化成具有在第二金属层112的第一区域118上方的第一开口116以及在第二金属层112的第二区域122上方的第二开口120。如所示出的,第二金属层112的第一区域118位于硅晶片102的电路区域134以及阻挡层108的上方。第二区域122位于硅晶片102的切割区域136的上方。

57.第一掩模层114可以由二氧化硅制成。替代性地,金属可以用于第一掩模层114,例如,优选地是(在室温下)有延展性的金属,比如钛、钽或等效性质的金属。

58.接下来,如图4f中所示,该工艺包括在第二金属层112的第一区域118中形成第一多孔结构124以及在第二金属层112的第二区域122中形成第二多孔结构126。在实施方式中,第二多孔结构126延伸到第一金属层104在第二区域122下面的区域中。

59.在实施方式中,第一多孔结构124和第二多孔结构126是通过在电解液中阳极氧化第二金属层112形成的。第一掩模层114的存在确保了多孔结构基本上仅形成在第二金属层112的在第一掩模层114的开口116和120下面的区域(开口区域)中。

60.在阳极氧化过程期间,第二金属层112的在开口区域中的表面上形成氧化物层或氢氧化物层,所述氧化物层或氢氧化物层沿着由施加的电场确定的优选的方向被电解液溶解。随着电解液溶解氧化物/氢氧化物层,在第二金属层的暴露的表面上形成新的氧化物/氢氧化物。因此,第二金属层112在开口区域中逐渐转变成阳极氧化物或氢氧化物的多孔结构124和126,所述多孔结构124和126具有从顶表面基本上垂直地延伸的孔,每个孔通过氧化物或氢氧化物的壁与相邻的孔隔开。

61.在实施方式中,第二金属层112由铝制成。因此,第一多孔结构124和第二多孔结构126由阳极氧化铝(aao)制成。

62.在实施方式中,如图4f中所示,第一多孔结构124包括第一组孔138,所述第一组孔138从第一多孔结构124的顶表面延伸至阻挡层108。第一组孔138基本上垂直于阻挡层108。在实践中,第一组孔138的底部可以不完全开口到阻挡层108。同样地,在实施方式中,第一组孔138的底部处的任何残留材料可以被蚀刻,以使第一组孔138完全开口到阻挡层108上,即,以暴露孔138的底部处的阻挡层108。

63.阻挡层108用于通过阻止阳极氧化的进程到达第一金属层104而在阳极氧化过程期间保护第一金属层104。此外,阻挡层108可以在第一组孔138的底部处的任何残留材料被蚀刻掉时保护第一金属层104。在实施方式中,阻挡层108可以由钨或在使用的电解液中抗阳极氧化的等效材料制成。

64.根据阳极氧化过程的条件,第一多孔结构124还可以包括位于第一掩模层114的边缘附近(第一组孔138的两侧处)的侧向孔146,所述侧向孔146不朝向第一金属层104大致垂直地延伸,而是朝向第二金属层112对角地/侧向延伸,如图4f中所示。侧向孔146通常是由于下述事实而形成的:所施加的电场在第一掩模层114的边缘附近可能不均匀和/或较弱,这导致侧向孔146不具有期望的方向性。

65.第二多孔结构126包括从第二多孔结构126的顶表面延伸至硅晶片102的第二组孔140。第二组孔140大致垂直于硅晶片102。在实践中,第二组孔140的底部可以或可以不完全开口到硅晶片102上。此外,与第一多孔结构124一样,第二多孔结构126也可以包括位于第一掩模层114的边缘附近(第二组孔140的两侧处)的侧向孔144,所述侧向孔144不朝向硅晶片102大致垂直地延伸,而是朝向第二金属层112对角地/侧向延伸,如图4f中所示。

66.在本文中应当注意的是,第二金属层112的第二区域122下面不存在阻挡层108允许了阳极氧化过程进行到第一金属层104中并且到达硅晶片102。

67.在各实施方式中,第一多孔结构124和第二多孔结构126可以利用相同的阳极化步骤或者利用不同的阳极化步骤形成。阳极氧化过程和影响阳极氧化过程的条件在本领域中是公知的,本领域技术人员将充分理解可以形成第一多孔结构124和第二多孔结构126的不同方式。例如,本领域技术人员将理解形成第一多孔结构124和第二多孔结构126所必需的阳极氧化控制参数,包括在第一组孔138已经到达第一金属层104并且第二组孔140已经到达硅晶片102时允许阳极氧化过程停止的参数。

68.根据另一实施方式,在图4c和图4d中所示的步骤之间引入了图5a中所示的附加工

艺步骤。也就是说,在第一金属层104的顶表面的区域110上形成阻挡层108之后,第一金属层104图案化成在该第一金属层104中、在硅晶片102的切割区域136上形成开口142。开口142暴露了硅晶片102的切割区域136。

69.根据该实施方式的工艺的后续步骤与上面参照图4d至图4f描述的以及下面参照图4g至4p进一步描述的工艺步骤相同。为了说明,图5b、图5c和图5d示出了根据该实施方式的工艺步骤,所述工艺步骤与上面参照图4d至图4f描述的工艺步骤——即,第二金属层112的形成、具有开口116和120的第一掩模层114的形成、以及在第二金属层112的第一区域118中的第一多孔结构124的形成和在第二金属层112的第二区域122中的第二多孔结构126的形成——相对应。应当注意的是,根据该实施方式,第二金属层112可以形成在第一金属层104、阻挡层108和硅晶片102的切割区域136上。该实施方式的优点在于,在第一金属层104如所描述地图案化的情况下,在形成第二金属层112之前,可以以更少的步骤执行阳极氧化过程,因为在这种情况下,第一多孔结构124和第二多孔结构126的形成将需要大致相等深度(即,层112的深度)的层的阳极氧化。

70.回到图4a至图4p的示例工艺,然后,该工艺继续图4g中所示的步骤,该步骤包括:在第一掩模层114、第一多孔结构124和第二多孔结构126上沉积第二掩模层128;以及将第二掩模层128图案化成在第二掩模层128中、在第一多孔结构124的第一组孔138上形成开口130。因此,第二硬掩模层128覆盖了第一多孔结构124的侧向孔146。这确保了孔146不被用于构建在其中的电路。这是有利的,因为这些孔在电学贡献(例如,电容、电阻等)方面通常难以量化,并且这些孔在后续工艺步骤(例如,下面进一步描述的mim叠层原子层沉积(ald)步骤)使用基于卤素的前体时可能倾向于将卤素腐蚀引入到所得到的产品中。

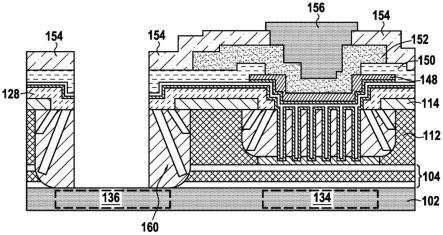

71.如图4g中所示,根据该实施方式,第二掩模层128也覆盖第二多孔结构126的第二组孔140。此外,根据该实施方式,第二硬掩模层128也覆盖第二多孔结构126的侧向孔144。

72.接下来,如图4h中所示,在第二掩模层128上沉积有金属-绝缘体-金属(mim)叠层132。在实施方式中,利用ald沉积mim叠层132。由于开口130,mim叠层132形成在第一多孔结构124的第一组孔138中。也就是说,连续的金属、绝缘体并且然后金属的层遵循第一多孔结构124的轮廓,使得mim叠层132嵌入在第一多孔结构124的第一组孔138的内部。

73.随后,如图4i中所示,导电材料(例如,铝)可以可选地被沉积和图案化,以形成与mim叠层132的顶部金属层接触的顶部电极148。在实施方式中,如图4i中所示,在形成顶部电极148时,在顶部电极148不延伸的区域中,mim叠层132的顶部金属层被移除。换句话说,mim叠层132的顶部金属层仅保留在顶部电极148的下面。这降低了在顶部电极148与底部电极之间发生短路泄漏的可能性(在下面进一步描述)。

74.接下来,如图4j中所示,该工艺包括移除第二多孔结构126的第二组孔140上的mim叠层132和第二掩模层128,以暴露第二组孔104。mim叠层可以通过干法蚀刻来移除。

75.随后,如图4k中所示,绝缘材料可以可选地被沉积和图案化,以形成绝缘层150。

76.然后,如图4l中所示,导电材料(例如,铝)可以可选地被沉积和图案化,以形成接触顶部电极148的接触层152。

77.然后,如图4m中所示,钝化层154可以可选地被沉积和图案化。钝化层154可以利用等离子体增强化学气相沉积(pecvd)来形成,该等离子体增强化学气相沉积使用干法蚀刻工艺来处理和图案化。

78.然后,如图4n中所示,导电材料(例如,氮化金)可以可选地被沉积和图案化,以形成顶部电极接触156。

79.接下来,如图4o中所示,该工艺可以包括移除第二多孔结构126的第二组孔140上的任何形成的层,以暴露第二组孔140。例如,在实施方式中,第二组孔140被钝化层154直接覆盖,第二组孔140上的钝化层154被移除以暴露所述第二组孔140。钝化层154可以通过干法蚀刻工艺移除。

80.随后,如图4p中所示,第二组孔140可以被蚀刻,以暴露硅晶片102的切割区域136。在实施方式中,使用各向同性湿法蚀刻步骤来移除第二组孔140。

81.在切割区域136被暴露的情况下,硅晶片102然后可以沿着穿过切割区域136的切割路线被切割。所得到的结构(即,图4p中切割区域136的右侧的结构)是具有aao嵌入式电路的半导体结构(在这种情况下是电容器),该半导体结构具有改进的机械轮廓,包括减少的分层、碎裂和支承基板中的破裂。此外,所得到的结构受益于第二多孔结构126的一部分160在所述第二多孔结构126的边缘处的持续存在,这减少了湿气的影响和特别是由于晶片土块工艺而泄漏的风险。

82.根据另一实施方式,可以在参照图4g在上面描述的步骤处修改该工艺。也就是说,如图6a中所示,第二掩模层128可以图案化成在第二多孔结构126的侧向孔144中的至少一些侧向孔和/或第二多孔结构126的第二组孔140中的与侧向孔144相邻的一些孔上具有开口158。第一多孔结构124的第一组孔138上的开口130也如图4g中所示地形成。

83.随后,如图6b中所示,可以形成mim叠层132。由于存在开口158,mim叠层132形成在第二多孔结构126的暴露的孔的内部。在图6b中,这包括侧向孔144中的一些侧向孔和第二组孔140中的紧邻暴露的侧向孔的一些孔。相反,第二组孔140的中央子组140a受到第二硬掩模层128的保护并且未被填充。

84.该工艺然后可以继续到图4i中所示的步骤。

85.随后,在与图4j中所示的步骤相对应的步骤中,该工艺可以包括移除第二多孔结构126的第二组孔140的中央子组140a上的mim叠层132和第二掩模层128。

86.该工艺然后可以根据图4k、图4l、图4m和图4n中所示的步骤继续。

87.然后,如图6c中所示,该工艺可以包括移除第二多孔结构126的第二组孔140的中央子组104a上的任何形成的层。例如,可以移除第二组孔140的中央子组140a上的钝化层154以暴露中央子组140a。

88.随后,如图6d中所示,第二组孔140的中央子组140a可以被蚀刻以暴露硅晶片102的切割区域136。在切割区域136被暴露的情况下,硅晶片102然后可以沿着穿过切割区域136的切割路线被切割。所得到的结构具有与先前描述的实施方式所得到的结构类似的优点。此外,用mim填充第二多孔结构126的孔中的一些孔提高了所得到的结构的机械强度,特别是边缘处的机械强度。

89.另外的变型

90.虽然上面已经参照某些特定实施方式描述了本发明,但是应当理解的是,本发明不受特定实施方式的特性的限制。可以在所附权利要求的范围内在上述实施方式中做出许多变型、改型和改进。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1