显示器件及相关联的方法与流程

显示器件及相关联的方法

1.相关申请的交叉引用

2.本技术受益于2020年2月10日提交的美国临时专利申请序列号62/972,206并要求其优先权,该申请的全部公开内容通过引用并入本文。

背景技术:

3.本公开的各方面总体上涉及可以与各种类型的显示器结合使用的发光器件,更具体地,涉及单片多色发光二极管(led)。

4.随着显示器中使用的发光元件(例如像素)的数量不断增加以提供更好的用户体验并使得能实现新的应用,从设计和制作的角度来看,添加越来越多的发光元件成为一个挑战。实现更小的发光元件以增加数目和密度使得小led的潜在用途更具吸引力;然而,用于制作大量、高密度并能够产生彩色显示器所需的不同颜色(例如,红色、绿色、蓝色)的小led的有效和高效技术并不是广泛可用的,并且那些确实存在的技术往往繁琐、耗时且成本高昂。此外,在诸如光场显示器和微型显示器的在性能和尺寸两者方面具有更严格要求的更复杂的显示架构中使用这些小led变得相当难以完成。

5.因此,需要使得能实现有效和高效设计和制作大量多色led的技术和器件。

技术实现要素:

6.下面给出一个或多个方面的简化摘要,以便提供对这些方面的基本理解。该摘要不是对所有预期方面的广泛概述,并且既不旨在识别所有方面的关键或要素,也不旨在描绘任何或所有方面的范围。其目的是以简化的形式呈现一个或多个方面的一些概念,作为稍后呈现的更详细描述的序言。

7.在第一方面,一种显示器件包括衬底,所述衬底在其上包括第一发射体和第二发射体。第一发射体包括第一下部有源量子阱(qw)区,所述下部有源量子阱(qw)区具有跨越第一光谱范围的第一发射光谱。第二发射体包括(i)上部有源qw区,所述上部有源qw区具有跨越与第一光谱范围不同的第二光谱范围的第二发射光谱,(ii)第二下部有源qw区,所述第二下部有源qw区具有第一发射光谱并且位于上部有源qw区和衬底之间,以及(iii)在第二下部有源qw区和上部有源qw区之间的势垒层,用于抑制第二下部有源qw区的发射。

8.在第二方面,一种用于形成多个光发射体的方法包括以下列举的步骤(i)-(vii)。步骤(i)包括在衬底上形成第一凹槽,第一凹槽具有第一宽度和第一深度。步骤(ii)包括在衬底上形成第二凹槽,第二凹槽具有第二宽度和第二深度,第二宽度和第二深度中的至少一个分别大于第一宽度和第一深度。步骤(iii)包括在衬底上沉积第一n型势垒材料。步骤(iv)包括在第一n型势垒材料上制作第一有源量子阱(qw)结构。步骤(v)包括在第一有源qw结构上沉积第二n型势垒材料;步骤(vi)包括在第二n型势垒材料上制作第二有源qw结构。步骤(vii)包括在第二有源qw结构上沉积第三n型势垒材料。第一凹槽的第一宽度和第一深度被配置为防止在第一凹槽内形成第二有源qw结构,使得第一n型势垒材料、第一有源qw结构和第二n型势垒层形成第一光发射体。第二凹槽的第二宽度和第二深度被配置为将第一n

型势垒材料、第一有源qw结构、第二n型势垒材料、第二有源qw结构和第三n型势垒材料支撑在第二凹槽内并至少部分包含在第二凹槽内以形成第二光发射体。

附图说明

9.附图仅说明了一些实施方式,因此不应被认为是对范围的限制。

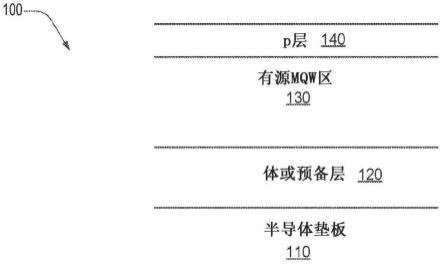

10.图1图示了通常实现的微型led结构。

11.图2图示了根据本公开的方面的作为用于显示器的阵列的一部分的多个微型led结构的俯视图。

12.图3图示了根据本公开的方面的包括有源多量子阱(mqw)区的微型led结构的示例。

13.图4图示了根据本公开的方面的通过选择性区域生长(sag)开口宽度的led颜色选择的示例。

14.图5图示了根据本公开的方面的通过sag开口宽度和深度的led颜色选择的示例。

15.图6图示了根据本公开的方面的通过sag开口深度的led颜色选择的示例。

16.图7图示了根据本公开的方面的通过基座宽度的led颜色选择的示例。

17.图5、图6和图7示出了根据本公开的方面的具有蚀刻隔离的单个连续sag的示例。

18.图8-图10为显示器件的相应剖面示意图,其中每一个都是图4的显示器件的一个示例。

19.图11和图12示出了根据本公开的方面的具有均匀高度的单个sag的示例。

20.图13是示出了根据本公开的方面的用于形成多个光发射体的方法的流程图。

具体实施方式

21.下面结合附图阐述的详细描述旨在作为对各种配置的描述,而不是旨在表示可以实践本文描述的概念的唯一配置。详细描述包括特定细节,目的是提供对各种概念的透彻理解。然而,对于本领域的技术人员来说显而易见的是,可以在没有这些具体细节的情况下实践这些概念。在某些情况下,众所周知的组件以框图形式显示,以避免混淆这些概念。

22.鉴于上述问题,非常需要使用单外延(例如,单外延生长通道)多色led阵列,因为包括但不限于显示器的许多应用需要多个颜色的发射体。不同颜色的多个阵列的混合组件昂贵且密度有限,而使用不同外延通道的单片制作可能很昂贵。为了解决这些问题,本公开描述了可以通过利用刻面相关外延生长在单个外延步骤中(或在有限数量的外延步骤中)实现的多色led阵列。p刻面生长几乎可以完全抑制,而c刻面在某些生长条件下生长。p刻面生长可以在其他生长条件下启用。p刻面可用于通过形成金字塔来终止生长,所述金字塔的高度和层取决于器件生长区域的尺寸。

23.即,本公开提出利用在外延生长期间出现的刻面。如上所述,当使用选择的区域方法生长外延时(例如,当使用选择性区域生长(sag)掩模时),外延将在刻面上生长,并且想法是利用基于刻面的生长来限制某些结构(例如,led)只生长所需的量子阱,以产生与该结构相关的光色。因此,本公开描述了在生长外延结构时使用选择性区域生长的刻面相关生长属性来自终止某些像素,使得不同像素终止于生长的不同部分并且像素仅包括所需的那些量子阱以产生光的适当颜色。

24.图1是led结构100的一部分的截面示意图,其包括支撑一个或多个体或预备层120的半导体衬底或垫板110。有源量子阱(qw)区130形成在体或预备层120上。体或预备层120例如是材料的厚层或两种或更多种材料的结构,其被配置用于提供降低的晶格失配和/或热膨胀系数失配的影响和/或过滤从半导体垫板110到有源qw区130的缺陷。在实施例中,有源qw区包括多个量子阱。

25.通过调整体或预备层120的材料组成,可以在有源qw区130的材料选择中获得更大的灵活性,从而使得能够实现形成具有所需发光特性的有源区。最后,一个或多个p层140沉积在有源qw上以形成p-n二极管并为led结构100提供电子接触。p层140包括p掺杂层和/或接触层。led结构100然后可以被蚀刻或以其他方式成形以形成用于指定应用的期望的微型led形状因数。

26.图2是根据本公开的方面的led阵列200的一部分的平面图,该led阵列200包括作为用于显示器的阵列的一部分的多个微型led结构。如图2所示,led阵列200包括支撑在衬底240上并且例如分别以红色、绿色和蓝色波长发射的多个微型led结构210、220和230。微型led结构210、220和230中的每一个都是led结构100的示例。虽然图2中仅示出了4

×

4的led阵列,但是led阵列200可以是形成例如显示器的更大的发射体阵列的一部分,并且可以针对特定应用调整像素的排列、它们的形状、它们的数量、它们的尺寸以及它们对应的波长发射。显示器可以是高分辨率、高密度显示器,诸如在光场应用中使用的显示器。

27.特别地,为了实现高密度的发射体或彼此紧密接近的特定数量的发射体的阵列,可能希望能够在以单片集成的方式在相同的衬底上形成微型led结构210、220和230。也就是说,不是在单独的衬底上形成每种类型的微型led结构(例如,在第一衬底上的一个或多个发射红光的微型led,在第二衬底上的一个或多个发射绿光的微型led,以及在第三衬底上的一个或多个发射蓝光的微型led),然后将每个微型led转移到第四衬底以形成用作显示器的微型led阵列,所有三种类型的微型led的阵列直接形成在单个衬底上。换言之,不是在单独的晶片上形成每种颜色的微型led 210、220和230并且将每个led转移到另一个衬底以形成如图2所示的led阵列200,可以通过从一开始就在单个衬底上形成微型led结构210、220和/或230来实现更高密度的led阵列。

28.图3是包括有源mqw区330的微型led结构300的截面示意图。包括有源mqw区330的微型led结构300是led结构100和有源mqw区130的相应示例。微型led结构300包括有源mqw区330,包括由势垒层334(例如,gan或ingan势垒层)隔开的有源qw区332。每个有源qw区332可以包括单层材料,或者两层或更多层不同的材料。虽然有源qw区332和势垒层334的重复堆叠的4个集合示出在有源mqw区330内,但是可以包括更少或更多数量的叠层,这取决于所需的发光性能。

29.图4是根据本公开的方面的显示器件400的截面示意图,其是通过选择性区域生长(sag)开口宽度的led颜色选择的示例。显示器件400包括衬底405,其上支撑有发射体401和402。在实施例中,显示器件400还包括发射体403。发射体401包括产生第一光谱范围内的照明(例如,蓝光)的第一类型的led。发射体402包括产生第二光谱范围内的照明(例如,绿光)的第二类型的led。发射体403包括产生第三光谱范围内的照明(例如,红光)的第三类型的led。

30.在实施例中,发射体401、402和403使用单次外延生长通道外延生长。发射体401、

402和403通过使用放置在衬底405上方的sag掩模430限定开口而生长,衬底405可以是例如半导体晶片或与led制作工艺兼容的另一衬底。sag掩模430包括孔431和432。这里术语sag掩模内的开口和孔可互换使用。在实施例中,sag掩模430还包括孔433,在这种情况下,显示设备还包括发射体403。

31.衬底405包括缓冲层410并且还可以包括空穴阻挡层(hbl)420,其中每个都可以由n型半导体材料形成。在实施例中,空穴阻挡层420由algalnn形成。空穴阻挡层420用于减少有源qw区之间可能发生的串扰量。

32.在实施例中,外延生长包括沉积势垒层441、有源qw区443、势垒层444、有源qw区452和势垒层453。在实施例中,外延生长还包括沉积空穴阻挡层442和451中的至少一个。当显示器件400包括发射体403时,外延生长包括有源qw区462和势垒层463的沉积。在实施例中,外延生长还包括空穴阻挡层的沉积461。层441、442、444、451和461中的至少一个可以由n型半导体形成。在一些实施方式中,n型势垒可以设置在可选的n型空穴阻挡层和任何量子阱之间。

33.在实施例中,sag掩模430防止沉积材料在相邻发射体之间的积累,使得上述外延沉积仅粘附到由sag掩模430的孔(诸如孔431-433)暴露的衬底405的区域。因此,层441、442、有源qw区443和层444的沉积导致相应的层441(1,2,3)-444(1,2,3)在孔431-433内或与孔431-433对齐,如图4所示。同样,层451、有源qw区452和层453的沉积导致相应的层451(1,2)-453(1,2)在孔432和433内或与孔432和433对齐,如图4所示。层461-463中的每一个仅是发射体403的一部分,如在沉积——在势垒层453沉积之后中的这种状态下,发射体401和402中的每一个都太窄而不能支撑任何附加层的粘附。

34.在实施例中,外延生长还包括p型电子阻挡层471、p型层472和欧姆接触层473的沉积。层471(1、2、3)是层471的相应部分;层472(1,2,3)是层472的相应部分;和层471(1、2、3)是层473的相应部分。在实施例中,以下中的至少一个:(i)发射体401-403包括相应的层471(1)-471(3);(ii)发射体401-403包括相应的层472(1)-472(3),并且(iii)发射体401-403包括相应的层473(1)-473(3)。

35.在结构终止之前发射体402包括n型势垒层441(2)、空穴阻挡层442(2)(在某些实施例中)、有源qw区443(2)、n型势垒层444(2)、空穴阻挡层451(1)(在某些实施例中)、有源qw区452(1)和势垒层453(1)。在发射体402中,n型势垒层444(2)防止电流跨有源qw区443(2)流动,因此抑制从那里发光。

36.在实施例中,有源qw区443和452在单个外延生长通道中形成,使得构成qw区443和452的材料和层的相应晶格参数(例如,晶格常数和/或晶格角)相似。在实施例中,构成有源qw区443和452的材料的对应晶格常数和/或晶格角相差小于百分之五。

37.有源qw区130和330是有源qw区443(1-3)和有源qw区452(1,2)的示例。qw区443具有跨越第一光谱范围的发射光谱。qw区452具有跨越第二光谱范围的发射光谱,在实施例中,该发射光谱不同于qw区443的第一光谱范围。在实施例中,第一和第二光谱范围中的每一个是可见电磁光谱的红色、绿色和蓝色区中的一个同时也是不同的区,使得第一和第二光谱范围一起跨越红色、绿色和蓝色区中的两个。

38.在结构终止之前,发射体403包括n型势垒层441(3)、空穴阻挡层442(3)(在某些实施例中)、有源qw区443(3)、n型势垒层444(3)、空穴阻挡层451(2)(在某些实施例中)、有源

qw区452(2)、势垒层453(2)、空穴阻挡层461、有源qw区462和n势垒层463。在发射体403中,n型势垒层444(3)防止电流跨有源qw区443(3)流动,并因此抑制从那里发光。类似地,n型势垒层453(2)防止电流跨有源qw区452(2)流动,因此抑制从那里发光。

39.有源qw区130和330是有源qw区462的示例,其具有跨越第三光谱范围的发射光谱,该第三光谱范围可能不同于有源qw区443(1-3)和451(1,2)的第一和第二光谱范围中的每一个。在实施例中,第一光谱范围包括电磁光谱的蓝色区,第二光谱范围包括电磁光谱的绿色区,第三光谱范围包括电磁光谱的红色区。发射光谱的其他组合是可能的。

40.完整的外延生长反映在发射体403的结构中,发射体403的结构在有源qw区443、452和461的生长之前没有终止。相反,发射体402的结构在有源qw区462生长之前终止(例如,由于各层的刻面生长机制)。类似地,发射体401的结构在有源qw区452和461两者生长之前终止。

41.在实施例中,发射体401包括p型电子阻挡层471(1)、p型接触层472(1)和金属(欧姆)接触层473(1)中的至少一个,它们是层471-473沉积后保留的相应部分。在实施例中,发射体402包括p型电子阻挡层471(2)、p型接触层472(2)和金属(欧姆)接触层473(2)中的至少一个。在实施例中,发射体403包括p型电子阻挡层471(3)、p型接触层472(3)和金属(欧姆)接触层473(3)中的至少一个。在实施例中,p型层471和472中的至少一个被部分或全部去除,除了在p欧姆接触层473下方之外。

42.图4表示层组440(1-3)、450(1,2)、460和470(1-3)。层组440(1-3)包括相应的层441(1-3)、443(1-3)、444(1-3),并且在实施例中包括层442(1-3)。例如,层组440(1)包括层441(1)、443(1)、444(1),并且在实施例中包括层442(1)。图4表示层组440(1-3),其包括相应的层441(1-3)、443(1-3)、444(1-3),并且在实施例中,包括层442(1-3)。层组450(1)包括相应的有源层452(1)、453(1)、454(1),并且在实施例中包括层451(1)。层组450(2)包括相应的有源层452(2)、453(2)、454(2),并且在实施例中包括层451(2)。层组460包括有源有源qw区462和层463,并且在实施例中,包括空穴阻挡层461。

43.如显示器件400所示,sag掩模为不同类型的led提供不同尺寸的开口。在这个示例中,存在狭窄的开口(例如,用于蓝色led)、较宽的开口(例如,用于绿色led)和最宽的开口(例如,用于红色led)。外延生长工艺的外延层生长在sag掩模的开口中。在实施例中,sag掩模430由sic2或si3n4形成。

44.当开口较小时,如本示例中的发射体401的情况,由于与外延生长相关的刻面角,生长区域随着生长的进行而缩小,直到在有源qw区443(1)生长之后但在其上有源qw区452的一部分生长之前到达终止点。

45.通过使孔径432大于孔径431,如本示例中发射体402的情况,生长终止点出现在有源qw区443(2)和有源qw区452(1)都生长之后。此外,使孔径433大于孔径432,如发射体403的情况,生长终止点出现在所有三个有源量子阱区生长——即有源qw区443(3)、451(2)和462——之后。

46.这种方式可以具有三种不同的结构,例如发射体401-403,每个分别具有不同的相应有源qw区:有源qw区443(1)、451(1)和462。一旦形成结构,就可以在所有结构上生长p型接触层472,然后放置欧姆接触层473。发射体401-403,其可以通过使用单个外延生长通道形成,因此被配置为在三个不同的光谱区中发射光,例如蓝色、绿色和红色波长。

47.图5是显示器件500的横截面示意图,该显示器件500是显示器件400的示例,其中led颜色选择是通过控制sag孔径宽度和每个孔径下方的衬底内的凹槽的深度来实现的。显示器件500包括衬底505和其上的发射体501和502。在实施例中,显示设备500还包括发射体503。衬底505是衬底405的示例,并且包括缓冲层510,并且在实施例中,在其上包括空穴阻挡层520。缓冲层510、空穴阻挡层520是缓冲层410、空穴阻挡层420的相应示例。发射体501-503是发射体401-403的相应示例。图5包括衬底505上的sag掩模530。sag掩模530是sag掩模430的示例,并且可以用于选择性孔径蚀刻工艺以制作显示器件500。

48.发射体501包括层541(1)、543(1)和544(1),其是发射体401的层441(1)、443(1)和444(1)的相应示例。此外,发射体501还包括层571(1)-573(1)中的至少一个,其是图4层471(1)-473(1)的相应示例。发射体502包括层541(2)、543(2)、544(2)、552(1)和553(1),其是发射体402的层441(2)、443(2)、444(2)、452(1)和453(1)的相应示例。在实施例中,发射体502还包括层571(2)-573(2)中的至少一个,其是图4层471(2)-473(2)的相应示例。发射体503包括层541(3)、543(3)、544(3)、552(2)、553(2)、562和563,其是发射体403的层441(3)、443(3)、444(3)、452(3)和453(3)、462和463的相应示例。在实施例中,发射体503还包括层571(3)-573(3)中的至少一个,其是图4层471(3)-473(3)的相应示例。在实施例中,发射体501-503包括相应的层542(1-3),其是图4层442(1-3)的相应示例。在实施例中,发射体502和503包括相应的层551(1)和551(2),其是图4层451(1)和451(2)的相应示例。

49.在制作发射体501之前,衬底505被蚀刻以形成具有深度511和宽度516的凹槽513。发射体501至少部分地包含在凹槽513中,使得凹槽513相对于空穴阻挡层520的顶面529降低了发射体501的轮廓或高度。在制作发射体502之前,晶片或衬底被蚀刻以形成具有深度512和宽度516的凹槽514。发射体502至少部分地包含在凹槽514中,使得凹槽514降低发射体502的高度轮廓,使得相对于顶面529,发射体501和502的相应高度基本上相等,例如在百分之五以内。在制作发射体503之前,还蚀刻衬底505以形成凹槽515,其具有深度512和宽度518。发射体503至少部分地包含在凹槽515中。相对于顶面529,发射体503的高度超过发射体501和502的高度。

50.在实施例中,以下中的至少一个:宽度517超过宽度516和深度512超过深度511。在实施例中,宽度518超过宽度517。在实施例中,凹槽深度511和512相等。

51.如该示例所示,发射体502比衬底505中的发射体501更深,使得当外延生长完成时,发射体501和502在顶面529上方具有大致相同的高度。因此,发射体501和502的相应的顶面是共面的,因此便于随后的处理,诸如平面化和将得到的发射体转移到其他衬底。第二个好处是,对于发射体502,其p型接触层572(2)和接触(欧姆)金属573(2)不接触有源qw区543(2),因此发生在发射体502中激发来自qw区543(2)的发射的机会更小。相比之下,在显示器件400中,发射体402的p型接触层472(2)与有源qw区443(2)相邻。为了避免从发射体402中的qw区443(2)无意激发光任务,p-型接触层472(2)的部分被去除,例如,被蚀刻掉,使得p-型接触层472(2)的任何部分都没有与有源qw区443(2)相邻。

52.图6是根据本公开的方面的显示器件600的截面示意图,其示出了通过sag开口深度的led颜色选择的示例。显示器件600包括衬底605和其上的发射体601和602。在实施例中,显示器件600还包括发射体603。衬底605是衬底405的示例,并且包括缓冲层610,并且在实施例中,在其上包括空穴阻挡层620。缓冲层610和空穴阻挡层620是缓冲层410和空穴阻

挡层420的相应示例。发射体601-603是发射体401-403的相应示例。图6包括在衬底605上的sag掩模630。sag掩模630是sag掩模430的示例,并且可以用于选择性孔径蚀刻工艺以制作显示器件600。

53.发射体601包括层641(1)、643(1)和644(1),其是发射体401的层441(1)、443(1)和444(1)的相应示例。在实施例中,发射体601还包括层671(1)-673(1)中的至少一个,其是图4层471(1)-473(1)的相应示例。发射体602包括层641(2)、643(2)、644(2)、652(1)和653(1),其是发射体402的层441(2)、443(2)、444(2)、452(1)和453(1)的相应示例。在实施例中,发射体602还包括层671(2)-673(2)中的至少一个,其是图4层471(2)-473(2)的相应示例。发射体603包括层641(3)、643(3)、644(3)、652(2)、653(2)、662和663,其是发射体403的层441(3)、443(3)、444(3)、452(3)和453(3)、462和463的相应示例。在实施例中,发射体603还包括层671(3)-673(3)中的至少一个,其是图4层471(3)-473(3)的相应示例。在实施例中,发射体601-503包括相应的层642(1-3),其是图4层442(1-3)的相应示例。在实施例中,发射体602和603包括相应的层651(1)和651(2),其是图4层451(1)和451(2)的相应示例。

54.在该示例中,发射体601-603中的每一个通过首先将相应的凹槽613-615蚀刻到衬底605中来生长,其中凹槽的相应深度611-613对于每个发射体601-603是不同的以提供共面结构。例如,发射体601从蚀刻深度611生长,该蚀刻深度611小于用于发射体602的蚀刻深度612,该蚀刻深度612小于发射体603的蚀刻深度613。因此,发射体601-603中的每一个从在衬底605内的不同的相应深度生长使得发射体601-603的相应顶面是共面的。因此,在每个发射体601-603中,p型接触层672仅与发射体的最上面的有源qw区接触或与其水平相邻,即,有源qw区在垂直于衬底605的顶面的垂直方向上最靠近p接触层672。凹槽613-615具有相应的宽度616-618。在实施例中,以下中的至少一个:(i)宽度618超过宽度617和(ii)深度613超过深度612。

55.另外或替代地,上述发射体可以在基座上生长。这仍然可以使用sag掩模来完成,例如,可能需要生长基座来生长缓冲层以提高晶体质量。图7是根据本公开的方面的显示器件700的横截面示意图,其示出了通过基座宽度的led颜色选择的示例。显示器件700是显示器件400的示例并且包括发射体701,702,并且在实施例中,发射体703生长在单独的基座上。发射体701-703是发射体401-403的相应示例。

56.发射体701包括衬底705(1)和层组740(1),其是图4衬底405层组440(1)的相应示例。发射体702包括衬底705(2)和层组740(2)和750(1),其是图4衬底405、层组440(2)和450(1)的相应示例。发射体703包括衬底705(3)和层组740(3)和750(2)和760,其是图4衬底405和层组440(3)和450(2)和460的相应示例。在实施例中,发射体701-703包括相应层771(1-3)、772(1-3)和773(1-3),其是图4层组471(1-3)、472(1-3)和473(1-3)的相应示例。

57.图8和9是显示器件800a、800b和900的横截面示意图,其中的每一个都是显示器件400的示例。显示器件800a、800b和900根据本公开的方面示出了具有蚀刻隔离的单个连续选择性区域生长的示例。该示例可以通过使用例如一个外延工艺和两个掩模(不包括金属层)来实现,并且其中发射体的光发射光谱由sag掩模中的孔径的宽度确定。显示器件800a、800b、900和1000中的每一个是图4中的显示器件400的示例。

58.显示器件800a包括衬底805和发射体801、802,并且在实施例中,包括其上的发射体803。衬底805包括缓冲层810,并且在实施例中,包括其上的空穴阻挡层820。层810和820

是层410和420的相应示例。图8包括衬底805上的sag掩模830。sag掩模830是sag掩模430的示例,并且可以用于选择性孔径蚀刻工艺以制作显示器件800a、800b和900。

59.发射体801包括层组840(1)和电子阻挡层871(1),其是图4层组440(1)和电子阻挡层471(1)的相应示例。发射体802包括层组840(2)、850(1)和电子阻挡层871(2),其是图4层组440(2)、450(1)和电子阻挡层471(2)的相应示例。发射体803包括层组840(3)、850(2)、860和电子阻挡层871(3),其是图4层组440(3)、450(2)、460和电子阻挡层471(3)的相应示例。

60.以下描述包括产生显示器件800a和900的显示器件800a的实施例的处理,其中显示器件800a的实施例包括发射体803。应该理解,应用于缺少发射体803的显示器件800a的实施例的类似过程导致相应地缺少从其得出的发射体的发射体803的类似显示器件800b和900。

61.显示器件800b是在其中的欧姆接触层873(1-3)沉积和在实施例中图案化之后的显示器件800a,欧姆接触层873(1-3)是欧姆接触层473(1-3)的相应示例。显示器件900是在蚀刻发射体801-803的侧壁产生相应的发射体901-903之后的显示器件800b。

62.发射体901包括层组940(1)、电子阻挡层971(1)和欧姆接触层973(3),其是在所述蚀刻之后的层组840(1)、电子阻挡层871(1)和欧姆接触层873(3)。发射体902包括层组940(2)、950(1)和电子阻挡层971(2),其是在所述蚀刻之后的层组840(2)、850(1)和电子阻挡层871(2)。发射体803包括层组940(3)、950(2)、960和电子阻挡层971(3),其是在所述蚀刻之后的层组840(3)、850(2)、860和电子阻挡层871(3)。

63.图10是显示器件1000的横截面示意图,显示器件1000是显示器件400的示例。显示器件1000包括衬底1005和在衬底1005上包括双发射体1001和1002,并且在实施例中包括双发射体1003。发射体1001-1003是发射体401-403的相应示例。衬底1005是衬底405的示例并且包括缓冲层1010,并且在实施例中包括空穴阻挡层1020。

64.双发射体1001包括两个层组1040(1a)和1040(1b),每个层组是图4层组440(1)的示例。层组1040(1a)和1040(1b)共享公共层1041(1),并且在实施例中,共享公共层1042(1),其是层441(1)和442(1)的相应示例。层组1040(1a)还包括有源qw区1043(1a)和层1044(1a),其是有源qw区443(1)和层444(1)的相应示例。层组1040(1b)还包括有源qw区1043(1b)和层1044(1b),其是有源qw区443(1)和层444(1)的相应示例。层组1040(1a)和1040(1b)可以经由其上的相应层组1070(1a)和1070(1b)独立控制,每个层组1070(1a)和1070(1b)都是图4层组470(1)的示例。

65.双发射体1002包括层组1040(2),其是图4层组440(2)的示例。双发射体1002还包括两个层组1050(1a)和1050(1b),每个层组1050(1a)和1050(1b)都是图4层组450(1)的示例。在实施例中,层组1050(1a)和1050(1b)共享公共层1051(1),其是层451(1)的示例。层组1050(1a)还包括有源qw区1052(1a)和层1053(1a),其是有源qw区452(1)和层453(1)的相应示例。层组1050(ib)还包括有源qw区1052(1b)和层1053(1b),其是有源qw区452(1)和层453(1)的相应示例。层组1050(1a)和1050(1b)可以经由其上的相应层组1070(2a)和1070(2b)独立控制,每个层组都是图4层组470(2)的示例。

66.双发射体1003包括层组1040(3)和层组1050(2),其是图4层组440(3)和450(2)的相应示例。双发射体1003还包括两个层组1060(1)和1060(2),每个层组1060(1)和1060(2)

都是图4层组460的示例。在实施例中,层组1060(1)和1060(2)共享公共空穴阻挡层1061,其是图4空穴阻挡层461的示例。层组1060(1)还包括有源qw区1062(1)和层1063(1),其是图4有源qw区462和层463的相应示例。层组1060(2)还包括有源qw区1062(2)和层1063(2),其是有源qw区462和层463的相应示例。层组1060(1)和1060(2)可以是经由其上的相应层组1070(3a)和1070(3b)独立控制,每个层组1070(3a)和1070(3b)都是图4层组470(3)的示例。

67.在使用随后蚀刻以隔离各个器件的条带或细长结构来形成结构的情况下,图10图示了沿着条带的隔离蚀刻以形成不同颜色的单个led。在该示例中,可以看出多个不同的发射体1001是通过蚀刻蓝色led条带形成的,多个不同的发射体1002器件是通过蚀刻绿色led条带形成的,并且多个不同的发射体1003器件是通过蚀刻红色led条带形成的。

68.蚀刻可用于去除p型接触层以避免p型接触层与可在顶面量子阱下方生长的任何量子阱之间的任何连接。p型接触层和其中一些量子阱之间的任何重叠都可能具有电流通过以激发其他量子阱的电势。通过执行这种类型的蚀刻,可以防止这些不希望的激发发生。

69.图11和12包括显示器件1100a、1100b、1100c和1200的横截面示意图,其图示了根据本公开的方面的具有均匀高度的单个选择性区域生长的示例。该示例可以通过使用例如一个外延工艺和三个或四个掩模(不包括金属层)来实现,并且其中颜色由sag开口宽度和深度选择。显示器件1100a、1100b、1100c和1200中的每一个是显示器件600的示例,图6。

70.显示器件1100a图示了将sag用于三个不同深度的凹槽,导致三个不同的发射体在三个不同的电磁光谱范围处操作。在图11的示例中,三个不同的发射体是图6中介绍的发射体601-603。显示器件1100b图示了显示器件制作中的金属沉积和图案化步骤。显示器件1100c图示了衬底605的隔离蚀刻用于分离不同的器件或结构(如果sag掩模是连续的),这产生了蚀刻的衬底1105。

71.在使用随后蚀刻以隔离各个器件的条带或细长结构形成结构的情况下,显示器件1200图示了沿条带的隔离蚀刻以形成在图10中介绍的发射体1001-1003。显示器件1200是显示器件1000的示例,其中发射体1001-1003在衬底1205内的不同深度处形成。衬底1205是衬底605的示例,并且至少包括层1210和1220,其是层610和620的相应示例。在实施例中,多个不同的发射体1001通过蚀刻蓝色led条带形成,多个发射体1002通过蚀刻绿色led条带形成,并且多个不同的发射体1003通过蚀刻红色led条带形成。

72.如本例所示,可以一起使用一种或多种技术。例如,可以在不同深度进行蚀刻、仅蚀刻接触金属、蚀刻到半导体衬底中或这些的某种组合。

73.图13是图示用于形成支撑在衬底上的多个光发射体的方法1300的流程图。方法1300可以被实施以形成图1-12的任何显示器件。方法1300包括步骤1310、1315、1320、1340、1350、1370和1380。在实施例中,方法1300还包括步骤1330、1360、1390、1392和1394中的至少一个。在实施例中,方法1300的每个步骤在单个外延生长通道中执行。

74.步骤1310包括在衬底上形成第一凹槽,第一凹槽具有第一宽度和第一深度。在步骤1310的示例中,凹槽513形成在图5衬底505中。步骤1315包括在衬底上形成第二凹槽。第二凹槽具有第二宽度和第二深度,第二宽度和第二深度中的至少一个分别大于第一宽度和第一深度。在步骤1310的示例中,凹槽514形成在衬底505中。

75.步骤1320包括在衬底上沉积第一n型势垒材料。在步骤1320的示例中,n型势垒层541(1)和541(2)被沉积在衬底505上。

76.步骤1330包括在第一n型势垒材料上沉积第一n型空穴阻挡层(hbl)。在步骤1330的示例中,空穴阻挡层542(1)和542(2)分别沉积在层541(1)和541(2)上。

77.步骤1340包括在第一n型势垒材料上制作第一有源量子阱(qw)结构。在步骤1340的示例中,有源qe区543(1)和543(2)分别被制作在(i)势垒层541(1)和541(2)上或(ii)空穴阻挡层542(1)和542(2)上。

78.步骤1350包括在第一有源qw结构上沉积第二n型势垒材料。在步骤1350的示例中,n型势垒层544(1)和544(2)分别沉积在有源qe区543(1)和543(2)上。

79.步骤1360包括在第二n型势垒材料上沉积第二n型hbl。在步骤1360的示例中,空穴阻挡层551(1)沉积在势垒层544(2)上。

80.步骤1370包括在第二n型势垒材料上制作第二有源qw结构。在步骤1370的示例中,在势垒层544(2)上或空穴阻挡层551(1)上制作有源qe区552(1)。

81.步骤1380包括在第二有源qw结构上沉积第三n型势垒材料。在步骤1380的示例中,n型势垒层553(1)沉积在有源qe区552(1)上。

82.作为步骤1310、1315、1320、1340、1350和1370的结果,第一凹槽的第一宽度和第一深度被配置为防止在第一凹槽内形成第二有源qw结构,使得第一n型势垒材料、第一有源qw结构和第二n型势垒层形成第一光发射体。第一光发射体的示例包括发射体401、501、601、701、801、901和1001。

83.作为步骤1310、1315、1320、1340、1350和1370的结果,第二凹槽的第二宽度和第二深度被配置为将第一n型势垒材料、第一有源qw结构、第二n-型势垒材料、第二有源qw结构和第三n型势垒材料支撑在第二凹槽内并且至少部分地包含在第二凹槽内,以形成第二光发射体。第二光发射体的示例包括发射体402、502、602、702、802、902和1002。

84.步骤1390包括将第一凹槽与第二凹槽电隔离,使得第一凹槽支撑第一发射体,而第二凹槽支撑第二发射体,使得第一发射体与第二发射体电隔离。如在步骤1390的示例中,去除——例如,湿法或干法蚀刻——显示器件1100b的发射体601、602和603之间的衬底605的部分,以产生显示器件1100c。

85.步骤1392包括在第一和第二led结构中的每一个上沉积p型层。在步骤1392的示例中,p型层572(1)和572(2)分别沉积在发射体501和502上。

86.步骤1394包括在第一和第二led结构中的每一个上形成p型欧姆接触。在步骤1394的示例中,欧姆接触层573(1)和573(2)分别沉积在发射体501和502上。

87.应当理解,本文描述的示例是通过说明而非限制的方式提供的。量子阱的顺序可以不同于图中所示的顺序,可以多于或少于图中所示的三个量子阱,量子阱的颜色可以不同于图中所示的颜色,并且除了图中所示的那些层之外,还可以包括可以改善led性能的不同方面的附加层。在一些实施方式中,使蓝色led较小可能是有帮助的,因为蓝光提供了由显示器产生的光的小部分并且蓝色led非常有效。在这样的实施方式中,绿色led也是有效的并且可以具有与蓝色led相似的尺寸或可能稍大一些。在这种实施方式中,红色led的效率不如蓝色led或绿色led,并且可能需要最大的器件。

88.对以上结合图1-6b描述的示例的附加考虑包括顶部接触放置、外延工艺通道(例如,外延通道)数、基于宽度、深度或宽度和深度的组合的led整体颜色选择,以及隔离器件或结构的不同方式(例如,不同颜色的单个led)。

89.器件隔离可以通过使用sag掩模中的开口隔离单个器件来实现(例如,开口阵列定义了相应led器件阵列的位置和隔离)。换句话说,每个器件或结构都是通过使用小开口在sag掩模中的两个维度上隔离的特征,并且每个开口用于生长led的结构。

90.还可以使用条带(例如,细长特征)sag,然后应用隔离蚀刻来隔离由条带结构制成的单个器件(参见例如图5b和9)。例如,器件以条带形式生长,然后在垂直于条带的方向上进行蚀刻以隔离器件。沿其长度具有不同宽度的条带是可能的,并且蚀刻使得它将不同颜色的led与同一条带隔离。

91.使用的器件隔离类型,无论是隔离sag还是带有隔离蚀刻的条带sag都可能影响器件钝化和封装密度。

92.关于顶部接触平面,它可以是c平面或非c平面。c平面是顶面、平面。在某些情况下,接触在c平面上,而在其他情况下,在非c平面上,即倾斜平面上。顶部接触平面的选择可能会影响不同颜色的相对强度。

93.关于外延工艺通道(例如,外延通道)的数量,上述示例对应于单个外延通道,所述单个外延通道提供了在不同电磁光谱范围内操作的光发射体(例如,在单个通道中的外延生长工艺将产生可以生产诸如红色、绿色和蓝色的三个颜色光的量子阱)。其他实施方式可以使得如此实施的制作方法为每个外延通道产生多于三种颜色。然而,其他实施方式可以为每个外延通道产生两种颜色,而不是为每个外延通道产生三种颜色。在又一实施方式中,一个外延通道可以产生一种颜色,而另一个外延通道可以产生两种颜色,总共三种颜色。在这种实施方式中,第一外延通道可以产生一种或两种颜色并且第二外延通道可以产生另一种或多种颜色。在又一实施方式中,可以使用两个外延通道,其中每个外延通道产生两种颜色,总共四种颜色。四色解决方案可用于提供更好的色域和功率效率。当使用多于一个外延通道时,可以应用某种形式的掩模来覆盖那些不应该应用外延通道的区域。

94.关于颜色选择性,使用宽度确定epi何时终止。因为蚀刻,使用深度控制颜色使过程更加复杂,但最终可以获得更好的平面性和颜色分离。如上面详细描述的,通过宽度、深度或两者的组合的对颜色的总体选择可以影响器件的平面度和工艺复杂性。

95.一般而言,本公开描述了各种技术和器件,这些技术和器件使得能够在同一衬底上单片集成生产不同颜色光的发光结构。

96.特征组合

97.(a1)一种显示器件,包括衬底,所述衬底在其上包括第一发射体和第二发射体。第一发射体包括第一下部有源量子阱(qw)区,所述第一下部有源量子阱(qw)区具有跨越第一光谱范围的第一发射光谱。第二发射体包括(i)上部有源qw区,所述上部有源qw区具有跨越与第一光谱范围不同的第二光谱范围的第二发射光谱,(ii)第二下部有源qw区,所述第二下部有源qw区具有第一发射光谱并且位于上部有源qw区和衬底之间,以及(iii)在第二下部有源qw区和上部有源qw区之间的势垒层,用于抑制第二下部有源qw区的发射。

98.(a2)在显示器件(a1)的实施例中,第一和第二下部有源qw区中的每一个都由晶格参数的第一集合表征。上部有源qw区由与晶格参数的第一集合中的相应参数相差小于百分之五的晶格参数的第二集合表征。

99.(a3)显示器件(a2)的实施例还包括在第二下部有源qw区和上部有源qw区之间的空穴阻挡层。

100.(a4)在显示器件(a3)的实施例中,空穴阻挡层包括n型半导体材料,

101.(a5)在显示器件(a1)-(a4)中任一项的实施例中,势垒层包括n型半导体材料。

102.(a6)在显示器件(a1)-(a5)中任一项的实施例中,第一发射体相对于衬底的顶面具有第一高度。衬底限定延伸到衬底中的凹槽。第二发射体至少部分地包含在凹槽内,使得第二发射体相对于顶面的高度等于第一高度。

103.(a7)在显示器件(a6)的实施例中,凹槽相对于顶面的深度基本上等于第一高度。

104.(a8)在显示器件(a6)和(a7)中的任一项的实施例中,衬底限定延伸到衬底中的附加凹槽,第一发射体至少部分地包含在附加凹槽内。

105.(a9)在显示器件(a1)-(a8)中任一项的实施例中,第二发射体在平行于衬底的顶面的第一方向中与第一发射体相邻,并且以下中的至少一个:(i)在第一方向上第二下部有源qw区的宽度超过第一下部有源qw区的宽度;以及(ii)第二下部有源qw区在平行于顶面的平面中的截面面积超过第一下部有源qw区的截面面积。

106.(a10)显示器件(a1)-(a9)中任一项的实施例还包括(i)多个附加的第一发射体,其与第一发射体一起形成第一发射体的阵列;(ii)多个附加的第二发射体,其与第二发射体一起形成与第一发射体阵列交错的第二发射体阵列。

107.(a11)在显示器件(a1)-(a10)中任一项的实施例中,第一发射体和第二发射体包括(i)相应的p掺杂半导体层和(ii)相应的欧姆接触层中的至少一个。

108.(b1)一种用于形成多个光发射体的方法,包括(i)在衬底上形成第一凹槽,所述第一凹槽具有第一宽度和第一深度;(ii)在衬底上形成第二凹槽,第二凹槽具有第二宽度和第二深度,第二宽度和第二深度中的至少一个分别大于第一宽度和第一深度;(iii)在衬底上沉积第一n型势垒材料;(iv)在第一n型势垒材料上制作第一有源量子阱(qw)结构;(v)在第一有源qw结构上沉积第二n型势垒材料;(vi)在第二n型势垒材料上制作第二有源qw结构;以及(vii)在第二有源qw结构上沉积第三n型势垒材料。第一凹槽的第一宽度和第一深度被配置为防止在第一凹槽内形成第二有源qw结构,使得第一n型势垒材料、第一有源qw结构和第二n型势垒层形成第一光发射体。第二凹槽的第二宽度和第二深度被配置为将第一n型势垒材料、第一有源qw结构、第二n型势垒材料、第二有源qw结构和第三n型势垒材料支撑在第二凹槽内,并至少部分包含在第二凹槽内以形成第二光发射体。

109.(b2)方法(bl)的实施例还包括,在沉积第一n型势垒材料之后和制作第一有源qw结构之前:在第一n型势垒材料上沉积第一n型空穴阻挡层(hbl)。

110.(b3)方法(b1)和(b2)中任一项的实施例还包括,在沉积第二n型势垒材料之后和制作第二有源qw结构之前:在第二n型势垒材料上沉积n型空穴阻挡层(hbl)。

111.(b4)方法(b1)-(b3)中任一项的实施例还包括将第一凹槽与第二凹槽电隔离,使得第一凹槽支撑第一发射体,而第二凹槽支撑第二发射体,使得第一发射体与第二发射体电隔离。

112.(b5)方法(b4)的实施例还包括以下中的至少一项:(i)在第一和第二led结构中的每一个上沉积p型层,以及(ii)在第一和第二led结构中的每一个上形成p型欧姆接触。

113.(b6)在方法(b1)-(b5)中任一项的实施例中,沉积和制作的每个步骤在单个外延生长通道中执行。

114.在不脱离本实施例的范围的情况下,可以对上述方法和系统进行改变。因此应当

注意,包含在以上描述中或在附图中示出的内容应当被解释为说明性的而不是限制性的。在本文中,除非另有说明,否则短语“在实施例中”等同于短语“在某些实施例中”,而不是指所有实施例。所附权利要求旨在覆盖本文所述的所有通用和特定特征,以及本方法和系统的范围的所有陈述,就语言而言,可以说落入它们之间。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1