使用外延形成的堆叠像素结构的制作方法

1.在此描述的实例一般涉及半导体处理领域,更具体地,涉及使用外延生长工艺形成堆叠像素结构(stacked pixel structure)。

背景技术:

2.图像传感器通常用于各种应用,例如数码相机。图像传感器通常包括排列成阵列的多个像素传感器。光从一个或多个物体反射或产生并被图像传感器接收。图像传感器提供信号输出,所述信号输出具有对应于阵列内每个像素传感器的光强度水平的幅度(magnitude)。

3.传统的彩色图像传感器使用彩色滤光器马赛克来选择不同光电二极管位置的不同波段。用于这些彩色滤光器马赛克的光电二极管经布置检测尽可能宽的色谱范围,同时使用彩色滤光器将检测限制为单一所需颜色。彩色滤光器马赛克的一个实例是拜耳(bayer)彩色滤光器阵列。新近的彩色图像传感器已经转向检测不同颜色的堆叠像素。然而,这些新近的图像传感器遇到了制造问题,可能会阻止这些图像传感器的大规模实施。

技术实现要素:

4.本公开内容的实例包括用于半导体处理的方法。第一传感器层在基板上的结晶表面(crystalline surface)上外延生长。第一隔离结构(isolation structure)在第一传感器层上外延生长。第二传感器层在第一隔离结构上外延生长。第二隔离结构在第二传感器层上外延生长。第三传感器层在第二隔离结构上外延生长。

5.本公开内容的实例还包括一种非暂时性存储介质。该非暂时性存储介质存储指令,当处理器执行所述指令时,使该处理器施行以下步骤:在处理腔室中控制在基板的结晶表面上的外延生长第一传感器层;在该处理腔室中控制该第一传感器层上的外延生长第一隔离结构;在该处理腔室中控制在第一隔离结构上的外延生长第二传感器层;在该处理腔室中控制在该第二传感器层上的外延生长第二隔离结构;和在该处理腔室中控制在该第二隔离结构上的外延生长第三传感器层。

6.本公开内容的实例进一步包括堆叠像素结构的器件结构。该堆叠像素结构包括:第一外延传感器层,该第一外延传感器层设置在基板上的结晶表面上;第一外延隔离结构,该第一外延隔离结构设置在该第一外延传感器层上;第二外延传感器层,该第二外延传感器层设置在该第一外延隔离结构上;第二外延隔离结构,该第二外延隔离结构设置在该第二外延传感器层上;和第三外延传感器层,该第三外延传感器层设置在该第二外延隔离结构上。

附图说明

7.本公开内容的特征已简要概述于前,并在以下有更详尽的讨论,可通过参考实例以作了解,部分的实例绘示于所附附图中。然而,要注意的是,附图仅示出了一些实例,因此

不应被认为是对本公开内容范围的限制,因为本公开内容可以允许其他同样有效的实例。

8.图1绘示根据一些实例设置在基板上的堆叠像素结构的横截面。

9.图2绘示根据一些实例设置在基板上的另一堆叠像素结构的横截面。

10.图3绘示作为根据一些实例的堆叠像素结构的示例性隔离结构的量子阱(quantum well)层。

11.图4绘示作为根据一些实例的堆叠像素结构的示例性隔离结构的结晶介电层。

12.图5绘示作为根据一些实例的堆叠像素结构的示例性隔离结构的超晶格(superlattice)结构。

13.图6是根据一些实例的形成堆叠像素结构的方法的流程图。

14.图7是根据一些实例的形成包括堆叠像素结构的器件结构的方法的流程图。

15.图8是根据一些实例根据图7的方法形成的器件结构的横截面。

16.图9是根据一些实例的形成包括堆叠像素结构的器件结构的方法的流程图。

17.图10是根据一些实例的根据图9的方法形成的器件结构的横截面。

18.图11是根据一些实例的形成包括堆叠像素结构的器件结构的方法的流程图。

19.图12是根据一些实例的根据图11的方法形成的器件结构的横截面。

20.图13是根据一些实例的可用于施行外延生长的处理腔室的截面图。

21.图14是根据一些实例的处理系统的示意性俯视图。

22.为便于理解,在可能的情况下,使用相同的附图标记代表图标中相同的元件。

具体实施方式

23.一般来说,本文描述的实例涉及用于使用外延生长工艺来形成堆叠像素结构的方法和处理腔室和系统以及由此形成的器件结构。在一些实例中,可以通过以下步骤形成堆叠像素结构:在基板上外延生长第一传感器层;在该第一传感器层上外延生长第一隔离结构;在该第一隔离结构上外延生长第二传感器层;在该第二传感器层上外延生长第二隔离结构;和在该第二隔离结构上外延生长第三传感器层。堆叠像素结构可以实现为图像传感器的像素阵列中的像素。

24.堆叠像素技术可以允许更多的光到达像素阵列中的像素,因为可以省略可以吸收光的彩色滤光器的使用。一般来说,堆叠像素结构中的传感器层可以基于层的布置和厚度以及传感器层的自然特性经配置吸收适当波长的光(例如,红(r)光、绿(g)光和蓝(b)光)。这可以避免对以前在传统图像传感器以能够检测特定波长的光中需要的彩色滤光器的需求。此外,堆叠像素技术可以实现更高密度的阵列和/或更大的像素尺寸,因为给定区域可以实现多个颜色的像素,而不是传统图像传感器中的单一颜色。甚至更进一步,堆叠像素技术可以在相同图像传感器芯片上实现诸如rgb加近红外(nir)等先进技术。

25.这里描述的一些实例可以具有额外的好处和优点。使用如本文所述的外延生长形成的堆叠像素结构可以产生易于成比例的(scaled)薄结构。隔离结构可以相对于堆叠像素结构为薄,且可以提供量子限制(quantum confinement)和材料绝缘。层与层之间的界面可以通过外延生长来精确定义,且各种材料可以用于材料工程的各种层。此外,对层使用外延生长可以避免可能由其他形成方法引起的晶体损伤,如可能由掺杂剂注入引起。可以获得其他好处和优点。

26.以下描述各种不同的实例。尽管可在处理流程或系统中一起描述不同实例的多个特征,但是多个特征可以各自单独地或个别地和/或在不同的处理流程或不同的系统中实现。另外,描述各种处理流程按顺序施行;其他实例可以以不同的顺序以和/或以更多或更少的操作来实施处理流程。

27.图1绘示根据一些实例设置在基板50上的堆叠像素结构的横截面。基板50可以是任何合适的半导体基板,例如大块基板(bulk substrate)、绝缘体上半导体(soi)基板等。在一些实例中,基板50是整块(bulk)硅晶片。基板尺寸的实例包括200mm直径、300mm直径、400mm直径和450mm直径等。基板50包括结晶表面52,堆叠像素结构形成于结晶表面52上。结晶表面52可以在基板50的正面上(在其中和/或上面形成器件,如晶体管),或者可以在基板50的与正面相对的背面上。结晶表面52为结晶表面(如单晶体表面),例如si(100)、si(110)或si(111),当基板50为整块硅晶片时,其被用作用于随后外延生长的模板(template)。在一些实例中,基板50进一步包括形成结晶表面52的外延缓冲层。在一些实例中,结晶表面52可以形成在基板50的正面或背面上的沟槽(如沟槽的底表面)中。

28.第一传感器层54设置在基板50的结晶表面52上。在一些实例中,第一传感器层54是外延生长的半导体材料,如硅、硅锗等。外延生长的半导体材料可以被掺杂(如通过原位掺杂),其视需要的光子吸收和电荷产生而定。这些实例中的外延生长的半导体材料是从基板50的结晶表面52外延生长的,例如通过减压外延(rpe)、液相外延(lpe)、分子束外延(mbe)、金属有机化学气相沉积(mocvd)、低压化学气相沉积(lpcvd)等。

29.第一隔离结构56设置在第一传感器层54上。第一隔离结构56通常在其间设置第一隔离结构56的层之间提供一定程度的电隔离(electrical isolation)。在一些实例中,第一隔离结构56进一步在其间设置第一隔离结构56的层之间提供一定程度的光学隔离。第一隔离结构56可以是一个或多个量子阱或绝缘体材料(例如,结晶介电材料)或包括一个或多个量子阱或绝缘体材料(例如,结晶介电材料)。下面描述隔离结构的实例的额外细节。在一些实例中,第一隔离结构56是可通过rpe、lpe、mbe、mocvd、lpcvd、原子层外延(ale)等生长的一个或多个外延生长材料或包括可通过rpe、lpe、mbe、mocvd、lpcvd、原子层外延(ale)等生长的一个或多个外延生长材料。

30.第二传感器层58设置在第一隔离结构56上。在一些实例中,第二传感器层58是外延生长的半导体材料,如硅、硅锗等。外延生长的半导体材料可以被掺杂(如通过原位掺杂),其视需要的光子吸收和电荷产生而定。在这样的实例中,外延生长的半导体材料是从第一隔离结构56如通过rpe、lpe、mbe、mocvd、lpcvd等外延生长的。

31.第二隔离结构60设置在第二传感器层58上。第二隔离结构60通常在其间设置第二隔离结构60的层之间提供一定程度的电隔离。在一些实例中,第二隔离结构60进一步在其间设置第二隔离结构60的层之间提供一定程度的光学隔离。第二隔离结构60可以是一个或多个量子阱或绝缘体材料(例如,结晶介电材料)或包括一个或多个量子阱或绝缘体材料(例如,结晶介电材料)。下面描述隔离结构的实例的额外细节。在一些实例中,第二隔离结构60是可通过rpe、lpe、mbe、mocvd、lpcvd、ale等生长的一个或多个外延生长材料或包括可通过rpe、lpe、mbe、mocvd、lpcvd、ale等生长的一个或多个外延生长材料。

32.第三传感器层62设置在第二隔离结构60上。在一些实例中,第三传感器层62是外延生长的半导体材料,如硅、硅锗等。外延生长的半导体材料可以被掺杂(如通过原位掺

杂),其视需要的光子吸收和电荷产生而定。在这样的实例中,外延生长的半导体材料是从第二隔离结构60如通过rpe、lpe、mbe、mocvd、lpcvd等外延生长的。

33.第一传感器层54、第一隔离结构56、第二传感器层58、第二隔离结构60和第三传感器层62在垂直于(normal to)基板50的结晶表面52的方向上具有各自的厚度64、66、68、70、72。厚度66、70可以很小。例如,量子阱的形成或绝缘体的隔离性质在理论上与这种量子阱或绝缘体的厚度无关,且因此,在一些实例中,厚度66、70可以尽可能小。例如,在一些实例中,厚度66、70可以累积小于堆叠像素结构的总厚度(如厚度64、66、68、70、72的总和)的5%。在其他实例中,厚度66、70可以是任何量。

34.第一传感器层54、第二传感器层58和第三传感器层62的厚度64、68、72分别可以是给定层经配置吸收并从中产生电荷的光的波长的函数。可采用较小的厚度来吸收较短波长的光(如蓝光),而可采用较大的厚度来吸收较长波长的光(如红光)。相对于通常在较深的入射深度内吸收的较长波长的光,较短波长的光通常在较浅的入射深度内被吸收。图1绘示照明方向74。方向74是入射在堆叠像素结构上的光的传播方向。如图所示,光在方向74上传播通过基板50以入射在结晶表面52处的堆叠像素结构上。第一传感器层54经配置吸收较短波长的光(如蓝光);第二传感器层58经配置吸收中等波长的光(如绿光);及第三传感器层62经配置吸收较长波长的光(如红光)。因此,如图所示,第一传感器层54的厚度64小于第二传感器层58的厚度68,第二传感器层58的厚度68小于第三传感器层62的厚度72。第一传感器层54、第二传感器层58和第三传感器层62的各自材料和/或掺杂也可以基于第一传感器层54、第二传感器层58和第三传感器层62分别经配置所吸收的光的波长。

35.如前所述,该堆叠像素结构的每一层或结构可以外延生长。在这样的实例中,可以精确地控制这样的层和结构的形成。这可以在相邻层和相邻结构之间产生精确、鲜明的(sharp)界面。此外,隔离结构可以形成得很薄。例如,第一隔离结构56和第二隔离结构60的厚度66、70可以各自等于或小于第一传感器层54、第一隔离结构56、第二传感器层58、第二隔离结构60和第三传感器层62的厚度64、66、68、70、72的总和的百分之一。这可以进一步导致堆叠像素结构相对于其他类似结构相对薄,这可以允许堆叠像素结构容易地根据其他应用成比例缩放(scaled)。此外,实施外延生长可以允许原位掺杂,这可以避免使用掺杂剂的注入。这可以允许堆叠像素结构具有改良的晶体结构,因为可以避免掺杂剂注入对晶体结构造成的损坏。

36.图2绘示根据一些实例设置在基板50上的堆叠像素结构的横截面。通常,与图1相比,堆叠像素结构的层和结构相对于基板50和结晶表面52的定向(orientation)是翻转的(flipped)。

37.第三传感器层62设置在基板50的结晶表面52上。在一些实例中,第三传感器层62的外延生长的半导体材料从基板50的结晶表面52外延生长。第二隔离结构60设置在第三传感器层62上。第二传感器层58设置在第二隔离结构60上。在一些实例中,第二传感器层58的外延生长的半导体材料从第二隔离结构60外延生长。第一隔离结构56设置在第二传感器层58上。第一传感器层54设置在第一隔离结构56上。在一些实例中,第一传感器层54的外延生长的半导体材料从第一隔离结构56外延生长。

38.图2进一步说明了照明方向74。如图所示,光在方向74上传播并且入射在远离结晶表面52的第一传感器层54的表面上。鉴于以上图1的描述,本领域技术人员将容易理解图2

的其他方面。

39.在一些实例中,图1中的第一传感器层54和图2中的第三传感器层62可以形成为除了基板50上外延生长相应层之外的基板50的部分,或者形成为替代基板50上外延生长相应层的基板50的部分。

40.图3、4和5绘示堆叠像素结构的不同示例性隔离结构。图3、4和5中的各图绘示下面的(underlying)传感器层102和上面的(overlying)传感器层104的相应部分。在图3、4和5的各图中,隔离结构设置在下面的传感器层102和上面的传感器层104之间。下面的传感器层102靠近基板50的结晶表面52,而上面的传感器层104远离结晶表面52。下面的传感器层102可以是例如图1所示的堆叠像素结构的定向上的第一传感器层54或第二传感器层58,且可以是如图2所示的堆叠像素结构的定向上的第三传感器层62或第二传感器层58。上面的传感器层104可以是例如图1所示的堆叠像素结构的定向上的第二传感器层58或第三传感器层62,且可以是如图2所示的堆叠像素结构的定向上的第二传感器层58或第一传感器层54。图3、4和5中的隔离结构可以是图1和2中的第一隔离结构56和第二隔离结构60中的任何一个。此外,第一隔离结构56和第二隔离结构60可以是图3、4和5中的隔离结构的任何一者,包括图3、4和5中的隔离结构的任何混合。例如,第一隔离结构56可以是图3中的隔离结构,而第二隔离结构60可以是图3、4和5中的隔离结构的任何一者。而且,第一隔离结构56可以是图4中的隔离结构,而第二隔离结构60可以是图3、4和5的隔离结构中的任何一个。甚至更进一步,第一隔离结构56可以是图5中的隔离结构,而第二隔离结构60可以是图3、4和5的隔离结构中的任何一个。

41.参考图3,量子阱层106设置在下面的传感器层102和上面的传感器层104之间。量子阱层106具有与下面的传感器层102和上面的传感器层104不同的功函数(work function)和/或带隙能量。因此,当设置在下面的传感器层102和上面的传感器层104之间并与其相邻时,下面的传感器层102、量子阱层106和上面的传感器层104形成量子阱。量子阱在下面的传感器层102和上面的传感器层104之间提供一定程度的电隔离。

42.在一些实例中,量子阱层106比下面的传感器层102和上面的传感器层104具有更高浓度的p型掺杂剂(其中电子是信号的载流子(carrier))或更高浓度的n型掺杂剂(其中空穴(hole)是信号的载流子)。例如,下面的传感器层102和上面的传感器层104中的各者可掺杂有p型掺杂剂,且量子阱层106比下面的传感器层102和上面的的传感器层104中的各者具有更高浓度的p型掺杂剂。此外,下面的传感器层102和上面的传感器层104中的各者可以是本征(intrinsic)半导体材料(如未掺杂的),且量子阱层106可掺杂有p型掺杂剂。在一些实例中,下面的传感器层102、上面的传感器层104和量子阱层106包括相同的基底(base)本征半导体材料。作为特定实例,下面的传感器层102和上面的传感器层104均是外延本征硅,且量子阱层106是外延p型掺杂硅。在这样的实例中,p型掺杂剂可以是硼,且量子阱层106中的p型掺杂剂的浓度可以大于10

17

cm-3

,如在10

17

cm-3

至10

20

cm-3

的范围内。类似地,下面的传感器层102和上面的传感器层104中的各者可掺杂有n型掺杂剂,且量子阱层106比下面的传感器层102和上面的传感器层104中的各者具有更高浓度的n型掺杂剂。此外,下面的传感器层102和上面的传感器层104中的各者可以是本征半导体材料,且量子阱层106可掺杂有n型掺杂剂。作为特定实例,下面的传感器层102和上面的传感器层104均是外延本征硅,且量子阱层106是外延n型掺杂硅。在这样的实例中,n型掺杂剂可以是磷或砷,且量子阱层106中的

n型掺杂剂的浓度可以大于10

17

cm-3

,如在10

17

cm-3

至10

20

cm-3

的范围内。

43.此外,在这样的实例中,可以通过流动适当的前驱物气体来外延生长下面的传感器层102,且当已经达到下面的传感器层102的厚度时,启动(initiating)(例如在相同处理腔室中)p型或n型掺杂剂源气体使得量子阱层106在原位掺杂外延生长。当达到量子阱层106的厚度时,可以停止p型或n型掺杂剂源气体,以及可以开始上面的传感器层104的生长。

44.在一些实例中,量子阱层106是不同于下面的传感器层102和上面的传感器层104的半导体材料。量子阱层106的半导体材料的带隙能量不同于(如大于或小于)下面的传感器层102和上面的传感器层104的带隙能量。值得注意的是,不同的半导体材料可以具有不同的自然晶格常数。当量子阱层106在下面的传感器层102上外延生长并且具有与下面的传感器层102不同的自然晶格常数时,在一些实例中,量子阱层106可以不超过其临界厚度。如果量子阱层106超过其临界厚度,则可以在量子阱层106中形成晶体缺陷。这种晶体缺陷可能传播到在量子阱层106上外延生长的任何上面的层,如上面的传感器层104。此外,如果量子阱层106的厚度没有超过其临界厚度,则量子阱层106可能会发生应变(strained)。经受应变的量子阱层106可能会影响量子阱层106的带隙能量。各种层的材料和量子阱层106的厚度的选择可以考虑这些考虑。作为特定实例,下面的传感器层102和上面的传感器层104均是外延本征硅,且量子阱层106是外延硅锗(sige)、锗(ge)、磷化硅(sip)、掺硼的硅(si:b)、掺磷的硅(si:p)、掺砷的硅(si:as)、掺碳的硅(si:c)等。

45.此外,在这样的实例中,可以通过为下面的传感器层102流动适当的前驱物气体来外延生长下面的传感器层102。当已经达到下面的传感器层102的厚度时,可以停止那些前驱物气体的流动,以及可以启动用于量子阱层106的适当的前驱物气体的流动。当已经达到量子阱层106的厚度时,可以停止那些前驱物气体的流动,以及可以启动用于上面的传感器层104的适当前驱物气体的流动。这些不同前驱物气体的流动以外延生长下面的传感器层102、量子阱层106和上面的传感器层104可以在同一处理腔室中施行。

46.在进一步的实例中,量子阱层106可以包括与下面的传感器层102和上面的传感器层104不同的基底(base)本征半导体材料,且比下面的传感器层102和上面的传感器层104具有更高的p型或n型掺杂剂浓度。可以组合上述各种方面。

47.参考图4,结晶介电层108(如单晶)设置在下面的传感器层102和上面的传感器层104之间。结晶介电层108是电绝缘的。结晶介电层108在下面的传感器层102和上面的传感器层104之间提供一定程度的电隔离。在一些实例中,结晶介电层108是结晶绝缘体材料。例如,结晶介电层108可以是结晶氧化硅。可以使用ale外延生长结晶氧化硅。例如,可以通过适当前驱物气体的脉冲(pulse)而在结晶表面上形成单层硅或含硅分子,以及随后,可以通过另一适当前驱物气体的脉冲而在单层硅或含硅分子上形成单层氧或含氧分子和/或单层氧或含氧分子对单层硅或含硅分子反应。随后可以使这些脉冲交替(alternate)以生长结晶氧化硅。像上述一样,下面的传感器层102、晶体介电层108和上面的传感器层104可以在同一处理腔室中外延生长。

48.参考图5,超晶格结构110设置在下面的传感器层102和上面的传感器层104之间。超晶格结构110具有交替的第一层112和第二层114。第一层112的半导体材料不同于第二层114的半导体材料。可以在超晶格结构110中实施任何数量的第一层112和第二层114。超晶格结构110包括多个量子阱。量子阱在下面的传感器层102和上面的传感器层104之间提供

一定程度的电隔离。

49.超晶格结构110可以进一步是布拉格光栅(bragg grating)。布拉格光栅可以作为滤光器操作。第一层112和第二层114的材料可以经选择具有适当折射率以将布拉格光栅实现为滤光器。作为实例,参考图1和图2,实现为布拉格光栅的第一隔离结构56可以经配置反射较短波长的光(如蓝光)同时允许较长波长的光通过,以及第二隔离结构60实现为布拉格光栅可以经配置反射中等波长的光(如绿光)同时允许较长波长的光通过。实现为超晶格结构110的布拉格光栅可以在下面的传感器层102和上面的传感器层104之间提供一定程度的光学隔离。实现为隔离结构的布拉格光栅可以通过使用更薄的传感器层达到改进的效率来允许堆叠像素结构更薄,因为光的波长可以被隔离结构选择性地反射到传感器层。

50.像上述一样,下面的传感器层102、超晶格结构110和上面的传感器层104可以在同一处理腔室中外延生长。对于给定的层(如下面的传感器层102、第一层112、第二层114和上面的传感器层104)可以以适当的顺序流动适当的前驱物气体以外延生长这些层。

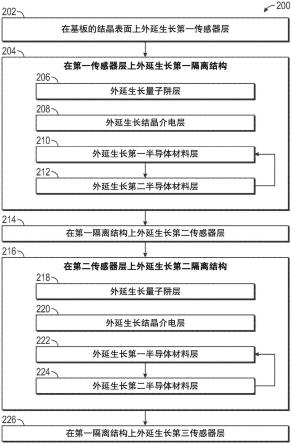

51.图6是根据一些实例的形成堆叠像素结构的方法200的流程图。方法200的描述是一般性的,更详细的处理可以从前面的描述中看出。

52.在框202,第一传感器层在基板的结晶表面上外延生长。例如,第一传感器层54(图1)或第三传感器层62(图2)在基板50的结晶表面52上外延生长。在一些实例中,第一传感器层可以形成为除了基板上外延生长的第一传感器层之外的基板的部分,或者形成为替代基板上外延生长的第一传感器层的基板的部分。

53.在框204,第一隔离结构在第一传感器层上外延生长。例如,第一隔离结构56(图1)或第二隔离结构60(图2)在第一传感器层(如分别为第一传感器层54或第三传感器层62)上外延生长。框204包括框206、208、210、212,其可以可选地被施行以形成第一隔离结构。在框206,量子阱层在第一传感器层上外延生长。例如,量子阱层可以是图3描述的量子阱层106或类似于关于图3描述的量子阱层106。在框208,结晶介电层在第一传感器层上外延生长。例如,结晶介电层可以是关于图4描述的结晶介电层108或类似于关于图4描述的结晶介电层108。在框210,外延生长第一半导体材料层,以及在框212,外延生长第二半导体材料。框210和212可以迭代地(iteratively)施行数次,例如,以形成超晶格结构,如布拉格光栅。例如,第一半导体材料和第二半导体材料可以分别是图5的第一层112和第二层114或类似于图5的第一层112和第二层114。

54.在框214,第二传感器层在第一隔离结构上外延生长。例如,第二传感器层58在第一隔离结构(如第一隔离结构56(图1)或第二隔离结构60(图2))上外延生长。在框216,第二隔离结构在第二传感器层上外延生长。例如,第二隔离结构60(图1)或第一隔离结构56(图2)在第二传感器层58上外延生长。框216包括框218、220、222、224,其可以可选地被施行以形成第二隔离结构。在框218,量子阱层在第二传感器层上外延生长。例如,量子阱层可以是图3描述的量子阱层106或类似于关于图3描述的量子阱层106。在框220,结晶介电层在第二传感器层上外延生长。例如,结晶介电层可以是关于图4描述的结晶介电层108或类似于关于图4描述的结晶介电层108。在框222,外延生长第一半导体材料层,以及在框224,外延生长第二半导体材料。框222和224可以迭代地施行数次,例如,以形成超晶格结构,如布拉格光栅。例如,第一半导体材料和第二半导体材料可以分别是图5的第一层112和第二层114或类似于图5的第一层112和第二层114。

55.在框216,第三传感器层在第二隔离结构上外延生长。例如,第三传感器层62(图1)或第一传感器层54(图2)在第二隔离结构(如分别为第二隔离结构60或第一隔离结构56)上外延生长。

56.图7至图12图标可以作为实例实施图6的方法200的各种流程图和所得到的结构。这些实例的描述是高度概括的,本领域技术人员将容易理解可以实现的更精确的处理和/或结构。

57.图7是根据一些实例形成包括堆叠像素结构的器件结构的方法300的流程图。图8是根据一些实例的根据图7的方法300形成的器件结构的横截面。将在图8的器件结构的上下文中描述图7的方法300。图8的器件结构被图标为背面照式(back side illuminated,bsi)器件,但器件结构可以被修改为正面照式(front side illuminated,fsi)器件。

58.参考图7的方法300,在框302,在基板的背面表面上外延生长电荷层。如图8所示,电荷层402在基板50的背面上外延生长。在一些实例中可以省略电荷层。可以为了提供蚀刻停止层、阻挡金属污染和扩散或其他目的而形成电荷层。

59.在框304,缓冲层在基板的正面(front side)表面上外延生长。如图8所示,缓冲层404外延生长在基板50的正面表面上。在一些实例中可以省略缓冲层。缓冲层可以改善堆叠像素结构外延生长所在其上的表面的质量。因此,缓冲层404形成结晶表面52,堆叠像素结构将在结晶表面52上外延生长。在省略缓冲层的实例中,基板50可以形成结晶表面52。

60.在方法200,形成堆叠像素结构,像关于图6所述。如图8所示,堆叠像素结构包括第一传感器层54、第一隔离结构56、第二传感器层58、第二隔离结构60和第三传感器层62。图8所示的堆叠像素结构处于相对于图1所示和描述的结晶表面52的定向上,其可以用于bsi器件。在其他实例中,堆叠像素结构可以处于相对于图2中所示和描述的结晶表面52的定向上,其可以用于fsi器件。

61.在框308,通过形成层间电介质(ild)和栅极堆叠来施行前段(front end of the line,feol)处理。作为实例,如图8所示,隔离区406形成在基板50的正面上,在该实例中,基板50在离结晶表面52最远的传感器层和隔离结构(例如,分别如图所示的第三传感器层62和第二隔离结构60)中并穿过离结晶表面52最远的传感器层和隔离结构(例如,分别如图所示的第三传感器层62和第二隔离结构60)。晶体管(如晶体管408)在由隔离区406所界定的有源区(active region)中形成。尽管在图8中未用附图标记标示,但掺杂阱(doped well)在离结晶表面52最远的传感器层(如第三传感器层62)中形成并延伸到离结晶表面52最远的隔离结构(如第二隔离结构60)。晶体管408包括掺杂阱区中的源极/漏极区以及设置在离结晶表面52最远的传感器层上且在源极/漏极区之间的栅极堆叠。栅极堆叠包括栅极电介质和栅电极,该栅极电介质设置在离结晶表面52最远的传感器层上,该栅电极在该栅极电介质上。沟道区被限定在离结晶表面52最远的传感器层中且在源极/漏极区之间的栅极电介质之下。一个或多个ild 412在晶体管408和离结晶表面52最远的传感器层上形成。穿过一个或多个ild 412到晶体管408的源极/漏极区形成接触件或插塞(plug)。

62.鉴于前面描述,本领域技术人员将容易地理解可以在feol处理中实施的具体工艺和材料。例如,晶体管可以是平面场效应晶体管(fet)和/或三维或鳍式fet。处理可以包括栅极优先处理和/或替换栅极处理。可以对处理和/或结构作各种其他修改。

63.在框310,形成穿过ild到堆叠像素结构的各个传感器层的通孔。如图8所示,通孔

414经形成到最靠近结晶表面52的传感器层(如第一传感器层54);通孔416经形成到中间传感器层(如第二传感器层58);以及通孔418经形成到离结晶表面52最远的传感器层(如第三传感器层62)。通孔418可使用各向异性(anisotropic)蚀刻工艺来形成,如深反应离子蚀刻(rie),以形成到适当传感器层的通孔凹槽。接着可以在通孔凹槽中如通过原子层沉积(ald)共形地(conformally)沉积钝化层以及对钝化层作各向异性蚀刻,使得钝化层保留在通孔凹槽的侧壁上,以及从通孔凹槽的底表面去除(如传感器层的暴露表面)。然后将导电材料(如金属)沉积在接触传感器层的暴露表面的通孔凹槽中以及侧壁上的钝化层上。可以如通过化学机械抛光(cmp)去除沉积在ild 412的顶表面上的任何导电材料。鉴于前面描述,本领域技术人员将容易地理解可以经实施以形成通孔的具体工艺和材料。

64.在框312,施行后段(back end of the line,beol)处理。如图8所示,beol处理在ild 412上形成互连结构420。互连结构可以包括金属间介电(imd)层,其中的金属层包括设置在其中的金属线和/或通孔。金属线和通孔可以以将通孔414、416、418连接到各种晶体管的方式连接。鉴于前述描述,本领域技术人员将容易理解可以经实施以形成互连结构并施行beol处理的具体工艺和材料。

65.在框314,对于bsi器件,施行基板的背面减薄(thinning)。对于fsi器件,可以省略框314。背面减薄可以通过cmp从基板背面施行。背面减薄可以去除在框302外延生长的电荷层(如在图8中图示为电荷层402)。

66.图9是根据一些实例形成包括堆叠像素结构的器件结构的方法500的流程图。图10是根据一些实例的根据图9的方法500形成的器件结构的横截面。将在图10的器件结构的上下文中描述图9的方法500。图10的器件结构被图标为bsi器件,尽管该器件结构可以修改为fsi器件。

67.参考图9的方法500,在框502,在基板的背面上外延生长电荷层(像图7的框302中)。如图10所示,电荷层602外延生长在基板50的背面上。在一些实例中可以省略电荷层。

68.在框504,在基板的正面表面上外延生长半导体层。如图10所示,半导体层603在基板50的正面表面上外延生长。在一些实例中可以省略半导体层。

69.在框506,针对堆叠像素结构在基板的正面中蚀刻沟槽。如图10所示,沟槽604被蚀刻穿过半导体层603(如果存在的话)并进入基板50,其中沟槽604由基板50所形成的侧壁和底表面限定。蚀刻工艺可以是任何各向异性蚀刻工艺,如rie。在框508,施行蚀刻后(post-etch)表面处置(treatment)和清洁。本领域技术人员将容易理解可以经施行以蚀刻、处置和清洁沟槽的各种工艺。沟槽604的底表面(如基板50的表面)形成结晶表面52。

70.在方法200,形成堆叠像素结构,像关于图6所述。如图10所示,堆叠像素结构包括第一传感器层54、第一隔离结构56、第二传感器层58、第二隔离结构60和第三传感器层62。图10所示的堆叠像素结构处于相对于图1所示和描述的结晶表面52的定向上,其可以用于bsi器件。在其他实例中,堆叠像素结构可以处于相对于图2中所示和描述的结晶表面52的定向上,其可以用于fsi器件。

71.在框512,通过形成ild和栅极堆叠来施行feol处理。图10绘示隔离区608、晶体管610和一个或多个ild 612作为一实例。此类部件和形成此类部件的工艺的描述可以类似于上文关于图8所描述的。

72.在框514,形成穿过ild到堆叠像素结构的各个传感器层的通孔。如图10所示,通孔

614经形成到最靠近结晶表面52的传感器层(如第一传感器层54);通孔616经形成到中间传感器层(如第二传感器层58);以及通孔618经形成到离结晶表面52最远的传感器层(如第三传感器层62)。通孔614、616、618和形成通孔614、616、618的工艺的描述可以与上面关于图8所描述的类似。

73.在框516,施行beol处理。如图10所示,beol处理在ild 612上形成互连结构620。互连结构620和形成互连结构620的工艺的描述可以与上面关于图8所描述的类似。

74.在框518,对于bsi器件,施行基板的背面减薄。对于fsi器件,可以省略框518。背面减薄可以通过cmp从基板背面施行。背面减薄可以去除在框502外延生长的电荷层(如在图10中图示为电荷层602)。

75.图11是根据一些实例的形成包括堆叠像素结构的器件结构的方法700的流程图。图12是根据一些实例根据图11的方法700形成的器件结构的横截面。将在图12的器件结构的上下文中描述图11的方法700。图12的器件结构被图标为bsi器件,尽管该器件结构可以修改为fsi器件。

76.参考图11的方法700,在框702,在基板的背面上外延生长电荷层(像图7的框302中)。电荷层在基板50的背面表面上外延生长,尽管在图12中未示出(由于随后将描述的原因)。在一些实例中可以省略电荷层。

77.在框704,在基板的正面表面上外延生长半导体层。如图12所示,半导体层804在基板50的正面表面上外延生长。在一些实例中可以省略半导体层。

78.在框706,通过形成ild和栅极堆叠来施行feol处理。图12绘示隔离区808、晶体管810和一个或多个ild 812作为一实例。此类部件和形成此类部件的工艺的描述可以类似于上文关于图8所描述的。

79.在框708,施行beol处理。如图12所示,beol处理在ild 812上形成正面互连结构820。正面互连结构820和形成正面互连结构820的工艺的描述可以与上面关于图8所描述的类似。

80.在框710,施行基板的背面减薄。背面减薄可以通过cmp从基板背面施行。背面减薄去除在框702外延生长的电荷层。

81.在框712,在用于堆叠像素结构的基板的背面中蚀刻沟槽。如图12所示,沟槽822被蚀刻到基板50中,其中沟槽822由基板50所形成的侧壁和底表面限定。蚀刻工艺可以是任何各向异性蚀刻工艺,如rie。在框714,施行蚀刻后表面处置和清洁。本领域技术人员将容易理解可以经施行以蚀刻、处置和清洁沟槽的各种工艺。沟槽822的底表面(如基板50的表面)形成结晶表面52。

82.在方法200,形成堆叠像素结构,像关于图6所述。如图12所示,堆叠像素结构包括第一传感器层54、第一隔离结构56、第二传感器层58、第二隔离结构60和第三传感器层62。图12所示的堆叠像素结构处于相对于图2所示和描述的结晶表面52的定向上,其可以用于bsi器件。在其他实例中,堆叠像素结构可以处于相对于图1中所示和描述的结晶表面52的定向上,其可以用于fsi器件。

83.在框718,通孔经形成到堆叠像素结构的各个传感器层,以穿过基板的通孔(tsv)经形成穿过基板到正面互连结构。如图12所示,通孔832经形成到离结晶表面52最远的传感器层(如第一传感器层54);通孔834经形成到中间传感器层(如第二传感器层58);以及通孔

836经形成到最靠近结晶表面52的传感器层(如第三传感器层62)。此外,tsv 842、844、846经形成穿过基板50到如基板50正面上的正面互连结构820中的金属线。介电层可以形成在基板50的背面及堆叠像素结构上,以及可以穿过介电层形成用于形成通孔832、834、836和tsv 842、844、846的凹槽。用于形成通孔832、834、836和tsv 842、844、846的工艺可以类似于以上关于图8的通孔414、416、418所描述的。

84.在框720,形成背面互连结构。背面互连结构包括其中设置有金属线和/或通孔的介电层。金属线和/或通孔将连接堆叠像素结构的传感器层的通孔电连接到tsv,tsv进一步电连接到正面互连结构中的金属线和/或通孔。如图12所示,形成背面互连结构850,其包括将通孔832电连接到tsv 842、将通孔834电连接到tsv 844以及将通孔836电连接到tsv 846的金属线和通孔。形成背面互连件的处理可以与上面针对beol处理所描述的类似。

85.图13是可用于施行外延生长的热处理腔室900的截面图。处理腔室900可以实施上述图6的方法200中不同层和材料的外延生长。例如,框202、204、214、216、226的外延生长可以在处理腔室900中顺序施行,例如,而无需从处理腔室900移除基板且/或无需破坏处理腔室的真空900。在一些实例中,处理腔室1012是可从加利福尼亚州圣克拉拉的应用材料公司取得的减压(rp)epi腔室。

86.处理腔室900包括腔室主体902、支撑系统904和控制器906。腔室主体902包括上部912和下部914。上部912包括在上圆顶916和基板901之间的腔室主体902内的区域。下部914包括在下圆顶930和基板901的底部之间的腔室主体902内的区域。沉积工艺通常发生在上部912内的基板901的上表面上。

87.支撑系统904包括用于执行和监控预定工艺的部件,如处理腔室900中的外延层或膜的生长。控制器906耦接到支持系统904并且适于控制处理腔室900和支持系统904。控制器906包括处理器(如中央处理单元(cpu))、存储器和支持电路。处理器可以是可在工业环境中使用的任何形式的通用处理器中的一种。存储器或非暂时性存储介质是可由处理器访问且可以是一个或多个存储器,如随机存取存储器(ram)、只读存储器(rom)、软盘、硬盘或任何其他的数字单元格式,本端的或是远程的。支持电路可以耦接至处理器且可包括高速缓存、时钟电路、输入/输出子系统、电源及类似物。这里公开的各种方法通常可在处理器的控制下通过处理器施行存储在存储器中的计算机指令代码(如作为软件常规程序)来实现。当计算机指令代码由处理器执行时,处理器控制处理腔室900施行根据各种方法和操作的工艺,如本案描述的图6的方法200。

88.处理腔室900包括多个热源(如灯935),多个热源适于向位于处理腔室900内的部件提供热能。例如,灯935可适于向基板901、基座926和/或预热环923提供热能。下圆顶930可由光学透明材料(如石英)形成,以利于热辐射通过。可以预期的是,灯935可经定位以提供通过上圆顶916以及下圆顶930的热能。

89.腔室主体902包括在其中形成的多个气室。气室与一个或多个气体源976(如载体气体)和一个或多个前驱物源978(如沉积气体和掺杂剂气体)流体连通。例如,第一气室920可适于提供通过其进入腔室主体902的上部912的沉积气体950,而第二气室924可适于从上部912排出沉积气体950。以此方式,沉积气体950可平行于基板901的上表面流动。

90.在使用液体前驱物的情况下,处理腔室900可以包括与液体前驱物源982流体连通的液体蒸发器980。液体蒸发器980用于蒸发待输送到处理腔室900的液体前驱物。虽然未示

出,但可以预期液体前驱物源982可包括例如一个或多个安瓿的前驱物液体和溶剂液体、关断阀和液体流量计(lfm)。

91.基板支撑组件932位于腔室主体902的下部914中。基板支撑组件932被图标为在处理位置中支撑基板901。基板支撑组件932包括由光学透明材料形成的基座支撑轴927和由基座支撑轴927支撑的基座926。基座支撑轴927的轴960定位在护罩931内,升举销接触件942耦接到护罩931。基座支撑轴927是可旋转的,以利于处理期间基板901的旋转。耦接到基座支撑轴927的致动器929促进基座支撑轴927的旋转。护罩931通常固定就位,因此在处理期间不旋转。支撑销937将基座支撑轴927耦接到基座926。

92.升举销933设置穿过在基座支撑轴927中形成的开口(未标记)。升举销933可垂直地致动且适于接触基板901的下侧以将基板901从处理位置(如图所示)升举至基板移除位置。

93.预热环923可拆卸地设置在耦接到腔室主体902的下衬垫940上。预热环923绕腔室主体902的内部空间设置且在基板901在处理位置时包围(circumscribe)基板901。当处理气体通过与预热环923相邻的第一气室920进入腔室主体902时,预热环923促进处理气体的预热。

94.上圆顶916的中央窗部分915和下圆顶930的底部分917可由光学透明材料(如石英)形成。上圆顶916的周边凸缘919与下圆顶930的周边凸缘921可全部由不透明的石英形成以保护靠近周边凸缘的o形环922免于直接暴露于热辐射,上圆顶916的周边凸缘919绕中央窗部分915的周缘接合中央窗部分915,下圆顶930的周边凸缘921绕底部分的周缘接合底部分。周边凸缘919可由光学透明材料(如石英)形成。

95.图14是处理系统1000的示意性俯视图,处理系统1000可以用于实施本文描述的框或方法的一个或多个操作,如图6、7、9和11的方法200、300、500、700的操作。在一些实例中,处理系统1000是可从加利福尼亚州圣克拉拉的应用材料公司取得的系统。

96.传送机器人1004设置在处理系统1000的传送腔室1002中。具有两个装载锁定腔室1006a、1006b的装载锁定1006与传送腔室1002耦接。多个处理腔室1008、1010、1012、1014、1016也耦接到传送腔室1002。处理腔室1008、1010、1012、1014、1016中的至少一个包括上文关于图4描述的处理腔室900,如用于实施图6的方法200。处理腔室1008、1010、1012、1014、1016中的其他处理腔室可以是任何合适的处理腔室,如用于清洁、蚀刻、沉积等,其可以实施如图7、9和11的方法300、500、700的其他操作。

97.在处理期间,待处理的基板可在舱(pod,未图标)中到达处理系统1000。基板由工厂接口机器人(未图标)从舱传送到真空兼容的装载锁定腔室1006a、1006b。接着基板由传送腔室1002中的传送机器人1004搬运(handle),传送腔室1002通常保持在真空状态。传送机器人1004然后将基板装载到处理腔室1008、1010、1012、1014、1016中的任一个中。传送机器人1004经配置从处理腔室1008、1010、1012、1014、1016中的任一个中拾取基板并将基板装载到处理腔室1008、1010、1012、1014、1016中的另一个中。传送机器人1004经配置在不同的处理腔室之间传送基板,以针对不同的处理腔室对基板施行不同的处理。随着基板被传送到各种处理腔室,由处理腔室1008、1010、1012、1014、1016施行的处理以及处理腔室1008、1010、1012、1014、1016之间的基板传送可以允许基板不暴露于大气(如没有破坏真空),这减少了污染的机会并改善处理结果的质量。

98.传送腔室1002在处理期间可保持在真空和/或低于大气压的压力下。传送腔室1002的真空度可被调整以匹配相应处理腔室的真空程度。例如,当将基板从传送腔室1002传送到处理腔室中(或反之亦然)时,传送腔室1002和处理腔室可保持在相同的真空程度。然后,当将基板从传送腔室传送到装载锁定腔室或批次装载锁定腔室(或反之亦然)时,传送腔室真空程度可匹配装载锁定腔室1006a、1006b的真空水平,即便装载锁定腔室和处理腔室的真空程度可能不同。

99.虽然前面所述涉及本公开内容的各种实例,但在不背离本公开内容的基本范围下,可设计本公开内容的其他与进一步的实施方式,且本公开内容的范围由随附权利要求所确定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1