一种基于玻璃衬底的芯片封装工艺及多器件集成玻璃芯片的制作方法

1.本发明涉及芯片封装工艺技术领域,更具体地说,涉及一种基于玻璃衬底的芯片封装工艺及多器件集成玻璃芯片。

背景技术:

2.随着集成电路芯片行业的迅速发展,现可以实现多器件有效集成在单一芯片上,从而也会导致芯片上的结构以及电路设计会非常复杂,相应的也会使芯片的尺寸变大,以及功耗的增加。

3.如说明书附图1所示,为目前芯片行业较普遍的铜走线结构,在芯片器件上方直接做铜走线后封装、进行走线与i/o连接;其结构尺寸和体积相对较大。

4.如说明书附图2所示,为目前部分多集成芯片上硅衬底的tsv(through silicon via,硅通孔)工艺结构,首先通过对硅片的背面减薄,然后进行rie(reactive ion etching,反应离子刻蚀)刻蚀开孔镀铜、焊接,完成芯片封装;其可以有效减少芯片的尺寸与体积。

5.目前,单器件芯片已经不能满足现今的芯片市场需求,多器件集成芯片已渐渐出现在人们的视野当中,所以针对玻璃衬底芯片来设计3d/tgv(through glass via,玻璃通孔)结构来提高多器件集成玻璃芯片的市场竞争力、增强产品电气性能、减小芯片体积尺寸以及符合玻璃衬底产品的性能需求,是目前需要研发的方向。

6.前面的叙述在于提供一般的背景信息,并不一定构成现有技术。

技术实现要素:

7.本发明的目的在于提供一种基于玻璃衬底的芯片封装工艺及多器件集成玻璃芯片,该基于玻璃衬底的芯片封装工艺,实现器件堆叠减少集成芯片尺寸以及体积,缩短铜走线,降低功耗,提高电气性能。

8.本发明提供一种基于玻璃衬底的芯片封装工艺,包括以下步骤:

9.s1:玻璃正面涂抗hf的腐蚀的胶膜,并进入s2步骤;

10.s2:玻璃衬底经背面研磨减薄,并进入s3步骤;

11.s3:通过化学机械抛光,并进入s4步骤;

12.s4:玻璃衬底背面经一定比例的hf酸和氨水的混合溶液做同性刻蚀,形成碗状的凹槽,并进入s5步骤;

13.s5:再用离子束蚀刻垂直导通形成深槽,刻穿玻璃衬底,并进入s6步骤;

14.s6:蒸镀tin/cu种子层,并进入s7步骤;

15.s7:通过带胶电镀形成细长的凸起,并进入s8步骤;

16.s8:再次通过回流焊接工艺,形成球状,并进入s9步骤;

17.s9:通过划片道切割,并进入s10步骤;

18.s10:将单个单元的裸片与pcb高温焊接贴合。

19.进一步地,所述s5步骤中细长的凸起用于裸片与pcb连接引线。

20.进一步地,所述s6步骤中通过回流焊接工艺形成球状用于增强引线接触。

21.本发明还提供一种多器件集成玻璃芯片,通过上述的基于玻璃衬底的芯片封装工艺对所述多器件集成玻璃芯片进行加工。

22.进一步地,所述多器件集成玻璃芯片包括钝化层、器件工作区、玻璃衬底、电路板及铜线;所述钝化层的一面和所述玻璃衬底连接,所述玻璃衬底另一面和所述电路板连接;在所述玻璃衬底上设有多个器件工作区,所述钝化层覆盖在所述器件工作区上,所述玻璃衬底上设有两个玻璃通孔,所述铜线上连接有多个器件,所述铜线的两端分别穿过所述玻璃通孔和所述电路板电性连接。

23.进一步地,所述玻璃衬底在和所述电路板连接的一面为光滑平面。

24.进一步地,所述玻璃通孔呈圆柱形。

25.进一步地,在所述铜线的端部设有细长凸起,所述细长凸起用于将单个单元的裸片与所述电路板连接。

26.进一步地,所述细长凸起上设有回流焊接球,所述回流焊接球用于增强所述细长凸起和所述电路板之间的连接强度。

27.本发明提供的基于玻璃衬底的芯片封装工艺,实现器件堆叠减少集成芯片尺寸以及体积,缩短铜走线,降低功耗,提高电气性能。

附图说明

28.图1为目前芯片行业较普遍的铜走线结构示意图。

29.图2为目前部分多集成芯片上硅衬底的tsv工艺结构示意图。

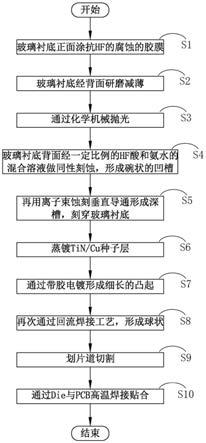

30.图3为本发明实施例提供的基于玻璃衬底的芯片封装工艺的流程图。

31.图4为本发明实施例提供的多器件集成玻璃芯片的结构示意图。

32.图5为图4中多器件集成玻璃芯片的另一结构示意图。

33.附图中涉及的附图标记和组成部分如下所示:

34.1、钝化层

35.2、器件工作区

36.3、玻璃衬底

37.4、电路板

38.5、铜线

39.6、玻璃通孔

40.7、细长凸起

41.8、回流焊接球

42.9、硅衬底

43.10、植球

44.11、通孔

具体实施方式

45.下面结合附图和实施例,对本发明的具体实施方式作进一步详细描述。以下实施

例用于说明本发明,但不用来限制本发明的范围。

46.本发明的说明书和权利要求书中的术语“第一”、“第二”、“第三”、“第四”等是用于区别类似的对象,而不必用于描述特定的顺序或先后次序。

47.实施例1

48.图3为本发明实施例提供的基于玻璃衬底的芯片封装工艺的流程图。请参照图3,本发明实施例提供的基于玻璃衬底的芯片封装工艺,包括以下步骤:

49.s1:玻璃正面涂抗hf的腐蚀的胶膜,用来防止后续的hf混合溶液腐蚀芯片表面,并进入s2步骤;

50.s2:玻璃衬底经背面研磨减薄,并进入s3步骤;

51.需要说明的是,该tgv工艺是在wafer前端制程完成后再在背部打孔的工艺,其类似tsv。

52.s3:通过化学机械抛光,并进入s4步骤;

53.s4:玻璃衬底背面经一定比例的hf酸和氨水的混合溶液做同性刻蚀,形成碗状的凹槽,并进入s5步骤;

54.s5:再用离子束蚀刻垂直导通形成深槽,刻穿玻璃衬底,并进入s6步骤;

55.需要说明的是,s4、s5步骤中所用到溶液浓度实际比例以玻璃的材质决定。

56.s6:蒸镀tin/cu种子层,并进入s7步骤;

57.s7:通过带胶电镀形成细长的凸起,用于裸片与pcb连接引线,并进入s8步骤;

58.s8:再次通过回流焊接工艺,形成球状,用于增强引线接触,并进入s9步骤;

59.s9:通过划片道切割,并进入s10步骤;

60.s10:将单个单元的裸片与pcb高温焊接贴合。

61.需要说明的是,本发明提供的基于玻璃衬底的芯片封装工艺,基于硅衬底的tsv(through silicon via)原理对玻璃衬底3背面开孔的技术,其3d/tgv的原理是在玻璃芯片的背面做铜走线的连接以及芯片与pcb板的焊接。从而实现器件堆叠减少集成芯片尺寸以及体积,缩短铜走线,降低功耗,提高电气性能。

62.图4为本发明实施例提供的多器件集成玻璃芯片的结构示意图,图5为图4中多器件集成玻璃芯片的另一结构示意图。请参照图3、图4,本发明还提供一种多器件集成玻璃芯片,通过上述的基于玻璃衬底的芯片封装工艺对多器件集成玻璃芯片进行加工。

63.本发明的多器件集成玻璃芯片包括钝化层1、器件工作区2、玻璃衬底3、电路板4及铜线5;钝化层1的一面和玻璃衬底3连接,玻璃衬底3另一面和电路板4连接;在玻璃衬底3上设有多个器件工作区2,钝化层1覆盖在器件工作区2上,玻璃衬底3上设有两个玻璃通孔6,铜线5上连接有多个器件,铜线5的两端分别穿过玻璃通孔6和电路板4电性连接。

64.本发明提供的玻璃衬底3在和电路板4连接的一面为光滑平面;玻璃通孔6呈圆柱形,从而可以缩短铜走线从而降低功耗并提高电气性能;在铜线5的端部设有细长凸起7,细长凸起7用于将单个单元的裸片与电路板4连接;细长凸起7上设有回流焊接球8,回流焊接球8用于增强细长凸起7和电路板4之间的连接强度。

65.基于上文的描述可知,本发明优点在于:

66.1、本发明提供的基于玻璃衬底的芯片封装工艺,基于硅衬底的tsv(through silicon via)原理对玻璃衬底3背面开孔的技术,其3d/tgv的原理是在玻璃芯片的背面做

铜走线的连接以及芯片与pcb板的焊接;从而实现器件堆叠减少集成芯片尺寸以及体积,缩短铜走线,降低功耗,提高电气性能。

67.2、本发明提供的多器件集成玻璃芯片,该产品结构已经在投入生产实验中,通过tgv流程和常规via流程对比,tgv流程所制造出来的芯片电气性能更优,可靠性更好。

68.以上所述,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应以所述权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1