半导体装置的制作方法

半导体装置

1.[相关申请的引用]

[0002]

本技术享有2021年9月14日提出申请的日本专利申请号2021-149156的优先权的权益,所述日本专利申请的全部内容被引用到本技术中。

技术领域

[0003]

本实施方式涉及一种半导体装置。

背景技术:

[0004]

半导体装置中,有时会将多个芯片积层,使端子从各芯片沿着积层方向延伸而构成。半导体装置中,期望除了多个芯片以外,还能适当地配置其它芯片。

技术实现要素:

[0005]

一实施方式提供一种能够适当地配置多个第1芯片及第2芯片的半导体装置。

[0006]

实施方式的半导体装置提供一种具有支撑体、多个第1芯片、第1密封部、第2芯片、多个第1端子及第2端子的半导体装置。多个第1芯片积层在支撑体上。第1密封部将多个第1芯片密封。第1密封部在与支撑体为相反侧的表面具有凹部。凹部包含与多个第1芯片分离的底面。第2芯片配置在凹部中。多个第1端子对应于多个第1芯片。多个第1端子分别从第1芯片的与支撑体为相反侧的面沿着积层方向延伸并贯通第1密封部。第2端子配置在第2芯片的与支撑体为相反侧的面上。

[0007]

根据所述构成,可提供一种能够适当地配置多个第1芯片及第2芯片的半导体装置。

附图说明

[0008]

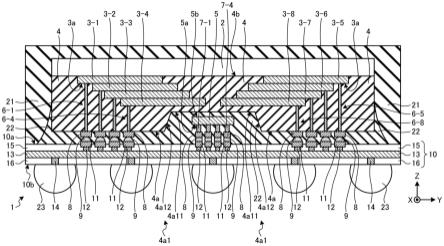

图1是表示第1实施方式的半导体装置的构成的剖视图。

[0009]

图2a~图2d是表示第1实施方式的半导体装置的制造方法的剖视图。

[0010]

图3是表示第1实施方式的半导体装置的制造方法的俯视图。

[0011]

图4a~图4c是表示第1实施方式的半导体装置的制造方法的剖视图。

[0012]

图5a~图5c是表示第1实施方式的半导体装置的制造方法的剖视图。

[0013]

图6a~图6c是表示第1实施方式的第1变化例的半导体装置的制造方法的剖视图。

[0014]

图7是表示第1实施方式的第2变化例的半导体装置的制造方法的俯视图。

[0015]

图8是表示第1实施方式的第3变化例的半导体装置的制造方法的俯视图。

[0016]

图9是表示第1实施方式的第4变化例的半导体装置的制造方法的俯视图。

[0017]

图10是表示第2实施方式的半导体装置的构成的剖视图。

[0018]

图11a及图11b是表示第2实施方式的半导体装置的制造方法的剖视图。

[0019]

图12a~图12c是表示第2实施方式的半导体装置的制造方法的剖视图。

[0020]

图13a~图13c是表示第2实施方式的半导体装置的制造方法的剖视图。

[0021]

图14是表示第3实施方式的半导体装置的构成的剖视图。

具体实施方式

[0022]

以下,参照附图,对实施方式的半导体装置详细地进行说明。此外,本发明并不受这些实施方式限定。

[0023]

(第1实施方式)

[0024]

第1实施方式的半导体装置是将多个芯片积层,使端子(纵交线(vertical wire))从各芯片沿着积层方向延伸而构成。半导体装置1例如按图1所示的方式构成。

[0025]

图1是表示半导体装置1的构成的剖视图。以下,将与支撑体2的主面垂直的方向设为z方向,将在与z方向垂直的面内相互正交的2个方向设为x方向及y方向。

[0026]

半导体装置1具有支撑体2、多个芯片3-1~3-8、密封部4、芯片5、多个端子6-1~6-8、多个端子7-1~7-4、密封部22、外部电极23、衬底10及密封部21。

[0027]

支撑体2是在xy方向上延伸的板状部件。支撑体2在沿着xy平面观察时具有矩形。支撑体2具有适于支撑多个芯片3-1~3-8的刚性。支撑体2可由适于具有规定刚性的材料(例如,玻璃、玻璃布、硅)等形成。

[0028]

多个芯片3-1~3-8配置在支撑体2的-z侧,分成相等的两部分呈阶梯状积层。多个芯片3-1~3-4在多个芯片3-5~3-8的-y侧呈阶梯状积层。多个芯片3-5~3-8在多个芯片3-5~3-8的+y侧呈阶梯状积层。各芯片3-1~3-8的功能与芯片5不同,例如是能够存储数据的存储器芯片。

[0029]

密封部4将多个芯片3-1~3-8密封。密封部4可由模具树脂等具有热塑性的第1绝缘物形成。密封部4具有正面4a及背面4b。背面4b与支撑体2相接。正面4a是与支撑体2为相反侧的主面。密封部4在正面4a具有凹部4a1。凹部4a1是密封部4中从正面4a向+z侧凹陷的空间。凹部4a1只要能收容芯片5,则可采用任意形状。凹部4a1配置在能收容芯片5的位置,也可以配置在例如沿着xy平面观察时正面4a的中央附近(参照图3)。

[0030]

凹部4a1的深度比芯片3-4、3-8相对于正面4a的z方向深度小。背面4b的z位置比芯片3-4、3-8的表面(-z侧的面)的z位置更靠-z侧。

[0031]

凹部4a1具有底面4a11及侧面4a12。底面4a11沿着xy方向延伸。底面4a11与多个芯片3-1~3-8在z方向上分离。底面4a11与多个芯片3-1~3-4中最靠-z侧的芯片3-4在z方向上分离,与多个芯片3-5~3-8中最靠-z侧的芯片3-8在z方向上分离。底面4a11可以与芯片3-4的正面3a大致平行,也可以与芯片3-8的正面3a大致平行。凹部4a1可以是例如大致长方体形状的孔,也可以在沿着xy平面观察时具有大致矩形。凹部4a1的开放端的面积大于底面4a11的面积。凹部4a1的开放端的x方向宽度大于底面4a11的x方向宽度。凹部4a1的开放端的y方向宽度大于底面4a11的y方向宽度。

[0032]

凹部4a1的开放端的面积大于芯片5的面积。凹部4a1的开放端的x方向宽度大于芯片5的x方向宽度。凹部4a1的开放端的y方向宽度大于芯片5的y方向宽度。

[0033]

底面4a11的面积大于芯片5的面积。底面4a11的x方向宽度大于芯片5的x方向宽度。底面4a11的y方向宽度大于芯片5的y方向宽度。

[0034]

多个端子6-1~6-8对应于多个芯片3-1~3-8。各端子6-1~6-8从对应的芯片3中与支撑体2为相反侧的面(-z侧的面)3a沿着-z方向延伸,贯通密封部4而到达正面4a。各端

子6-1~6-8也可以多个连接于对应的芯片3。各端子6-1~6-8也可以沿着-z方向直线延伸。各端子6-1~6-8也可以是直立型端子,具有能够维持直线形状的刚性。

[0035]

例如,各端子6-1~6-8的直径可以比用于打线接合型安装的金属线的直径粗。各端子6-1~6-8是垂直延伸的金属线,也被称为纵交线。通过将各端子6-1~6-8以直立型构成,可容易实现各端子6-1~6-8间的配置间距的窄间距化。

[0036]

在将多个芯片3-1~3-8分成两半部分呈阶梯状积层的情况下,多个端子6-1~6-8也可以分成两半部分使长度呈阶梯状不同。多个端子6-1~6-4的+z侧端部的z位置在多个端子6-5~6-8的-y侧呈阶梯状变低。多个端子6-5~6-8的+z侧端部的z位置在多个端子6-5~6-8的+y侧呈阶梯状变低。多个端子6-1~6-8的-z侧端部的z位置也可以相互均等。各端子6-1~6-8的-z侧端部经由电极8及焊球凸块(ball bump)9而连接于衬底10的电极图案11。各端子6-1~6-8可由以金属(例如金)为主成分的导电物形成。

[0037]

芯片5配置在支撑体2的-z侧,且配置在多个芯片3-1~3-8的-z侧。芯片5的功能与芯片3不同,例如是能够控制多个芯片3-1~3-8的控制器芯片。芯片5电连接于多个芯片3-1~3-8。芯片5理想的是配置在半导体装置1中沿着xy平面观察时的中央附近,以此使得朝向各芯片3-1~3-8的配线长度一样长。因此,芯片5配置在凹部4a1内。

[0038]

芯片5的背面(+z侧的面)5b也可以与凹部4a1的底面4a11在-z方向上稍微分离。这样一来,芯片5与多个芯片3-1~3-8中最靠-z侧的芯片3-4、3-8在-z方向上分离。

[0039]

多个端子7-1~7-4配置在芯片5的正面(-z侧的面)5a。各端子7-1~7-4也可以沿着-z方向呈柱状延伸。各端子7-1~7-4的xy方向上的最大宽度比各端子6-1~6-8的xy方向上的最大宽度大。各端子7-1~7-4可由多个层的积层而形成。多个层可分别由焊料合金层、铜合金层等以合金为主成分的导电物形成。多个层可以包含组成互不相同的层,也可以是不同组成的层与相同组成的层混合存在。

[0040]

多个端子7-1~7-4的+z侧端部与芯片5的正面5a耦合。多个端子7-1~7-4的-z侧端部的z位置也可以相互均等。多个端子7-1~7-4的-z侧端部距离支撑体2的z方向高度可与多个端子6-1~6-8的-z侧端部距离支撑体2的z方向高度均等。各端子7-1~7-4的-z侧端部经由电极8及焊球凸块9而连接于衬底10的电极图案11。各端子7-1~7-4是柱状凸块,也被称为柱形凸块。通过将各端子7-1~7-4以柱状构成,可容易实现各端子7-1~7-4间的配置间距的窄间距化。

[0041]

密封部22填埋凹部4a1,且将芯片5密封。密封部22填埋密封部4与衬底10的间隙,并将电极8、焊球凸块9及电极图案11密封。密封部22覆盖密封部4的-z侧的面,并且覆盖衬底10的正面10a。密封部22可由模具树脂等具有热塑性的第2绝缘物形成。第2绝缘物的组成与第1绝缘物不同。

[0042]

密封部21从外侧覆盖支撑体2、密封部4、密封部22并进行密封。密封部21可到达衬底10的正面10a。密封部21可由模具树脂等具有热塑性的第3绝缘物形成。第3绝缘物的组成与第1绝缘物不同,与第2绝缘物也不同。

[0043]

密封部4、密封部21、密封部22也可以是在绝缘性树脂中包含无机物填料所得者。这时,密封部4、密封部21的填料的含量可以比密封部22的填料的含量多。

[0044]

密封部4、密封部21的热膨胀率可分别小于密封部22的热膨胀率。

[0045]

密封部4、密封部21的杨氏模数可分别大于密封部22的杨氏模数。

[0046]

衬底10具有多个电极图案11、多个通孔电极12、导电层13、多个通孔电极14、预浸体层15及核心层16。多个电极图案11分别露出在衬底10的正面10a,多个通孔电极14分别露出在衬底10的背面10b。各电极图案11、各通孔电极12、导电层13、各通孔电极14可分别由以导电物(例如铜)为主成分的材料形成。预浸体层15、核心层16可分别由以绝缘物(例如塑料等有机系物质)为主成分的材料形成。

[0047]

此外,图1中,为了简化表示,示出了导电层13连接于多个电极图案11、多个通孔电极12、多个通孔电极14的形态,但实际上可形成规定的配线,选择性地连接规定的电极图案11、规定的通孔电极12、规定的通孔电极14。

[0048]

多个外部电极23配置在衬底10的背面10b,且分别与通孔电极14接合。多个外部电极23的x方向的配置间距大于多个端子6-1~6-8的x方向的配置间距。多个外部电极23的x方向的配置间距大于多个端子7-1~7-4的x方向的配置间距。同样,多个外部电极23的y方向的配置间距大于多个端子6-1~6-8的y方向的配置间距。多个外部电极23的y方向的配置间距大于多个端子7-1~7-4的y方向的配置间距。由此,能够实现各端子6-1~6-8间的配置间距、各端子7-1~7-4间的配置间距的窄间距化,同时容易将半导体装置1连接于宽间距的外部端子(例如母板上的端子)。

[0049]

接下来,使用图1~图5c对半导体装置1的制造方法进行说明。图1是表示半导体装置1的构成的剖视图,但也用作表示半导体装置1的制造方法的剖视图。图2a~图2d、图4a~图4c、图5a~图5c是表示半导体装置1的制造方法的剖视图。图3是表示半导体装置1的制造方法的俯视图。

[0050]

图2a所示的步骤中,准备支撑体2。支撑体2是沿着xy方向延伸的板状部件。支撑体2可由适于具有规定刚性的材料(例如,玻璃、玻璃布、硅)等形成。多个芯片3-1~3-8呈阶梯状积层在支撑体2的-z侧的面2a。

[0051]

例如,在支撑体2的-z侧的面2a中的-y侧区域,可经由粘接剂或粘接膜等粘接芯片3-1。芯片3-2可以xy平面位置例如向+y侧偏移的状态粘接在芯片3-1的-z侧。芯片3-3可以xy平面位置例如向+y侧偏移的状态经由粘接剂或粘接膜等粘接在芯片3-2的-z侧。芯片3-4可以xy平面位置例如向+y侧偏移的状态粘接在芯片3-3的-z侧。

[0052]

由此,在支撑体2的面2a的-y侧区域,多个芯片3-1~3-4以y位置向+y侧依次偏移的方式呈阶梯状积层。各芯片3-1~3-4以正面3a为-z侧的状态面朝上安装。多个芯片3-1~3-4的正面3a距离支撑体2的z方向高度依次变高。同样,在支撑体2的面2a的+y侧区域,多个芯片3-5~3-8以y位置向-y侧依次偏移的方式呈阶梯状积层。各芯片3-5~3-8以正面3a为-z侧的状态面朝上安装。多个芯片3-5~3-8的正面3a距离支撑体2的z方向高度依次变高。

[0053]

图2b所示的步骤中,多个端子6-1~6-8与多个芯片3-1~3-8耦合。多个端子6-1~6-8对应于多个芯片3-1~3-8。多个端子6-1~6-8的长度对应于多个芯片3-1~3-8距离支撑体2的z方向高度(例如,用来吸收z方向高度的差异),可互不相同。各端子6-1~6-8在竖立在z方向的姿势下,其+z侧的端部可与所对应的芯片3的正面3a上的电极垫耦合。此外,也可以从各芯片3延伸出多个端子6(参照图3)。

[0054]

例如,对应于多个芯片3-1~3-4的正面3a距离支撑体2的z方向高度依次变高,多个端子6-1~6-4的长度会依次变短。由此,多个端子6-1~6-4在已与多个芯片3-1~3-4耦合的状态下,其-z侧端部的z位置相互靠近。同样,对应于多个芯片3-5~3-8的正面3a距离

支撑体2的z方向高度依次变高,多个端子6-5~6-8的长度会依次变短。由此,多个端子6-5~6-8在已与多个芯片3-5~3-8耦合的状态下,其-z侧端部的z位置相互靠近。

[0055]

图2c所示的步骤中,在支撑体2的-z侧形成密封部4i。也就是说,利用第1绝缘物覆盖多个芯片3-1~3-8的正面及侧面,并且利用第1绝缘物覆盖多个端子6-1~6-8的侧面及端面,以此形成密封部4i。密封部4i可由模具树脂等具有热塑性的第1绝缘物形成。密封部4i距离支撑体2的z方向高度比最靠-z侧的芯片3-4、3-8的z方向高度高,且比各端子6-1~6-8的z方向高度高。

[0056]

图2d所示的步骤中,在密封部4i的-z侧的正面4ai形成凹部4a1i。凹部4a1i的形成深度与规定深度和后续步骤的研磨厚度的合计相对应。规定深度形成为小于芯片3-4、3-8相对于正面4ai的z方向深度。规定深度也可以是后续步骤中将芯片5安装在衬底10的状态下的芯片5距离衬底10的z方向高度以上。凹部4a1i也可以形成为在分别沿着xz截面观察及沿着yz截面观察时呈锥形,即,以越靠近底面4a11开口宽度越小的方式使侧面4a12倾斜。例如,凹部4a1i可由模具成形而形成。准备模具,所述模具包含有在xy方向中央附近具有基座部的平坦部,使第1绝缘物加热熔融后流入模具中,冷却后进行脱模,由此可形成在表面的xy方向中央附近具有凹部4a1i的密封部4i。这时,通过使基座部为锥形,可容易进行脱模,能够提高形成密封部4i的处理的处理量。或者,凹部4a1i也可以通过激光加工来形成。在形成具有平坦表面的密封部4i之后,一边通过nc(numerical control,数字控制)控制等在其表面将照射位置控制为矩形,一边对所述表面照射激光,由此可形成在表面的中央附近具有凹部4a1i的密封部4i。这时,从激光加工的特性来看,凹部4a1i可形成为锥形。

[0057]

如图3所示,凹部4a1i在沿着xy平面观察时形成在正面4ai的中央附近。图3中,例示了凹部4a1i形成为大致长方体形状的孔(沿着xy平面观察时为大致矩形)的构成。凹部4a1i以其x方向宽度大于芯片5的x方向宽度的方式形成。凹部4a1i以其y方向宽度大于芯片5的y方向宽度的方式形成。通过将凹部4a1i以这样的方式构成,能够在后续步骤中将芯片5收容在凹部4a1i内。

[0058]

图4a所示的步骤中,对密封部4i的正面4ai进行研磨。例如,将研磨装置的研磨机抵接于密封部4i的正面4ai,研磨机以与接触面垂直的轴为中心旋转,使研磨机连续旋转,直到各端子6-1~6-8的-z侧端部露出在密封部4的正面4a为止。密封部4的z方向厚度相比密封部4i薄了相当于研磨厚度的量。凹部4a1的深度相比凹部4a1i减小了相当于研磨厚度的量。

[0059]

图4b所示的步骤中,在密封部4的正面4a形成多个电极8。多个电极8对应于多个端子6-1~6-8。各电极8连接于所对应的端子6的-z侧的端部。各电极8由金属(例如铜)等导电物形成。由此,可获得多个芯片3-1~3-8呈阶梯状积层且面朝上安装并被密封的上部构造体20。

[0060]

图4c所示的步骤中,准备衬底10。露出在衬底10的正面10a的多个电极图案11分别与焊球凸块9耦合。沿着xy平面观察时的衬底10的中央附近的多个焊球凸块9分别与电极8耦合。

[0061]

另一方面,准备芯片5。在芯片5的正面5a配置多个电极垫。准备与多个电极垫对应的多个端子7-1~7-4。多个端子7-1~7-4各自的一端与芯片5的正面5a上的对应的电极垫耦合。另外,多个端子7-1~7-4与沿着xy平面观察时的衬底10的中央附近的多个电极8相对

应。多个端子7-1~7-4各自的另一端与电极8耦合。也就是说,芯片5以正面5a为-z侧的状态面朝下安装于衬底10。由此,获得芯片5面朝下安装于衬底10的下部构造体30。

[0062]

以正面4a与正面10a相对的方式使上部构造体20与下部构造体30对向配置。从z方向透视时,以上部构造体20中的电极8与下部构造体30中的焊球凸块9重叠的方式,进行上部构造体20与下部构造体30的相对位置对准。这时,从z方向透视时,芯片5包含在凹部4a1的内侧(参照图3)。

[0063]

图5a所示的步骤中,上部构造体20及下部构造体30在z方向上相对靠近。上部构造体20中的电极8与下部构造体30中的焊球凸块9相互耦合。芯片5被收容在密封部4的凹部4a1内。

[0064]

图5b所示的步骤中,上部构造体20与下部构造体30的间隙被密封部22密封。密封部22以填满凹部4a1并且填满密封部4及衬底10的间隙的方式填充。密封部22可由模具树脂等具有热塑性的第2绝缘物形成。由此,芯片5被密封部22密封,并且电极8、焊球凸块9被密封部22密封。

[0065]

图5c所示的步骤中,上部构造体20的外侧被密封部21密封。密封部21形成为从外侧覆盖支撑体2、密封部4、密封部22。密封部21也可以形成为到达衬底10的正面10a。密封部21可由模具树脂等具有热塑性的第3绝缘物形成。第3绝缘物的组成与第1绝缘物不同,与第2绝缘物也不同。

[0066]

图1所示的步骤中,在衬底10的背面10b安装多个外部电极23。可对露出在衬底10的背面10b的通孔电极14接合外部电极23。然后,通过切削进行单片化,从而获得半导体装置1。

[0067]

如上所述,在第1实施方式中,在半导体装置1中,在将积层的多个芯片3-1~3-8密封的密封部4的正面4a的沿着xy平面观察时的中央附近设置凹部4a1。在凹部4a1内收容芯片5。由此,容易将芯片5相对于多个芯片3-1~3-8以大致等距离配线,从而能够提供一种具有适于将多个芯片3-1~3-8及芯片5分别适当配置的构造的半导体装置1。

[0068]

此处,当制造半导体装置1时,考虑将多个芯片3-1~3-8呈阶梯状积层在支撑体2上,在最上方(最靠-z侧)的芯片3-4、3-8上粘接芯片5的情况。这种情况下,可能会因粘接时的应力等而导致芯片3-4、3-8弯曲,使得芯片5从恰当的平面方向倾斜。

[0069]

对此,在第1实施方式中,在半导体装置1中,收容芯片5的凹部4a1的底面4a11与被密封部4密封的多个芯片3-1~3-8中的最上方(最靠-z侧)的芯片3-4、3-8的正面3a在z方向上分离。由此,能够提供一种具有适于将芯片5在不会从恰当的平面方向倾斜的情况下安装而制造的构造的半导体装置1。

[0070]

此处,当制造半导体装置1时,考虑利用密封部4一并密封连接于芯片3-1~3-8的直立型端子6-1~6-8与安装于芯片5的柱状端子7-1~7-4。这种情况下,在端子6-1~6-8与端子7-1~7-4之间,前端的高度存在差异。为了吸收这种差异,将端子6-1~6-8及端子7-1~7-4形成得较高,然后通过研磨使高度一致。也就是说,因增高了具有比端子6-1~6-8复杂的构造(多个膜的积层构造)的端子7-1~7-4,有可能会导致半导体装置1的成本增加。

[0071]

对此,在第1实施方式中,在半导体装置1中,直立型端子6-1~6-8与作为连接目标的芯片3-1~3-8均被密封部4密封,其-z侧端部露出在密封部4的正面4a。柱状端子7-1~7-4安装在密封部4的凹部4a1内所收容的芯片5上。由此,能够抑制密封部4的密封对端子6-1

~6-8及端子7-1~7-4间的不均的影响,从而能够将端子7-1~7-4抑制得较低。也就是说,能够提供一种适于降低制造成本的半导体装置1。

[0072]

此外,如图6c所示,也可以在芯片5与凹部4a1的底面4a11之间介置缓冲部件40。图6a~图6c分别是表示第1实施方式的第1变化例的半导体装置的制造方法的剖视图。

[0073]

例如,在半导体装置1的制造方法中,也可以在进行图2a~图2d所示的步骤之后,进行图6a所示的步骤。在图6a所示的步骤中,在凹部4a1的底面4a11配置缓冲部件40。缓冲部件40是在xy方向上延伸的板状部件。缓冲部件40也可以由树脂系粘着剂等具有柔软性、弹性的绝缘材料形成。缓冲部件40以覆盖底面4a11的主要部分的方式配置。

[0074]

如图3中两点链线所示,缓冲部件40以沿着xy平面观察时包含在底面4a11的内侧并且内侧包含芯片5的方式配置。缓冲部件40的xy面积小于底面4a11的xy面积,大于芯片5的xy面积。缓冲部件40的x方向宽度小于底面4a11的x方向宽度,大于芯片5的x方向宽度。缓冲部件40的y方向宽度小于底面4a11的y方向宽度,大于芯片5的y方向宽度。

[0075]

在进行图4a~图4c所示的步骤之后,代替图5a所示的步骤,而进行图6b所示的步骤。在图6b所示的步骤中,上部构造体20及下部构造体30在z方向上相对靠近。与第1实施方式相同的是,上部构造体20中的电极8与下部构造体30中的焊球凸块9相互耦合。芯片5的背面与缓冲部件40接触,并且芯片5被收容在密封部4的凹部4a1内。这时,芯片5稍微压抵于缓冲部件40,但由于缓冲部件40具有弹性,所以能抑制对芯片5的应力。

[0076]

代替图5b所示的步骤而进行图6c所示的步骤。在图6c所示的步骤中,当利用密封部22将上部构造体20与下部构造体30的间隙密封时,覆盖缓冲部件40及芯片5的露出面并且填满凹部4a1。这时,凹部4a1的底面4a11的主要部分被缓冲部件40覆盖,因此,能够抑制密封部22中产生空隙,提高安装品质。

[0077]

然后,进行图5c所示的步骤、图1所示的步骤,以与第1实施方式相同的方式来制造半导体装置1。

[0078]

这样一来,在第1实施方式的第1变化例的半导体装置中,在芯片5与凹部4a1的底面4a11之间介置缓冲部件40。由此,能够提供具有适于提高安装品质的构造的半导体装置1。

[0079]

另外,凹部4a1i只要能够收容芯片5,则可以是任意形状,例如也可以形成为图7所示的横i字状的沟槽(沿着xy平面观察时为大致横i字状)。图7是表示第1实施方式的第2变化例的半导体装置1的制造方法的俯视图。图7中,例示了凹部4a1i形成为横i字状的沟槽的构成。这种情况下,与第1实施方式不同的是,凹部4a1的开放端的y方向宽度与底面4a11的y方向宽度均等。此外,与第1实施方式相同的是,凹部4a1i的开放端的面积大于底面4a11的面积,凹部4a1i的开放端的x方向宽度大于底面4a11的x方向宽度。

[0080]

端子6-1~6-8露出在凹部4a1i的底面。端子露出面的高度较低。因此,也可以另外形成电极来补足端子的高度。或者,也可以将电极8或焊球凸块9形成得较高。

[0081]

凹部4a1i也可以形成为在沿着xz截面观察时呈锥形,即,以越接近底面4a11开口宽度越小的方式使侧面4a12倾斜。例如,凹部4a1i也可以利用切割加工来形成。在形成具有平坦表面的密封部4i之后,一边通过nc控制等在其表面上控制接触位置一边使切割刀在x方向上接触所述表面并旋转,由此,可形成在表面的x方向中央附近具有槽状凹部4a1i的密封部4i。这时,从切割加工的特性来看,凹部4a1i可以形成为在沿着xz截面观察时呈锥形。

或者,凹部4a1i也可以通过模具成形而形成。准备模具,所述模具包含有在x方向中央附近具有横i字状基座部的平坦部,使第1绝缘物加热熔融后流入模具,冷却后进行脱模,由此,可形成在表面的x方向中央附近具有凹部4a1i的密封部4i。这时,通过使基座部为锥形,可容易进行脱模,从而可提高形成密封部4i的处理的处理量。或者,凹部4a1i也可以利用激光加工而形成。在形成具有平坦表面的密封部4i之后,一边通过nc控制等在其表面将照射位置控制为横条纹状,一边对所述表面照射激光,由此,可形成在表面的x方向中央附近具有凹部4a1i的密封部4i。这时,从激光加工的特性来看,凹部4a1i可形成为锥形。

[0082]

另外,凹部4a1i例如也可以形成为图8所示的纵i字状的沟槽(沿着xy平面观察时为大致纵i字状)。图8是表示第1实施方式的第3变化例的半导体装置1的制造方法的俯视图。图8中,例示了凹部4a1i形成为纵i字状的沟槽的构成。这种情况下,与第1实施方式不同的是,凹部4a1的开放端的x方向宽度与底面4a11的x方向宽度均等。此外,与第1实施方式相同的是,凹部4a1i的开放端的面积大于底面4a11的面积,凹部4a1i的开放端的y方向宽度大于底面4a11的y方向宽度。

[0083]

凹部4a1i也可以形成为在沿着yz截面观察时呈锥形,即,以越接近底面4a11开口宽度越小的方式使侧面4a12倾斜。例如,凹部4a1i也可以利用切割加工而形成。在形成具有平坦表面的密封部4i之后,一边通过nc控制等在其表面控制接触位置,一边使切割刀在y方向上接触所述表面并旋转,由此,可形成在表面的y方向中央附近具有槽状凹部4a1i的密封部4i。这时,从切割加工的特性来看,凹部4a1i可以形成为在沿着yz截面观察时呈锥形。或者,凹部4a1i也可以通过模具成形而形成。准备模具,所述模具包含有在y方向中央附近具有纵i字状基座部的平坦部,使第1绝缘物加热熔融后流入模具,冷却后进行脱模,由此,可形成在表面的y方向中央附近具有凹部4a1i的密封部4i。这时,通过使基座部为锥形,可容易进行脱模,从而可提高形成密封部4i的处理的处理量。或者,凹部4a1i也可以利用激光加工而形成。在形成具有平坦表面的密封部4i之后,一边通过nc控制等在其表面将照射位置控制为纵条纹状,一边照射激光,由此,可形成在表面的y方向中央附近具有凹部4a1i的密封部4i。这时,从激光加工的特性来看,凹部4a1i可形成为锥形。

[0084]

另外,凹部4a1i例如也可以形成为图9所示的十字状的沟槽(沿着xy平面观察时为大致十字状)。图9是表示第1实施方式的第4变化例的半导体装置1的制造方法的俯视图。图9中,例示了凹部4a1i形成为十字状沟槽的构成。这种情况下,与第1实施方式不同的是,凹部4a1的开放端的x方向宽度在y方向中央附近与底面4a11的x方向宽度均等,在y方向两端附近大于底面4a11的x方向宽度,凹部4a1的开放端的y方向宽度在x方向中央附近与底面4a11的y方向宽度均等,在x方向两端附近大于底面4a11的y方向宽度。此外,与第1实施方式相同的是,凹部4a1i的开放端的面积大于底面4a11的面积。

[0085]

端子6-1~6-8露出在凹部4a1i的底面。端子露出面的高度较低。因此,也可以另外形成电极以补足端子的高度。或者,也可以将电极8或焊球凸块9形成得较高。

[0086]

凹部4a1i的x方向两端附近的部分也可以形成为在沿着yz截面观察时呈锥形,即,以越接近底面4a11开口宽度越小的方式使侧面4a12倾斜。凹部4a1i的y方向两端附近的部分也可以形成为在沿着xz截面观察时呈锥形,即,以越接近底面4a11开口宽度越小的方式使侧面4a12倾斜。例如,凹部4a1i也可以利用切割加工来形成。在形成具有平坦表面的密封部4i之后,一边通过nc控制等在其表面控制接触位置,一边使切割刀在x方向上接触所述表

面并旋转,并且使切割刀在y方向上接触所述表面并旋转,由此,可形成表面具有交叉槽状的凹部4a1i的密封部4i。这时,从切割加工的特性来看,凹部4a1i的x方向两端附近的部分可形成为在沿着yz截面观察时呈锥形,且y方向两端附近的部分形成为在沿着xz截面观察时呈锥形。或者,凹部4a1i也可以通过模具成形而形成。准备模具,所述模具包含具有十字状基座部的平坦部,使第1绝缘物加热熔融后流入模具,冷却后进行脱模,由此,可形成表面具有十字状凹部4a1i的密封部4i。这时,通过使基座部为锥形,可容易进行脱模,从而可提高形成密封部4i的处理的处理量。或者,凹部4a1i也可以利用激光加工而形成。在形成具有平坦表面的密封部4i之后,一边通过nc控制等在其表面将照射位置控制为十字状,一边对所述表面照射激光,由此,可形成表面具有十字状凹部4a1i的密封部4i。这时,从激光加工的特性来看,凹部4a1i的x方向两端附近的部分可形成为在沿着yz截面观察时呈锥形,y方向两端附近的部分形成为在沿着xz截面观察时呈锥形。

[0087]

(第2实施方式)

[0088]

接下来,对第2实施方式的半导体装置进行说明。以下,以与第1实施方式不同的部分为中心进行说明。

[0089]

在第1实施方式中,例示了包含芯片5的背面与凹部4a1的底面4a11分离的构造的半导体装置1,但在第2实施方式中,例示包含芯片5的背面与凹部4a1的底面4a11接触的构造的半导体装置101。

[0090]

具体来说,如图10所示,半导体装置101中,芯片5的背面5b与凹部4a1的底面4a11接触。图10是表示第2实施方式的半导体装置101的构成的剖视图。与第1实施方式相比,芯片5与多个芯片3-1~3-8中最上方的芯片3-4、3-8的z方向距离变得更小,因此,能够实现半导体装置101的低背化。

[0091]

此外,在芯片5与芯片3-4、3-8之间介置着密封部4。由此,与第1实施方式相同的是,能够将芯片5在沿着xy平面观察时沿着xy方向安装在密封部4的中央附近。

[0092]

半导体装置101具有多个端子107-1~107-4、密封部122来代替多个端子7-1~7-4、密封部22(参照图1),还具有密封部123。多个端子107-1~107-4的-z侧端部的z位置与多个端子6-1~6-8的-z侧端部的z位置大致相同。密封部123填埋凹部4a1并且密封芯片5。密封部123的-z侧的面123a与密封部4的-z侧的面4a形成连续面,且z位置大致相同。密封部123可由模具树脂等具有热塑性的第4绝缘物形成。第4绝缘物的组成与第1绝缘物不同。第4绝缘物的组成可以与第2绝缘物不同,也可以与第3绝缘物不同。

[0093]

密封部122及密封部123也可以是在绝缘性树脂中包含无机物填料所得者。这时,密封部4、密封部21、密封部122的填料的含量可以多于密封部123的填料的含量。密封部4、密封部21的填料的含量也可以多于密封部122的填料的含量。

[0094]

密封部4、密封部21、密封部122的热膨胀率可以小于密封部123的热膨胀率。密封部4、密封部21的热膨胀率也可以小于密封部122的热膨胀率。

[0095]

密封部4、密封部21、密封部122的杨氏模数可以大于密封部123的杨氏模数。密封部4、密封部21的杨氏模数也可以大于密封部122的杨氏模数。

[0096]

此外,与第1实施方式相同的是,各端子6-1~6-8的-z侧端部经由电极8及焊球凸块9而连接于衬底10的电极图案11,各端子7-1~7-4的-z侧端部经由电极8及焊球凸块9而连接于衬底10的电极图案11。

[0097]

另外,如图11a~图13c所示,半导体装置101的制造方法在以下方面与第1实施方式不同。图11a~图11b、图12a~图12c、图13a~图13c是表示半导体装置101的制造方法的剖视图。

[0098]

例如,在半导体装置101的制造方法中,也可以在进行图2a~图2d所示的步骤之后,进行图11a所示的步骤。在图11a所示的步骤中,准备芯片5及多个端子107-1~107-4。多个端子107-1~107-4各自的一端与芯片5的表面上所对应的电极垫耦合。在凹部4a1的底面4a11配置与多个端子107-1~107-4耦合的芯片5。如图3中单点链线所示,芯片5以沿着xy平面观察时包含在底面4a11的内侧的方式配置。芯片5也可以是其背面5b经由粘接剂或粘接膜等而粘接于底面4a11。

[0099]

这时,在凹部4a1内配置有芯片5的状态下,各端子6-1~6-8的-z侧端部的z位置与各端子107-1~107-8的-z侧端部的z位置可以在能够通过研磨而对齐的范围内互不相同。

[0100]

在图11b所示的步骤中,在凹部4ai内填充第4绝缘物质。也就是说,利用第4绝缘物覆盖芯片5的表面及侧面,并且利用第4绝缘物覆盖多个端子107-1~107-8的侧面及端面,以此形成密封部123i。由此,形成填满凹部4ai的密封部123i。第4绝缘物质的组成与第1绝缘物不同。第4绝缘物的组成可以与第2绝缘物不同,也可以与第3绝缘物不同。

[0101]

这时,密封部4的正面4ai的z位置与密封部123的正面123ai的z位置也可以在能够通过研磨而对齐的范围内互不相同。

[0102]

在图12a所示的步骤中,对密封部4i的正面4ai及密封部123i的正面123ai进行研磨。例如,研磨装置的研磨机抵接于密封部4i的正面4ai及密封部123i的正面123ai,研磨机以与接触面垂直的轴为中心旋转,使研磨机连续旋转,直到各端子6-1~6-8的-z侧端部露出在密封部4的正面4a并且各端子107-1~107-8的-z侧端部露出在密封部123的正面123为止。凹部4a1的深度相比凹部4a1i(参照图2d)减小了相当于研磨厚度的量。密封部4的z方向厚度相比密封部4i薄了相当于研磨厚度的量。凹部4a1的深度相比凹部4a1i减小了相当于研磨厚度的量。密封部123的z方向厚度相比密封部123i薄了相当于研磨厚度的量。

[0103]

这时,各端子6-1~6-8的-z侧端部的z位置与各端子107-1~107-8的-z侧端部的z位置大致相同。

[0104]

在图12b所示的步骤中,在密封部4的正面4a形成多个电极8,在密封部123的正面123a形成多个电极8。形成在密封部4的正面4a的多个电极8与第1实施方式相同。形成在密封部123的正面123a的多个电极8对应于多个端子107-1~107-4。形成在正面123a的各电极8电连接于所对应的端子107的-z侧的端部。由此,可获得多个芯片3-1~3-8呈阶梯状积层且面朝上安装并被密封、同时芯片5以能够面朝下安装的状态被密封的上部构造体120。

[0105]

在图12c所示的步骤中,准备衬底10。露出在衬底10的正面10a的多个电极图案11分别与焊球凸块9耦合。可获得构成为芯片5能够面朝下安装的状态的下部构造体130。

[0106]

以正面4a、123a与正面10a相对的方式将上部构造体120与下部构造体130对向配置。从z方向透视时,以上部构造体120中的电极8与下部构造体130中的焊球凸块9重叠的方式,进行上部构造体120与下部构造体130的相对位置对准。

[0107]

在图13a所示的步骤中,上部构造体120与下部构造体130在z方向上相对接近。上部构造体120中的电极8与下部构造体130中的焊球凸块9相互耦合。

[0108]

在图13b所示的步骤中,利用密封部122将上部构造体120与下部构造体130的间隙

密封。密封部122以填埋密封部4、123及衬底10的间隙的方式填充。密封部122可由模具树脂等具有热塑性的第2绝缘物形成。由此,电极8、焊球凸块9被密封部122密封。

[0109]

在图13c所示的步骤中,上部构造体120的外侧被密封部21密封。密封部21形成为从外侧覆盖支撑体2、密封部4、密封部122。密封部21也可以形成为到达衬底10的正面10a。密封部21可由模具树脂等具有热塑性的第3绝缘物形成。第3绝缘物的组成与第1绝缘物不同,与第2绝缘物也不同。

[0110]

在图10所示的步骤中,在衬底10的背面10b安装多个外部电极23。外部电极23可与露出在衬底10的背面10b的通孔电极14接合。然后,通过切削进行单片化,获得半导体装置101。

[0111]

如上所述,在第2实施方式中,在半导体装置101中,在将积层的多个芯片3-1~3-8密封的密封部4的正面4a的沿着xy平面观察时的中央附近设置凹部4a1。在凹部4a1内收容芯片5。由此,容易将芯片5相对于多个芯片3-1~3-8以大致等距离配线,因此,能够提供一种具有适于将多个芯片3-1~3-8及芯片5分别恰当地配置的构造的半导体装置101。

[0112]

(第3实施方式)

[0113]

接下来,对第3实施方式的半导体装置进行说明。以下,以与第1实施方式及第2实施方式不同的部分为中心进行说明。

[0114]

在第2实施方式中,例示了包含将端子6-1~6-8、107-1~107-4经由衬底10连接于外部电极23的构造的半导体装置101,但在第3实施方式中,例示包含将端子6-1~6-8、107-1~107-4经由再配线层240连接于外部电极23的构造的半导体装置201。

[0115]

具体来说,如图14所示,半导体装置201省略了电极8、焊球凸块9、密封部21(参照图10),且配置再配线层240以代替衬底10。图14是表示第3实施方式的半导体装置201的构成的剖视图。与第2实施方式相比,端子6-1~6-8、107-1~107-4与外部电极23的z方向距离变得更小,并且z高度降低了相当于密封部21的厚度的量,因此,可实现半导体装置201的更低背化。

[0116]

此外,在芯片5与芯片3-4、3-8之间介置着密封部4。由此,与第1实施方式及第2实施方式相同的是,能够将芯片5在沿着xy平面观察时沿着xy方向安装在密封部4的中央附近。

[0117]

在半导体装置201中,再配线层240包含用来将端子6-1~6-8、107-1~107-4与外部电极23连接的多层配线。再配线层240例如包含3层配线层,且包含配线层241、插塞层242、配线层243、插塞层244、配线层245、层间绝缘膜246。

[0118]

多个端子6-1~6-8的-z侧端部分别连接于配线层241中的电极图案。多个端子107-1~107-4的-z侧端部分别连接于配线层241中的电极图案。

[0119]

多个外部电极23分别连接于配线层245中的电极图案。

[0120]

配线层241中的电极图案与配线层245中的电极图案可经由插塞层242中的插塞、配线层243中的线图案、插塞层244中的插塞等而连接。由此,端子6-1~6-8、107-1~107-4经由再配线层240而连接于外部电极23。

[0121]

另外,如图14所示,半导体装置201的制造方法在以下方面与第2实施方式不同。图14是表示半导体装置201的构成的剖视图,但也可以用作表示半导体装置201的制造方法的剖视图。

[0122]

例如,在半导体装置201的制造方法中,也可以在以与第2实施方式相同的方式进行到图12a所示的步骤之后,进行图14所示的步骤。在图14所示的步骤中,通过蒸镀法或溅镀法等,在密封体4的正面4a及密封部123的正面123a堆积导电层241i。在所述导电层241i上,形成选择性地覆盖多个端子6-1~6-8的-z侧端部与多个端子107-1~107-4的-z侧端部的抗蚀图案rp1。将抗蚀图案rp1作为掩模对导电层241i进行蚀刻加工。由此,形成包含选择性地覆盖多个端子6-1~6-8的-z侧端部与多个端子107-1~107-4的-z侧端部的电极图案的配线层241。

[0123]

接着,堆积覆盖配线层241的绝缘膜246i。在所述绝缘膜246i上,形成在配线层241中的电极图案的位置具有开口的抗蚀图案rp2。将抗蚀图案rp2作为掩模对绝缘膜246i进行蚀刻加工。形成选择性地使配线层241中的电极图案露出的孔。在孔中埋入钨等导电物质。由此,形成与配线层241中的电极图案连接的插塞层242的插塞。

[0124]

以相同的方式形成配线层243、插塞层244、配线层245。

[0125]

然后,在再配线层240的-z侧的面安装多个外部电极23。外部电极23与配线层245中的电极图案耦合。然后,通过切削进行单片化,获得半导体装置201。

[0126]

如上所述,在第3实施方式中,在半导体装置201中,在将积层的多个芯片3-1~3-8密封的密封部4的正面4a的沿着xy平面观察时的中央附近设置凹部4a1。在凹部4a1内收容芯片5。由此,容易将芯片5相对于多个芯片3-1~3-8以大致等距离配线,因此,能够提供一种具有适于将多个芯片3-1~3-8及芯片5分别恰当地配置的构造的半导体装置201。

[0127]

(其它实施方式)

[0128]

(a)在第1实施方式及第2实施方式中,也可以设置密封部4来代替密封部22及密封部122。例如,在图5b中,不设置密封部22,而利用密封部4直接进行密封。在第2实施方式中,同样地,可以删除图13b中设置密封部122的步骤。由此,能够降低制造成本。这时,在密封部4与衬底10之间设置密封部21。

[0129]

(b)在第1实施方式中,芯片5以面朝下状态通过倒装芯片接合将芯片5的端子连接于设置在衬底10的端子。这时,芯片5的电路面朝向衬底10侧而形成。也可以取而代之,将芯片5的端子通过打线接合而连接于设置在衬底10的端子。这时,芯片5的电路面形成为与衬底10为相反方向侧的面。通过利用打线接合进行连接,能够以低成本形成。

[0130]

对本发明的几个实施方式进行了说明,但这些实施方式是作为示例提出的,并不意图限定发明的范围。这些新颖的实施方式能够以其它各种形态加以实施,且能够在不脱离发明的主旨的范围内进行各种省略、替换、变更。这些实施方式及其变化包含在发明的范围或主旨中,并且包含在权利要求书所记载的发明及其均等的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1