一种槽型分裂栅集成沟道二极管的MOSFET器件

一种槽型分裂栅集成沟道二极管的mosfet器件

技术领域

1.本发明属于mosfet器件技术领域,涉及一种槽型分裂栅集成沟道二极管的mosfet器件。

背景技术:

2.功率半导体器件承担着开关、驱动以及整流器的作用,功率mosfet具有开关转换频率高,输入阻抗大,热稳定性好等优良特性,而节能先进的功率mosfet逐渐成为我国信息产业和效能经济的重要基石。功率mosfet的应用在日常生活、各个行业非常广泛,有现代电子芯片的地方就有功率mosfet,它是电子芯片安全高效且精确处理信息的重要一环。随着半导体行业在技术和工艺上的不断优化,不仅要求功率器件的静态特性优良,同样也要求其动态特性更好,故而对开关速度和开关损耗有了更高的要求。在传统mosfet器件上,通过结构改进,已经设计出silicon-gate metal oxide semiconductor field effect transistor(分裂栅金属氧化物半导体器件,简称sg-mos器件)、mostet with built-in channel diode(集成沟道二极管金属氧化物半导体器件,bd-mos器件),这些器件的开关性能均有不同程度的改善。

3.mosfet器件的开关速度与栅漏电容c

gd

与栅漏电荷q

gd

有关,c

gd

越低,q

gd

越少时,器件的开关速度就会提升;而器件在反向恢复过程中,反向恢复电流i

rr

的峰值大小、反向恢复时间t

rr

的长短以及反向恢复电荷q

rr

都会影响到器件的开关性能。

4.因此,需要通过改善以上几个关键指标来设计新的mosfet器件。

技术实现要素:

5.有鉴于此,本发明的目的在于提供一种槽型分裂栅集成沟道二极管的mosfet器件。

6.为达到上述目的,本发明提供如下技术方案:

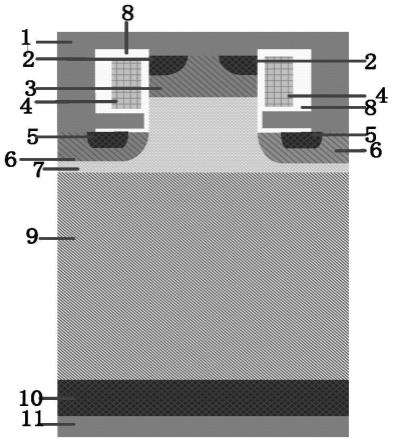

7.1.一种槽型分裂栅集成沟道二极管的mosfet器件,所述mosfet器件为左右对称结构,所述mosfet器件从下到上依次包括漏极11、漏极n+区10、n-drift区9、jfet区7、源极p-base区3和源极1;

8.所述mosfet器件两侧分别设置有沟道二极管p-base 6,所述沟道二极管p-base 6的上表面一侧与源极1相连、另一侧与氧化层8相连,其余部分与jfet区7相连;

9.所述沟道二极管p-base 6中设置有沟道二极管n+区5,所述沟道二极管n+区5的上表面的一侧与源极1相连,另一侧与氧化层8相连,沟道二极管包含沟道二极管n+区5和沟道二极管p-base 6;

10.所述源极p-base区3的两侧分别设置有氧化层8,所述氧化层8的其余部分与源极1相连,所述氧化层8中设置有栅极4,所述栅极4为分裂栅;

11.所述源极p-base区3的两端分别设置有两个不相连的源极n+区2,所述源极n+区2的上表面与源极1相连,一侧与氧化层8相连。

12.优选的,所述源极p-base区3的上表面与源极1相接触,下表面与jfet区7相接触;

13.所述源极p-base区3为一个整体部分或两个并不相连的独立部分。

14.优选的,所述jeft区7中掺杂的是浓度为1

×

10

16

cm-3

的n型杂质。

15.优选的,所述n-drift区9的长度为9μm,所述n-drift区9掺杂的是浓度为9

×

10

14

cm-3

的n型杂质。

16.优选的,所述源极n+区2的顶端到沟道二极管p-base 6的顶端的垂直高度为0.8μm。

17.优选的,所述源极p-base区3的底端到沟道二极管p-base 6的顶端的垂直高度为0.3μm。

18.优选的,所述mosfet器件的宽度为7.6μm。

19.本发明的有益效果在于:

20.本发明公开了一种槽型分裂栅集成沟道二极管的mosfet器件,在传统的mosfet器件结构上,通过器件在栅极下表面引入分裂栅和沟道二极管(包含沟道二极管n+区5和沟道二极管p-base 6),其中,分裂栅屏蔽了栅极与漏极的耦合面积,从而大幅降低了器件的反馈电容和栅极电荷,最终提高器件的开关速度;与此同时,由于沟道mos二极管的存在,在反向恢复时,沟道mos二极管抑制了寄生pn结二极管的开启,大幅降低了寄生pn结二极管空穴的注入效率,从而降低了反向恢复电荷、反向峰值电流和反向恢复时间,最终改善了器件的反向恢复性能。因此,本发明的槽型分裂栅集成沟道二极管的mosfet器件对于传统的mosfet器件在开关性能和反向恢复性能方面进行了改善。

21.本发明的其他优点、目标和特征在某种程度上将在随后的说明书中进行阐述,并且在某种程度上,基于对下文的考察研究对本领域技术人员而言将是显而易见的,或者可以从本发明的实践中得到教导。本发明的目标和其他优点可以通过下面的说明书来实现和获得。

附图说明

22.为了使本发明的目的、技术方案和优点更加清楚,下面将结合附图对本发明作优选的详细描述,其中:

23.图1为实施例1中槽型分裂栅集成沟道二极管的mosfet器件的结构图;

24.图2为实施例1中的mosfet器件和传统的con-mos器件、sg-mos器件、bd-mos器件的耐压变化情况的关系对比图;

25.图3为实施例1中的mosfet器件和传统的con-mos器件、sg-mos器件、bd-mos器件的导通电阻的对比关系图;

26.图4为实施例1中的mosfet器件和传统的con-mos器件、sg-mos器件、bd-mos器件的反向恢复电流的变化关系对比图;

27.图5为实施例1中的mosfet器件和传统的con-mos器件、sg-mos器件、bd-mos器件反向恢复过程中的空穴浓度的变化对比图;

28.图6为实施例1中的mosfet器件和传统的con-mos器件、sg-mos器件、bd-mos器件的反馈电容的变化对比图;

29.图7为实施例1中的mosfet器件和传统的con-mos器件、sg-mos器件、bd-mos器件的

栅电荷随栅源电压的变化关系对比图;

30.图8为实施例1中的mosfet器件与传统的con-mos器件、sg-mos器件、bd-mos器件的反向恢复电荷量变化的对比分析图;

31.图9为实施例1中的mosfet器件的制备工艺流程示意图;

32.其中1为源极、2为源极n+区、3为源极p-base区、4为栅极、5为沟道二极管n+区、6为沟道二极管p-base、7为jfet区、8为氧化层、9为n-drift区、10为漏极n+区、11为漏极。

具体实施方式

33.以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。需要说明的是,以下实施例中所提供的图示仅以示意方式说明本发明的基本构想,在不冲突的情况下,以下实施例及实施例中的特征可以相互组合。

34.实施例1

35.一种槽型分裂栅集成沟道二极管的mosfet器件,具体结构如图1所示,该槽型分裂栅集成沟道二极管的mosfet器件为左右对称结构,mosfet器件从下到上依次包括漏极11、漏极n+区10、n-drift区9、jfet区7、源极p-base区3(所述源极p-base区3为一个整体部分,上端与源极1相接触,下端与jfet区7相接触)和源极1;mosfet器件两侧分别设置有沟道二极管p-base 6,所述沟道二极管p-base 6的上端与源极1相连,其余部分与jfet区7相连;所述沟道二极管p-base 6中设置有沟道二极管n+区5(沟道二极管n+区5和沟道二极管p-base 6统称沟道二极管),所述沟道二极管n+区5的上表面的一侧与源极1相连,另一侧与氧化层8相连;所述源极p-base区3的两侧分别设置有氧化层8,所述氧化层8的其余部分与源极1相连,所述氧化层8中设置有分裂栅的栅极4;所述源极p-base区3的两端分别设置有两个不相连的源极n+区2,所述源极n+区2的上表面与源极1相连,一侧与氧化层8相连。

36.上述mosfet器件的宽度为7.6μm,其含有的jfet区7为n型杂质,其浓度为1

×

10

16

cm-3

;n-drift区9长度为9μm,掺杂的是n型杂质,其浓度为9

×

10

14

cm-3

。源极n+区2的顶端到沟道二极管p-base 6的顶端的长度为0.8μm;源极p-base区3的底端到沟道二极管p-base 6的顶端的长度为0.3μm。

37.性能测试

38.图2为实施例1中的mosfet器件和传统的con-mos器件、sg-mos器件、bd-mos器件的耐压变化情况的关系对比图。从图2中可以看出,相同条件下,sg-mos器件会比其他三种器件提前击穿,击穿电压为193v,而实施例1中的mosfet器件与传统mos器件(con-mos器件、sg-mos器件、bd-mos器件)的曲线基本相合,说明实施例1中的mosfet器件在优化传统器件结构之后,依然能够达到传统器件的耐压水平,击穿电压为225v,不会提前击穿。

39.图3为实施例1中的mosfet器件和传统的con-mos器件、sg-mos器件、bd-mos器件的导通电阻的对比关系图。从图3中可以看出,传统的con-mos器件和sg-mos器件的导通电阻分别为2.65mω

·

cm2和2.73mω

·

cm2,实施例1中的mosfet器件的导通电阻相较于它们高一些,为2.80mω

·

cm2;bd-mos器件的导通电阻为2.91mω

·

cm2,实施例1中的mosfet器件的导

通电阻相较其略低一点。

40.图4为实施例1中的mosfet器件和传统的con-mos器件、sg-mos器件、bd-mos器件的反向恢复电流的变化关系对比图。从图4可以看出,传统的con-mos器件、sg-mos器件的二极管开启电压大致在0.65v左右,bd-mos器件的二极管开启电压在0.5v左右,相对于传统结构,实施例1中的mosfet器件的二极管的开启电压更小,在0.45v左右,降低了30%。另一方面,传统的con-mos器件、sg-mos器件的导通电压在0.8v左右,bd-mos器件的导通电压在0.77v左右,而实施例1中的mosfet器件的导通电压相比更小一点,在0.76v左右,降低了5%。

41.图5为实施例1中的mosfet器件和传统的con-mos器件、sg-mos器件、bd-mos器件反向恢复过程中的空穴浓度的变化对比图。从图5可以看出,随着深度的增加,con-mos器件、bd-mos器件的空穴浓度从1.2

×

10

16

cm-3

增加到2.5

×

10

16

cm-3

左右,bd-mos器件的空穴浓度则从0.3

×

10

16

cm-3

增加到1.5

×

10

16

cm-3

左右,而实施例1中的mosfet器件的空穴浓度在器件结构的纵向分布上明显低于传统的三个器件,从0增加到1.0

×

10

16

cm-3

左右,相对于前三种器件分别降低了60%和33.3%,从而使得器件空穴电流减小。

42.图6为实施例1中的mosfet器件和传统的con-mos器件、sg-mos器件、bd-mos器件的反馈电容的变化对比图。从图6可以看出,随着漏源电压v

ds

的增加,实施例1中的mosfet器件的反馈电容曲线明显低于其他三种结构,这是因为器件在栅极下表面引入分裂栅和沟道mos二极管,分裂栅屏蔽了栅极与漏极的耦合面积,从而大幅降低了器件的反馈电容,传统con-mos器件、sg-mos器件、bd-mos器件的反馈电容分别为217pf/cm2、88pf/cm2、11pf/cm2,而实施例1中的mosfet器件的反馈电容只有1.1pf/cm2,相较于前面三种器件,分别降低了99%、98%、90%,从这些数值可以直观看出,在相同漏源电压v

ds

下,实施例1中的mosfet器件反馈电容最小,效果最好。

43.图7为实施例1中的mosfet器件和传统的con-mos器件、sg-mos器件、bd-mos器件的栅电荷随栅源电压的变化关系对比图。从图7中可以看出,由于实施例1中的mosfet器件引入分裂栅和沟道mos二极管来屏蔽栅漏的耦合面积,所以其栅极电荷大幅降低。从图7中可以直观看到,传统的con-mos器件、sg-mos器件、bd-mos器件的栅漏电荷分别为154nc/cm2、82nc/cm2、19nc/cm2,而实施例1中的mosfet器件的栅电荷平台区很窄,几乎没有,表明新结构的储存的栅漏电荷q

gd

极少,只有6nc/cm2左右,相对于前三种器件分别降低了96%、92%、68%。在达到相同的栅源电压v

gs

=10v左右时,con-mos器件、sg-mos器件、bd-mos器件的栅电荷分别为340nc/cm2、196nc/cm2、85nc/cm2,而实施例1中的mosfet器件所储存的栅电荷量较少,为93nc/cm2,只比传统bd-mos器件多8%,而相较于con-mos器件、sg-mos器件分别减少了72%、53%,因此最终提高了器件的开关速度。

44.图8为实施例1中的mosfet器件与传统的con-mos器件、sg-mos器件、bd-mos器件的反向恢复电荷量变化的对比分析图。如图8所示,在实施例1中的mosfet器件中,由于沟道mos二极管的存在,在反向恢复过程中,沟道mos二极管抑制了寄生pn结二极管的开启,大幅降低了寄生pn结二极管空穴的注入效率,从而降低了反向恢复电荷、反向峰值电流和反向恢复时间,最终改善了器件的反向恢复性能。从图8中可以看出,传统的con-mos器件、sg-mos器件和bd-mos器件的反向恢复时间分别为70ns、69ns、62ns,而实施例1中的mosfet器件的反向恢复时间明显缩短,为44ns;传统的con-mos器件、sg-mos器件和bd-mos器件的反向

恢复电流峰值分别为186a/cm2、172a/cm2、150a/cm2,而实施例1中的mosfet器件的反向恢复电流峰值大幅减小,为84a/cm2;传统的con-mos器件、sg-mos器件和bd-mos器件的反向恢复电荷分别为6.45μc/cm2、6.34μc/cm2、5.23μc/cm2,实施例1中的mosfet器件的反向恢复电荷q

rr

也明显减小,为2.56μc/cm2,相较前三种传统器件,分别减少了60%、59%、51%。

45.表1为实施例1中的mosfet器件和传统的con-mos器件、sg-mos器件、bd-mos器件的各种相关参数的对比情况。从表1中的对比可知,实施例1中的mosfet器件在较高耐压的情况下,拥有较低的栅电荷、栅漏电荷以及极低的反馈电容,并且在反向恢复过程中,反向恢复电荷、方向恢复电流以及反向恢复时间都降低,因此,相比于传统的con-mos器件、sg-mos器件、bd-mos器件,实施例1中的mosfet器件的各方面性能、参数更好,改善了器件的开关性能和反向恢复性能。

46.表1不同器件各种相关参数的对比情况

[0047][0048]

图9为实施例1中的mosfet器件的制备工艺流程示意图,主要工艺包括:第一步对衬底进行刻蚀,刻蚀出源极、栅极以及氧化层的区域;第二步在jeft区进行离子注入,形成p-base区和n+区;第三步在刻蚀的区域进行氧化、多晶硅填充、氧化形成源极区域,第四步在形成的源极区域上方重复第三步的操作,然后形成栅极区域;最后,淀积金属电极形成源极、栅极、漏极。

[0049]

综上所述,本发明公开了一种槽型分裂栅集成沟道二极管的mosfet器件,在传统的mosfet器件结构上,通过器件在栅极下表面引入分裂栅和沟道二极管(由沟道二极管n+区5和沟道二极管p-base 6组成),其中分裂栅屏蔽了栅极与漏极的耦合面积,从而大幅降低了器件的反馈电容和栅极电荷,最终提高器件的开关速度;与此同时,由于沟道mos二极管的存在,在反向恢复时,沟道二极管抑制了寄生pn结二极管的开启,大幅降低了寄生pn结二极管空穴的注入效率,从而降低了反向恢复电荷、反向峰值电流和反向恢复时间,最终改善了器件的反向恢复性能。因此,本发明的槽型分裂栅集成沟道二极管的mosfet器件对于

传统的mosfet器件在开关性能和反向恢复性能方面进行了改善。

[0050]

最后说明的是,以上实施例仅用以说明本发明的技术方案而非限制,尽管参照较佳实施例对本发明进行了详细说明,本领域的普通技术人员应当理解,可以对本发明的技术方案进行修改或者等同替换,而不脱离本技术方案的宗旨和范围,其均应涵盖在本发明的权利要求范围当中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1