集成电路的制作方法

1.本发明涉及半导体技术领域,尤其涉及一种集成电路。

背景技术:

2.根据现有技术,电子设备中的控制电路可以通过ic(integrated circuit,集成电路)制造(fabrication)来实现。例如,设计公司可以根据一些设计规则来设计控制电路等电路,而制造过程可以在一个或多个高度专业化的半导体制造工厂中进行,这些工厂可以称为代工厂或晶圆厂。在集成电路的量产阶段,可以从晶圆获得的晶粒(die)数量可能取决于晶粒的大小,而总成本可能取决于从晶圆获得的所有晶粒中功能正常的晶粒数量。尽管相关技术可能已经努力提高良率,但似乎由于瓶颈而无法进一步降低成本。因此,需要一种新颖的方法和相关架构来节省ic的整个电路面积而不引入副作用或以不太可能引入副作用的方式。

技术实现要素:

3.有鉴于此,本发明提供一种集成电路,以解决上述问题。

4.根据本发明的第一方面,公开一种集成电路,包括:

5.多个功能块,该多个功能块中的每个功能块包括硬件电路,其中,该多个功能块包括:

6.第一功能块,包括:第一宏电路,位于该第一功能块的第一子区域内,其中该第一子区域的多个侧中,该第一子区域的第一侧最靠近该第一功能块的边界;

7.其中,该第一功能块的第一中间子区域位于该第一子区域的该第一侧与该第一功能块的该边界之间,并且在该第一功能块的该第一中间子区域中不存在分接单元。

8.本发明的集成电路由于包括:多个功能块,该多个功能块中的每个功能块包括硬件电路,其中,该多个功能块包括:第一功能块,包括:第一宏电路,位于该第一功能块的第一子区域内,其中该第一子区域的多个侧中,该第一子区域的第一侧最靠近该第一功能块的边界;其中,该第一功能块的第一中间子区域位于该第一子区域的该第一侧与该第一功能块的该边界之间,并且在该第一功能块的该第一中间子区域中不存在分接单元。本发明将功能块之内的分接单元进行省略,在将功能块之内的分接单元省去后,可以继续保证对宏电路的正常供电,同时减少了零部件,减少了集成电路的面积,因此也简化了制程和减少了成本。

附图说明

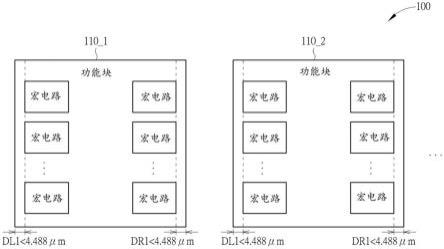

9.图1是根据本发明实施例的ic的示意图。

10.图2是在其右半部分示出了根据本发明实施例的用于实现ic(诸如图1所示的ic)的方法的紧凑布局控制方案的图,为了更好地理解,图2的左半部分示出了非紧凑布局控制方案。

11.图3是在其右半部分示出了根据本发明的一个实施例的图2所示的紧凑布局控制方案的一些实施细节的示意图,为了更好地理解,图3的左半部分示出了非紧凑布局控制方案的一些实施细节。

12.图4是在其右半部分示出了根据本发明另一实施例的图2所示的紧凑布局控制方案的一些实施细节的示意图,为了更好地理解,图4的左半部分示出了非紧凑布局控制方案的一些实施细节。

13.图5是在其右半部分示出了根据本发明实施例的图2所示的紧凑布局控制方案的一些实施细节的示意图,为了更好地理解,图5的右半部分示出了非紧凑布局控制方案的一些实施细节。

14.图6是在其右半部分示出了根据本发明另一实施例的图2所示紧凑布局控制方案的一些实施细节的示意图,为了更好地理解,图6的右半部分示出了非紧凑布局控制方案的一些实施细节。

15.图7是示出通过使用根据本发明实施例的方法实现的改进的图。

具体实施方式

16.在下面对本发明的实施例的详细描述中,参考了附图,这些附图构成了本发明的一部分,并且在附图中通过图示的方式示出了可以实践本发明的特定的优选实施例。对这些实施例进行了足够详细的描述,以使本领域技术人员能够实践它们,并且应当理解,在不脱离本发明的精神和范围的情况下,可以利用其他实施例,并且可以进行机械,结构和程序上的改变。本发明。因此,以下详细描述不应被理解为限制性的,并且本发明的实施例的范围仅由所附权利要求限定。

17.将理解的是,尽管术语“第一”、“第二”、“第三”、“主要”、“次要”等在本文中可用于描述各种元件、组件、区域、层和/或部分,但是这些元件、组件、区域、这些层和/或部分不应受到这些术语的限制。这些术语仅用于区分一个元件、组件、区域、层或部分与另一区域、层或部分。因此,在不脱离本发明构思的教导的情况下,下面讨论的第一或主要元件、组件、区域、层或部分可以称为第二或次要元件、组件、区域、层或部分。

18.此外,为了便于描述,本文中可以使用诸如“在...下方”、“在...之下”、“在...下”、“在...上方”、“在...之上”之类的空间相对术语,以便于描述一个元件或特征与之的关系。如图所示的另一元件或特征。除了在图中描述的方位之外,空间相对术语还意图涵盖设备在使用或运行中的不同方位。该装置可以以其他方式定向(旋转90度或以其他定向),并且在此使用的空间相对描述语可以同样地被相应地解释。另外,还将理解的是,当“层”被称为在两层“之间”时,它可以是两层之间的唯一层,或者也可以存在一个或多个中间层。

19.术语“大约”、“大致”和“约”通常表示规定值的

±

20%、或所述规定值的

±

10%、或所述规定值的

±

5%、或所述规定值的

±

3%、或规定值的

±

2%、或规定值的

±

1%、或规定值的

±

0.5%的范围内。本发明的规定值是近似值。当没有具体描述时,所述规定值包括“大约”、“大致”和“约”的含义。本文所使用的术语仅出于描述特定实施例的目的,并不旨在限制本发明。如本文所使用的,单数术语“一”,“一个”和“该”也旨在包括复数形式,除非上下文另外明确指出。本文所使用的术语仅出于描述特定实施例的目的,并不旨在限制本发明构思。如本文所使用的,单数形式“一个”、“一种”和“该”也旨在包括复数形式,除非上下文

另外明确指出。

20.将理解的是,当将“元件”或“层”称为在另一元件或层“上”、“连接至”、“耦接至”或“邻近”时,它可以直接在其他元件或层上、与其连接、耦接或相邻、或者可以存在中间元件或层。相反,当元件称为“直接在”另一元件或层“上”、“直接连接至”、“直接耦接至”或“紧邻”另一元件或层时,则不存在中间元件或层。

21.注意:(i)在整个附图中相同的特征将由相同的附图标记表示,并且不一定在它们出现的每个附图中都进行详细描述,并且(ii)一系列附图可能显示单个项目的不同方面,每个方面都与各种参考标签相关联,这些参考标签可能会出现在整个序列中,或者可能只出现在序列的选定图中。

22.图1是根据本发明实施例的ic 100的示意图。ic 100可以包括多个功能块,例如功能块110_1、110_2等,并且多个功能块中的每个功能块可以包括硬件电路,例如多个宏电路(macro circuit)。多个宏电路中的任何宏电路的示例可以包括但不限于:静态随机接入存储器(static random access memory,sram)、知识产权(intellectual property,ip)模块等。为了更好地理解,ic 100可以表示控制电子设备中的电路,更具体地,可以表示包括至少一个处理器/微处理器等的处理电路,但本发明不限于此。

23.如图1所示,在多个功能块中的任意一个功能块(例如,每个功能块)中,例如功能块110_1、110_2等中的功能块110_i(例如,功能块索引i可以表示正整数),任一功能块的第一边界线(例如左侧的边界线)与靠近任一功能块的第一边界线(例如左侧的边界线)的宏电路之间的距离dl1小于4.488微米(μm),任一功能块的另一条边界线(例如右侧的边界线)(或称为第二边界线)与靠近任一功能块的另一条边界线(例如右侧的边界线)(或称为第二边界线)的宏电路之间的距离dr1小于4.488μm。边界又可称为边缘,边界线又可称为边缘线。边界线可以简称为边界。

24.基于图1所示的架构,ic 100可以配备紧凑的布局布置。与现有技术相比,ic 100可以在各种情况下正确操作(运行),同时ic 100的整体电路面积进一步减小。因此,相关成本可以相应地进一步降低。

25.图2是在其右半部分示出了根据本发明实施例的用于实现诸如图1所示的ic 100的ic的方法的紧凑布局控制方案的图,为了更好地理解,图2的左半部分示出了非紧凑布局控制方案(例如图2的左半部分为传统的做法)。在根据图2左半部分所示的非紧凑版图控制方案实现的ic中,该ic中的功能块的边界与该功能块中的宏电路之间的中间子区域的每个中间子区域可以包括多个分接单元(tap cell)(为简洁起见标记为“具有分接单元的中间子区域”),并且更具体地,包括位于多个分接单元的一侧(如左侧)的边界单元的第一一维(1d)阵列(例如左侧的第一一维阵列的分接单元),并且进一步包括位于多个分接单元的另一侧(如右侧)的边界单元的第二一维阵列(例如右侧的第二一维阵列的分接单元)。因此,功能块的左边界线(例如,左侧的边界线)与靠近左边界线的宏电路之间的距离dl0通常大于或等于4.488μm(为简洁标记为“dl0≥4.488μm”),以及功能块的右边界线(例如,右侧的边界线)与靠近右边界线的宏电路之间的距离dr0通常大于或等于4.488μm(为简洁起见,标记为“dr0≥4.488μm”)。

26.在根据如图2右半部分所示的紧凑布局控制方案实现的ic 100中,功能块110的多个功能块中的第一功能块110(为简洁起见标记为“功能块”)的边界与功能块110中的宏电

路之间的中间子区域的每个中间子区域不包括任何分接单元(为简洁起见标记为“没有任何分接单元的中间子区域”)。第一功能块110可以代表多个功能块中的任意一个功能块,例如功能块110_1、110_2等中的功能块110_i。第一功能块110可以包括第一组宏电路ml(1)、ml(2)、...和ml(n),它们靠近第一功能块110的第一边界线(例如,左侧的边界线),并且第一功能块110可以进一步包括第二组宏电路mr(1)、mr(2)、

…

和mr(m),它们靠近第一功能块110的另一条边界线(例如,右侧的边界线,又称为第二边界线),其中第一组宏电路ml(1)、ml(2)、

……

和ml(n)的宏电路数量n和第二组宏电路mr(1),mr(2),...和mr(m)的宏电路数量m中的任意宏电路数可以是大于2的正整数,更具体地,可以是远大于2的正整数,但本发明不限于此。例如,第一功能块110可以进一步包括一组或多组宏电路,例如位于第一组宏电路ml(1),ml(2),

…

和ml(n)和第二组宏电路mr(1),mr(2),

…

和mr(m)之间的其他组宏电路。其中,中间子区域位于功能块的边界线和与该边界线最近的宏电路的一边或一侧之间的间隔区域中,例如图2右半部分的距离dl1和dr1的区域中。例如图2右半部分中,功能块的左侧示出了三个中间子区域,功能块的右侧示出了三个中间子区域。

27.以第一组宏电路ml(1)、ml(2)、

……

、ml(n)中的第n个宏电路为例,第一功能块110可以包括第一宏电路ml(n),其位于在第一功能块110的第一子区域内,其中宏电路索引n可以是落在区间[1,n]内的正整数。在第一子区域的多个边或侧(side)中,例如第一宏电路ml(n)所在子区域的四个边中,第一子区域的第一边或第一侧(例如,左侧)最靠近第一功能块110的边界。此外,第一功能块110的第一中间子区域位于第一子区域(例如,第一宏电路ml(n)所在的子区域)的第一侧(例如,左侧)和第一功能块110的边界(例如第一功能块110的左边界,或称为第一边界线)之间,并且在第一功能块110的第一中间子区域中没有分接单元。因此,第一子区域的第一边(或第一侧)与第一功能块110的边界之间距离,例如第一宏电路ml(n)与的第一功能块110的第一边界线(例如,左侧的边界线)之间的距离dl1小于4.488μm(为简洁起见,标记为“dl1《4.488μm”)。第一子区域可以是第一宏电路ml(n)所在的区域,本发明实施例中第一组宏电路具有多个宏电路,因此还可以具有第二子区域,例如第二子区域可以是第二宏电路ml(n-1)或ml(n-2)或ml(n+1)所在的区域。当然还可以具有其他子区域,为简洁起见在此不一一列举;在一个实施例中,第一功能块110的第二中间子区域位于第二子区域(例如,第一宏电路ml(n-1)所在的子区域)的第一侧(例如,左侧)和第一功能块110的边界(例如第一功能块110的左边界,或称为第一边界线)之间,并且在第一功能块110的第二中间子区域中没有分接单元。在一个实施例中,相似的,其他的中间子区域亦没有分接单元。

[0028]

类似地,以第二组宏电路mr(1)、mr(2)、

……

和mr(m)中的第m个宏电路为例,第一功能块110可以包括另一个第一宏电路mr(m)(或称为第三宏电路),其位于第一功能块110的另一个第一子区域(或称为第三子区域)内,其中宏电路索引m可以是落在区间[1,m]内的正整数。在另一个第一子区域(或称为第三子区域)的多个边中,例如另一个第一宏电路mr(m))(或称为第三宏电路)所在的子区域的四个边中,另一个第一子区域(或称为第三子区域)的第一边或第一侧(例如,右侧)最靠近第一功能块110的边界(例如第一功能块110的右边界,或称为第二边界线或另一条边界线)。此外,第一功能块110的另一个第一中间子区域(或称为第三中间子区域)位于另一个第一子区域(例如,另一个第一宏电路mr(m)所在的子区域,或称为第三子区域)的另一个第一侧(例如,右侧)(或称为第二侧)和第一功能块110

的边界(例如第一功能块110的右边界,或称为第二边界线或另一条边界线)之间,并且在第一功能块110的另一个第一中间子区域中没有分接单元。因此,另一个第一子区域(第三子区域)的第一边与第一功能块110的边界(例如第一功能块110的右边界,或称为第二边界线或另一条边界线)之间的距离,例如另一第一宏电路mr(m)(第三宏电路mr(m))与第一功能块110的另一条边界线(例如,右侧的边界线,又称为第二边界线)之间的距离dr1小于4.488μm(为简洁起见,标记为“dr1《4.488μm”)。另一个第一子区域或第三子区域可以是第三宏电路mr(m)所在的区域,本发明实施例中第二组宏电路具有多个宏电路,因此还可以具有第四子区域,例如第四子区域可以是第四宏电路ml(m-1)或ml(m-2)或ml(m+1)所在的区域。当然还可以具有其他子区域,为简洁起见在此不一一列举;在一个实施例中,第一功能块110的第四中间子区域位于第四子区域(例如,第四宏电路ml(m-1)所在的子区域)的另一个第一侧(例如,右侧,或称为第二侧)和第一功能块110的边界(例如第一功能块110的右边界,或称为第二边界线或另一条边界线)之间,并且在第一功能块110的第四中间子区域中没有分接单元。在一个实施例中,相似的,其他的中间子区域亦没有分接单元。

[0029]

根据本实施例,第一功能块110的边界可以包括多条边界线,例如在第一功能块110的四个边上的四个边界线,其中,第一功能块110的第一中间子区域位于第一子区域(例如,第一宏电路ml(n)所在的子区域)的第一侧(例如,左侧)与多条边界线中的第一边界线(例如左侧或左边的边界线)之间,第一功能块110的另一第一中间子区域(或称为第三中间子区域)位于另一个第一子区域(或称为第三子区域)(例如,另一个第一宏电路mr(m),或第三宏电路mr(m)所在的子区域)的另一个第一侧(例如,右侧)(或称为第二侧)与多条边界线中的另一条边界线(或称为第二边界线,也即右侧或右边的边界线)之间。

[0030]

根据一些实施例,第一宏电路ml(n)和另一个第一宏电路mr(m)(或第三宏电路mr(m))中的任何一个可以是sram。例如,第一组宏电路ml(1)、ml(2)、

……

和ml(n)中的任何一个都可以是sram。又例如,第二组宏电路mr(1)、mr(2)、

……

和mr(m)中的任何一个都可以是sram。在一些示例中,第一组宏电路ml(1)、ml(2)、

……

和ml(n)和第二组宏电路mr(1),mr(2),

…

和mr(m)中的至少一个宏电路(例如,一个或多个宏电路)可以是sram。

[0031]

图3是根据本发明的一个实施例的图2所示的紧凑布局控制方案的一些实施细节的示意图,为了更好的理解,图3的左半部分示出了非紧凑布局控制方案的一些实施细节。图3左半部分所示的宏电路可以作为图2左半部分所示功能块内靠近左侧边界线的宏电路中的任意一个宏电路的示例。功能块的边界与该功能块中的宏电路之间的中间子区域可以包括一组tap单元(tap cell,在一个实施例中又可称为分接单元(tap cell)),例如四个tap单元(标记为“为简洁起见,具有分接单元的中间子区域),更具体地,包括位于该组tap单元的一侧的一组边界单元,并且还包括位于该组tap的另一侧的另一组边界单元,其中tap单元组、边界单元组和另一组边界单元可以分别作为多个分接单元、边界单元的第一一维阵列和第二一维阵列的示例。因此,宏电路与功能块的左边界线(为简洁标记为“边界线”)之间的距离dl0通常大于或等于4.488μm(为简洁标记为“dl0≥4.488μm”)。如图3的左半部分所示,在距离dl0的区域中,一组分接单元和分别比特于它相对的两侧的第一组边界单元和第二组边界单元共同组成具有正常功能的分接单元功能组(或分接功能单元)。其中,边界单元是用于将tap单元和其他电路元件进行电性隔离的,也即边界单元是绝缘的隔离元件。当然图3的左半部分中,仅示出了在功能块的左侧的边界线之内的分接单元功能组

(位于功能块之内),实际上还有在功能块的左侧的边界线之外的分接单元功能组(位于功能块之外,不在任何功能块内),为简洁起见图中未示出。

[0032]

图3右半部分所示的宏电路ml(n)可以作为上述第一组宏电路ml(1)、ml(2)、

……

中的第一宏电路ml(n)的示例。图2右半部分所示的第一功能块110内的ml(n)。第一功能块110的边界与第一功能块110中的宏电路ml(n)之间的中间子区域(位于距离dl1的区域中)不包括任何分接单元(为简洁起见,标记为“没有任何分接单元的中间子区域”)。因此,宏电路ml(n)与第一功能块110的第一边界线(简称为“边界线”)之间的距离dl1小于4.488μm(简称为“dl1《4.488μm”)。根据该实施例,ic 100可以包括top通道(top channel)中的一些tap单元,例如位于第一功能块110外部并且靠近宏电路ml(n)的一组tap单元(例如,四个tap单元),其中ic 100还可以包括一组边界单元,该一组边界单元位于该组tap单元和邻近宏电路ml(n)的中间子区域之间。例如,ic 100可以通过这组tap单元和相关的布线向宏电路ml(n)供电,但本发明不限于此。如图3的右半部分所示,在距离dl1的区域中没有设置tap单元或分接单元。当然设置在功能块的左侧的边界线之外的分接单元功能组(位于功能块之外)仍然存在,图3的右半部分为了简洁并未将分接单元功能组全部示出,省略了一组分接单元的左边的一组边界单元。在传统的做法中,不仅在功能块的左侧的边界线之内的具有分接单元功能组(位于功能块之内),还具有在功能块的左侧的边界线之外的分接单元功能组(位于功能块之外)。这些分接单元功能组(包括位于功能块之内和之外的)为相邻的宏电路提供电源,传统的方案中一直采用上述做法。然而发明人经过研究后,创造性的发现功能块之内的分接单元功能组可以省略,在将功能块之内的分接单元功能组省去后,可以继续保证对宏电路的正常供电,因此发明人提出了本发明。本发明在省略功能块之内的分接单元功能组之后仍然保证了半导体电路的正常运行和稳定性,同时减少了零部件,减少了集成电路的面积,因此也简化了制程和减少了成本。

[0033]

如图3的右上部分和右下部分所示,第一功能块110还可以包括一组边界单元bl(n-1)和一组边界单元bl(n)(或称为边界单元组bl(n-1)和边界单元组bl(n)),其中,边界单元bl(n-1)和边界单元集合bl(n)可以以相同或相似的方式实现,但本发明不限于此。这些边界单元可以用于隔离相邻的宏电路。例如,当宏电路索引n不等于1时,宏电路索引n可以等于区间[2,n]内的任意整数。在这种情况下,该组边界单元bl(n-1)可以位于宏电路ml(n)和第一功能块110内的相邻组件(例如,宏电路ml(n-1))之间,其中,在第一子区域(例如,宏电路ml(n)所在的子区域)的多个边中,第一子区域的第二边(例如,上边)最靠近相邻组件(边界单元组或集合bl(n-1))。又例如,当宏电路索引n不等于n时,宏电路索引n可以等于区间[1,(n-1)]内的任意整数。在这种情况下,该组边界单元bl(n)可以位于第一功能块110内的宏电路ml(n)和相邻组件(例如,宏电路ml(n+1))之间,其中第一子区域(例如,宏电路ml(n)所在的子区域)的多个边(或侧),第一子区域的另一第二边(又称为第三边或第三侧)(例如,下边或下侧)最靠近相邻元件(组件)。相邻组件可以是指边界单元组或宏电路,在一个实施例中,从上下的方向来说,边界单元组与宏电路交替设置;边界单元组用于将相邻的宏电路进行隔离,例如电性隔离。

[0034]

根据该实施例,第一子区域(例如,宏电路ml(n)所在的子区域)的第一边(例如,左侧)与边界单元集合bl(n-1)和边界单元集合bl(n)(或边界单元组bl(n-1)和边界单元组bl(n))中任意边界单元集合(或边界单元组)的左侧之间的距离可以等于第一功能块110的第

一边界线(为简洁起见标记为“边界线”)与任意一组边界单元的左侧之间的距离d1,因此也可以标记为“d1”,如图3所示,但本发明不限于此。例如,第一子区域的第一侧与任意一组边界单元的左侧之间的距离可以变化,并且更具体地,可以大于d1。此外,边界单元集合bl(n-1)和边界单元集合bl(n)中任意边界单元集合的每个边界单元的宽度(例如,在图3的垂直方向上测量的长度)可以等于d0,并且任意一组边界单元的两个子集(例如,两个上边界单元和两个下边界单元)之间的距离可以等于d2。在一个实施例中,任意一组边界单元(例如边界单元集合bl(n-1))的两个子集之间,可以存在其他的边界单元(这些其他的边界单元的长度可以较短,高度可以与长度较长的边界单元的高度相同),其中两个较长的边界单元的距离d2可以等于2倍的距离d0。此外如图3右半部分所示,距离d1可以等于电路设计的最小规范距离,而宏电路与功能块的边界线之间的距离等于d1的两倍,从而使集成电路运行稳定。

[0035]

图4是根据本发明另一实施例的图2所示的紧凑布局控制方案的一些实施细节的示意图,为了更好地理解,图4的左半部分示出了非紧凑布局控制方案的一些实施细节。与图3所示的实施例相比,在本实施例中,宏电路ml(n)的宏电路索引n可以等于n。在这种情况下,边界单元集合bl(n-1)可以位于第一功能块110内的宏电路ml(n)和相邻组件(例如,宏电路ml(n-1))之间,其中,在第一子区域(例如,宏电路ml(n)所在的子区域)的多个边中,第一子区域的第二侧(例如,上侧)最接近相邻组件。此外,边界单元集合bl(n)可以位于宏电路ml(n)和多条边界线的第三边界线(例如,下边界线,为简洁起见标记为“边界线”)之间,其中,在第一子区域(例如,宏电路ml(n)所在的子区域)的多个边中,第一子区域的第三边(例如,下边)最靠近第三边界线。为简洁起见,本实施例类似的描述在此不再赘述。

[0036]

在图4所示的实施例中,第一功能块110的左下角周围的宏电路ml(n)和边界单元集合(边界单元组)bl(n)的布置可以作为第一功能块110的四个角周围的布置的示例,但本发明不限于此。例如,围绕第一功能块110的左上角的布置可以类似于围绕第一功能块110的左下角的布置,并且更具体地,可以是围绕第一功能块110的左下角相对于第一对称轴的布置的镜像版本(例如,穿过第一功能块110的水平中心线)。根据一个实施例,图3所示架构中的宏电路ml(n)的宏电路索引n可以等于1。在这种情况下,该组边界单元bl(1)可以位于第一功能块110内的宏电路ml(1)和相邻组件(例如,宏电路ml(2))之间,其中,在第一子区域(例如,宏电路ml(1)所在的子区域)的多个边中,第一子区域的第二侧(例如,下侧)最接近相邻组件。此外,该组边界单元bl(0)可以位于宏电路ml(1)和多条边界线的第三边界线(例如,上边界线)之间,其中,在第一子区域(例如,宏电路ml(1)所在的子区域)的多个边中,第一子区域的第三边(例如,上边)最接近第三边界线。为简洁起见,本实施例类似的描述在此不再赘述。边界单元组bl(n)与功能块的下边界线之间的距离等于d2,以便隔开距离,保证电路运行稳定。

[0037]

根据一些实施例,围绕第一功能块110的右下角的布置可以类似于围绕第一功能块110的左下角的布置,并且更具体地,可以是围绕第一功能块110的左下角的布置相对于第二对称轴(例如,穿过第一功能块110的垂直中心线)的镜像版本。

[0038]

图5是根据本发明实施例的图2所示的紧凑布局控制方案的一些实施细节的示意图,其中非紧凑布局控制方案的一些实施细节在图5中示出。图5的右半部分以便更好地理解。图5右半部分所示的宏电路可以作为图2左半部分所示功能块内靠近右边界线的宏电路

中的任意一个宏电路的例子。功能块和该功能块中的宏电路的边界可以包括一组tap单元,例如四个tap单元(为简洁标记为“具有tap单元的中间子区域”),更具体地,包括一组边界单元位于该组tap的一侧并且进一步包括位于该组tap的另一侧的另一组边界组,其中该组tap、该组边界和另一组边界可以以多个分接单元为例,边界单元的第一个1d阵列和第二个一维边界单元阵列,分别。因此,宏电路与功能块的右侧边界线(为简洁标记为“边界线”)之间的距离dr0通常大于或等于4.488μm(为简洁标记为“dr0≥4.488μm”)。

[0039]

图5左半部分所示的宏电路mr(m)可以作为前述如图2右半部分所示的第一功能块110内的第二组宏电路mr(1)、mr(2)、...和mr(m)中的另一个第一宏电路mr(m)(第三宏电路mr(m))的示例。第一功能块110的边界和第一功能块110中的宏电路mr(m)之间的中间子区域没有包括任何分接单元(为简洁起见,标记为“没有任何分接单元的中间子区域”)。因此,宏电路mr(m)与第一功能块110的第一边界线(简称为“边界线”)之间的距离dr1小于4.488μm(简称为“dr1《4.488μm”)。根据该实施例,ic 100可以包括top通道中的一些tap单元,例如位于第一功能块110外部并靠近宏电路mr(m)的一组tap单元(例如,四个tap单元),其中ic 100还可以包括一组边界单元,其位于该组tap单元和邻近宏电路mr(m)的中间子区域之间。例如,ic 100可以通过这组tap单元和相关的布线向宏电路mr(m)供电,但本发明不限于此。

[0040]

如图5的左上部分和左下部分所示,第一功能块110还可以包括边界单组元br(m-1)和边界单元组br(m),其中边界单元组br(m-1)和边界单元组br(m)可以以相同或相似的方式实现,但本发明不限于此。例如,当宏电路索引m不等于1时,宏电路索引m可以等于区间[2,m]内的任意整数。在这种情况下,该边界单元组br(m-1)可以位于第一功能块110内的宏电路mr(m)和相邻组件(例如,宏电路mr(m-1))之间,其中,在另一个第一子区域(例如,宏电路mr(m)所在的子区域)(可称为第二子区域)的多个边中,另一个第一子区域的第二边(例如,上边)最近到相邻的组件。又例如,当宏电路索引m不等于m时,宏电路索引m可以等于区间[1,(m-1)]内的任意整数。在这种情况下,边界单元集合br(m)(或一组边界单元br(m)、边界单元组br(m))可以位于第一功能块110内的宏电路mr(m)和相邻组件(例如,宏电路mr(m+1))之间,其中另一个第一子区域(例如,宏电路mr(m)所在的子区域)的多个边,另一个第一子区域的另一个第二边(例如,下边)(例如可称为第四边)最接近于相邻组件。

[0041]

根据本实施例,另一个第一子区域(例如,宏电路mr(m)所在的子区域)的第一边(例如,右侧)与任意集合的右侧之间的距离边界单元集合br(m-1)与边界单元集合br(m-)和边界单元集合br(m)中任意边界单元集合的右侧之间的距离可以等于在第一功能块110的另一条边界线与任何一组边界单元的右侧之间的距离d1,因此也可以如图5所示标记为“d1”,但本发明不限于此。例如,另一个第一子区域的第一侧与任意一组边界单元的右侧之间的距离可以变化,并且更具体地,可以大于d1。此外,边界单元集合br(m-1)和边界单元集合br(m)中任意边界单元集合的每个边界单元的宽度(例如,在图5的垂直方向上测量的长度)可以等于d0,并且任意一组边界单元的两个子集(例如,两个上边界单元和两个下边界单元)之间的距离可以等于d2。图5所示的示例与图3所示的示例可以是镜像版本,它们两者关于功能块的竖直中心轴对称。因此图3所示的结构在对称后适用于图5所示的结构,在此不再对图5进行赘述。

[0042]

图6是根据本发明另一实施例的图2所示紧凑布局控制方案的一些实施细节的示意图,其中非紧凑布局控制方案的一些实现细节在图6的右半部分示出,以便更好地理解。

与图5所示的实施例相比,在本实施例中,宏电路mr(m)的宏电路索引m可以等于m。在这种情况下,该组边界单元br(m-1)可以位于宏电路mr(m)和第一功能块110内的相邻组件(例如,宏电路mr(m-1))之间,其中在另一个第一子区域(例如,宏电路mr(m)所在的子区域)的多个边中,另一个第一子区域的第二侧(例如,上侧)最接近相邻组件。此外,该组边界单元br(m)可以位于宏电路mr(m)和多条边界线的第二边界线(例如,下边界线,为简洁起见标记为“边界线”)之间,其中,在另一个第一子区域(例如,宏电路mr(m)所在的子区域)的多个边中,另一个第一子区域的第三边(例如,下边)最近到第二条边界线。为简洁起见,本实施例类似的描述在此不再赘述。

[0043]

在图6所示的实施例中,第一功能块110的右下角周围的宏电路mr(m)和边界单元集合br(m)的布置可以作为第一功能块110的四个角周围的布置的示例,但本发明不限于此。例如,围绕第一功能块110的右上角的布置可以类似于围绕第一功能块110的右下角的布置,并且更具体地,可以是围绕第一功能块110的右下角相对于第一对称轴(例如,穿过第一功能块110的水平中心线)的布置的镜像版本。根据一个实施例,图5所示架构中的宏电路mr(m)的宏电路索引m可以等于1。在这种情况下,边界单元组br(1)可以位于第一功能块110内的宏电路mr(1)和相邻组件(例如,宏电路mr(2))之间,其中,在另一个第一子区域(例如,宏电路mr(1)所在的子区域)的多个边中,另一个第一子区域的第二边(例如,下边)最靠近相邻组件。此外,边界单元组br(0)可位于宏电路mr(1)与多条边界线中的第三条边界线(例如,上边界线)之间,其中,在另一个第一子区域(例如,宏电路mr(1)所在的子区域)的多个边中,另一个第一子区域的第三边(例如,上边)最靠近第三边界线。在本实施例中,围绕第一功能块110的右下角和右上角的布置可以分别类似于围绕第一功能块110的左下角和左上角的布置,更具体地,可以是围绕第一功能块110的左下角和左上角分别相对于第二对称轴(例如,通过第一功能块110的垂直中心线)的布置的镜像版本。为简洁起见,本实施例类似的描述在此不再赘述。图6所示的示例与图4所示的示例可以是镜像版本,它们两者关于功能块的竖直中心轴对称。因此图4所示的结构在对称后适用于图6所示的结构,在此不再对图6进行赘述。

[0044]

图7是示出通过使用根据本发明实施例的方法实现的改进的图。与根据非紧凑版图控制方案实现的ic中的功能块相比,根据紧凑版图控制方案实现的ic 100中的第一功能块110可以节省对应于距离dl0与距离dl1之差δdl的不必要电路面积(为简洁起见,标记为“节省δdl”),以及节省对应于距离dr0与距离dr1之差δdr的不必要电路面积(为简洁起见,标记为“节省δdr”)。为了便于理解,假设第一功能块110在图7的水平方向的尺寸等于dx,第一功能块110在图7的垂直方向的尺寸等于dy,因此集成电路ic 100中的第一功能块110的面积等于(dx*dy)。在这种情况下,对于每个功能块来说,减少电路面积的改进可以用面积减少率rar表示,如下所示:rar=(((δdl+δdr)*dy)/((dx+δdl+δdr)*dy));或者rar=((δdl+δdr)/(dx+δdl+δdr));但本发明不限于此。例如,δdl=δdr=3.0μm时,这样对于每个功能块来说,减少了0.006mm2的面积。对于具有80个功能块的集成电路来说,可以节省0.48mm2(0.006mm2乘以80)。而原来的集成电路的面积例如是1000μm乘以2840μm=2.84mm2,那么节省的面积比率为0.48mm2/2.84mm2≈0.169=16.9%。又例如原来的集成电路的面积例如是2000μm乘以2000μm=4mm2,那么节省的面积比率为0.48mm2/4mm2=0.12=12%。。因此,ic 100可以在各种情况下正确操作(或运行),同时ic 100的整体电路面积已

进一步减小。因此,相关成本可以相应地进一步降低。经过测算,例如按照上述面积减少率12%,那成本方面可以减少大约12%,在出货量较大的情况下(例如上亿颗),可以减少数十亿的成本。

[0045]

本领域的技术人员将容易地观察到,在保持本发明教导的同时,可以做出许多该装置和方法的修改和改变。因此,上述公开内容应被解释为仅由所附权利要求书的界限和范围所限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1