半导体器件和包括半导体器件的数据存储系统的制作方法

半导体器件和包括半导体器件的数据存储系统

1.相关申请的交叉引用

2.本技术要求于2021年3月24日在韩国知识产权局提交的韩国专 利申请no.10-2021-0038069的优先权,其内容通过引用整体并入本文。

技术领域

3.本发明构思的实施例涉及半导体器件和包括该半导体器件的数 据系统。

背景技术:

4.需要可以在需要数据存储的电子系统中存储高容量数据的半导 体器件。因此,已经研究了用于提高半导体器件的数据存储容量的方 法。例如,为了提高半导体器件的数据存储容量,已经提出了包括三 维存储单元而不是二维存储单元的半导体器件。

5.在vnand闪存器件中,同时形成竖直存储结构和竖直支撑结构, 并且通过不同的工艺形成栅接触插塞、外围接触插塞和使栅堆叠结构 分离的分离结构。

技术实现要素:

6.本发明构思的实施例提供了具有增加的集成度和改进的可靠性 的半导体器件。

7.本发明构思的另一实施例提供了包括半导体器件的数据存储系 统。

8.根据本发明构思的实施例,一种半导体器件,包括:第一结构; 第二结构,所述第二结构包括:堆叠结构,其包括沿竖直方向在第一 结构上堆叠的至少三个栅堆叠组;以及绝缘结构,其覆盖堆叠结构的 至少一部分;竖直存储结构,所述竖直存储结构至少穿透堆叠结构; 以及分离结构,所述分离结构至少穿透堆叠结构,并且所述分离结构 具有位于比竖直存储结构的上表面高的高度处的上表面。至少三个栅 堆叠组中的每个栅堆叠组包括沿竖直方向堆叠并且彼此间隔开的栅层。 在堆叠结构的栅层中的最下栅层与最上栅层之间的高度处,竖直存储 结构的侧表面包括数量为n的多个存储侧表面坡度改变部,并且分离 结构的侧表面包括m个分离侧表面坡度改变部,所述m个分离侧表 面坡度改变部位于与数量为n的多个存储侧表面坡度改变部中的m 个存储侧表面坡度改变部基本上相同的高度处,其中,m<n,n是2 或更大的自然数并且m是1或更大的自然数。

9.根据本发明构思的另一实施例,一种半导体器件,包括:下结构; 上结构,所述上结构包括:堆叠结构,其包括沿竖直方向在下结构上 堆叠的至少三个栅堆叠组;以及绝缘结构,其覆盖堆叠结构的至少一 部分;竖直存储结构,所述竖直存储结构至少穿透堆叠结构;外围接 触插塞;多个栅接触插塞;以及分离结构,所述分离结构至少穿透堆 叠结构,并且所述分离结构在平面图中具有线形。至少三个栅堆叠组 中的每个栅堆叠组包括沿竖直方向堆叠并且彼此间隔开的栅层。在堆 叠结构的栅层中的最下栅层与最上栅层之间的高度处,竖直存储结构 的侧表面和外围接触插塞的侧表面中的每一个包括数量为n的多个第 一坡度改变部,分离结构的侧表面包括m个第二坡度改变部,所述m 个第二坡度改变部位于与所述数量为n的多个第一坡度改变部中的m 个第一坡度改变部基本上相同的高度处,其

中,m<n并且n和m是 彼此不同的自然数。在比最上栅层高的高度处,竖直存储结构的侧表 面、外围接触插塞的侧表面、分离结构的侧表面、以及栅接触插塞中 的每个栅接触插塞的侧表面包括位于基本上相同的高度处的第一上坡 度改变部,以及,在与所述数量为n的多个第一坡度改变部中设置在 最下部的第一坡度改变部相同的高度处,分离结构的侧表面基本上是 竖直的。

10.根据本发明构思的实施例,一种数据存储系统,包括:主基板; 半导体器件,设置在所述主基板上;以及控制器,所述控制器电连接 到所述主基板上的半导体器件。所述半导体器件包括:下结构;上结 构,所述上结构包括:堆叠结构,其包括沿竖直方向在下结构上堆叠 的至少三个栅堆叠组;以及绝缘结构,其覆盖堆叠结构的至少一部分; 竖直存储结构,所述竖直存储结构至少穿透堆叠结构;外围接触插塞; 多个栅接触插塞;以及分离结构,所述分离结构至少穿透堆叠结构, 并且所述分离结构在平面图中具有线形。至少三个栅堆叠组中的每个 栅堆叠组包括沿竖直方向堆叠并且彼此间隔开的栅层。在堆叠结构的 栅层中的最下栅层与最上栅层之间的高度处,竖直存储结构的侧表面 和外围接触插塞的侧表面中的每一个包括数量为n的多个第一坡度改 变部,分离结构的侧表面包括m个第二坡度改变部,所述m个第二 坡度改变部位于与所述数量为n的多个第一坡度改变部中的m个第 一坡度改变部基本上相同的高度处,其中,m<n并且n和m是彼此 不同的自然数。在比最上栅层高的高度处,竖直存储结构的侧表面、 外围接触插塞的侧表面、分离结构的侧表面、以及栅接触插塞中的每 个栅接触插塞的侧表面均包括位于基本上相同的高度处的第一上坡度 改变部,以及,在与所述数量为n的多个第一坡度改变部中设置在最 下部的第一坡度改变部相同的高度处,分离结构的侧表面基本上是竖 直的。

附图说明

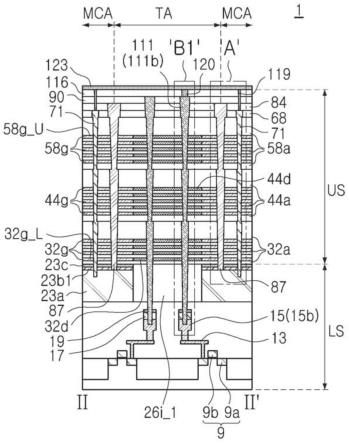

11.图1是根据本发明构思的实施例的半导体器件的示意性透视图。

12.图2a和图2b是根据本发明构思的实施例的半导体器件的示意性 截面图。

13.图3a和图3c是根据本发明构思的实施例的半导体器件的一部分 的示意性局部放大图。

14.图4a和图4b是根据本发明构思的修改的实施例的半导体器件的 示意性截面图。

15.图5a和图5b是根据本发明构思的修改的实施例的半导体器件的 一部分的示意性局部放大图。

16.图6和图7是根据本发明构思的修改的实施例的半导体器件的示 意图。

17.图8是根据本发明构思的修改的实施例的半导体器件的示意性截 面图。

18.图9a和图9b是根据本发明构思的实施例的形成半导体器件的工 艺的流程图。

19.图10a、图10b、图11a和图11b是示出了根据本发明构思的实 施例的形成半导体器件的方法的截面图。

20.图12示意性地示出了根据本发明构思的实施例的包括半导体器 件的数据存储系统。

21.图13是包括根据本发明构思的实施例的半导体器件的数据存储 系统的示意性透视图。

22.图14是包括根据本发明构思的实施例的半导体器件的数据存储 系统的截面图。

具体实施方式

23.在下文中,将参考附图描述本发明构思的实施例。

24.将参考图1描述根据本发明构思的实施例的半导体器件。图1是 根据本发明构思的实施例的半导体器件的示意性透视图。

25.参考图1,在实施例中,半导体器件1包括第一结构ls和设置在 第一结构ls上的第二结构us。第二结构us包括多个存储结构m1 和m2。虽然图1示出两个存储结构m1和m2,但是实施例不限于此, 并且在其他实施例中,可以设置多于两个存储结构。多个存储结构 m1和m2中的每个存储结构包括分离结构87、设置在分离结构87之 间的第一区mca、以及设置在第一区mca的至少一侧上的第二区 sa。

26.在实施例中,第一区mca是存储单元阵列区或存储单元区,并 且第二区sa是阶梯区。

27.在实施例中,第一区mca中设置在彼此间隔开并且彼此平行的 一对分离结构87之间的的第一区(即,存储单元阵列区)是存储块。 多个存储结构m1和m2中的每个存储结构还包括设置在第一区mca 中的一对第一区之间的贯通区ta。半导体器件1还包括外围接触插塞111。至少一些外围接触插塞111穿透贯通区ta。

28.在下文中,将参考图2a和图2b描述半导体器件1的示例。图 2a是沿图1的线i-i’截取的示意性截面图,并且图2b是沿图1的线 ii-ii’截取的示意性截面图。

29.结合图1参考图2a和图2b,在实施例中,半导体器件1的第一 结构ls包括图案化结构23。图案化结构23包括至少一个硅层。

30.在实施例中,图案化结构23包括下图案化层23a、第一中间图案 化层23b1、第二中间图案化层23b2和上图案化层23c。第一中间图案 化层23b1和第二中间图案化层23b2在下图案化层23a上彼此间隔开。 上图案化层23c覆盖下图案化层23a上的第一中间图案化层23b1和第 二中间图案化层23b2。下图案化层23a具有比第一中间图案化层23b1、 第二中间图案化层23b2和上图案化层23c中的每一个厚的厚度。下图 案化层23a、第一中间图案化层23b1、第二中间图案化层23b2和上图 案化层23c中的至少一个包括硅层。例如,下图案化层23a、第一中 间图案化层23b1和上图案化层23c可以包括硅层(例如具有n型导 电性的硅层),并且第二中间图案化层23b2可以包括与硅层的材料不 同的材料。例如,第二中间图案化层23b2可以包括多个顺序堆叠的层, 例如顺序堆叠的氧化硅层、氮化硅层和氧化硅层。

31.在实施例中,第一结构ls包括:半导体衬底5;半导体衬底5 上的外围电路9和外围电路13;电连接到外围电路9和外围电路13 的外围焊盘15;以及在半导体衬底5上并且覆盖外围电路9和外围电 路13以及外围焊盘15的下绝缘结构21。半导体衬底5包括限定有源 区7a的器件隔离层7s。外围电路9和外围电路13包括:电路元件9, 例如包括设置在有源区7a上的外围栅极9a、设置在有源区7a中在外 围栅极9a的两侧上的外围源极/漏极9b的晶体管;以及电连接到电路 元件9的电路互连13。

32.在实施例中,第一结构ls还包括:形成在每个外围焊盘15上的 封盖层17;以及形成在封盖层17上的蚀刻停止层19。在实施例中, 封盖层17由硅层形成,并且蚀刻停止层19由诸如氧化硅或氮化硅之 类的绝缘材料形成。

33.在实施例中,图案化结构23设置在下绝缘结构21上。外围焊盘 15包括接地焊盘15g、第一外围焊盘15a、第二外围焊盘15b和第三 外围焊盘15c。

34.在实施例中,图案化结构23的下图案化层23a的一部分向下延 伸以电连接到接地焊盘15g。接地焊盘15g通过电路互连13接地到半 导体衬底5的接地区11。

35.在实施例中,第一结构ls还包括:设置在图案化结构23外部的 外绝缘层26o;穿透图案化结构23的第一内绝缘层26i_1;以及穿透 图案化结构23的第二内绝缘层26i_2。

36.在实施例中,第一内绝缘层26i_1在平面图中具有线形。每个第 二内绝缘层26i_2可以具有圆形、椭圆形或多边形形状。

37.在实施例中,半导体器件1的第二结构us包括堆叠结构gs,其 设置在第一区mca中并且从第一区mca延伸到第二区sa中。堆叠 结构gs包括沿竖直方向z堆叠的至少三个堆叠组gr1、gr2和gr3。 例如,堆叠结构gs包括下堆叠组gr1、下堆叠组gr1上的中间堆叠 组gr2、和中间堆叠组gr2上的上堆叠组gr3。下堆叠组gr1包括 交替堆叠的下层间绝缘层32a和下栅层32g,中间堆叠组gr2包括交 替堆叠的中间层间绝缘层44a和中间栅层44g,并且上堆叠组gr3包 括交替堆叠的上层间绝缘层58a和上栅层58g。

38.在实施例中,下栅层32g沿竖直方向z堆叠并且彼此间隔开并且 形成下栅堆叠组,中间栅层44g沿竖直方向z堆叠并且彼此间隔开并 且形成中间栅堆叠组,以及上栅层55g在沿竖直方向z堆叠并且彼此 间隔开并且形成上栅堆叠组。在这方面,附图标记32g、附图标记44g 和附图标记55g也可以分别用于指代下栅堆叠组、中间栅堆叠组和上 栅堆叠组。

39.在实施例中,下栅层32g、中间栅层44g和上栅层58g包括栅焊 盘gp,栅焊盘gp在下栅层32g、中间栅层44g和上栅层58g的端部 处并且以阶梯形状布置在第二区sa中。然而,栅焊盘gp不限于图 2a所示的阶梯形状,并且在其他实施例中可以以各种其他形状布置。

40.在实施例中,每个栅焊盘gp的厚度大于下栅层32g、中间栅层44g和上栅层58g中的每一个的厚度。

41.在实施例中,第二结构us还包括覆盖堆叠结构gs的至少一部 分的中间绝缘结构36、48和62。中间绝缘结构36、48和62包括: 设置在下结构ls上并且覆盖下栅层32g的栅焊盘gp的第一中间绝缘 层36;设置在第一中间绝缘层36上并且覆盖中间栅层44g的栅焊盘 gp的第二中间绝缘层48;以及设置在第二中间绝缘层48上并且覆盖 上栅层58g的栅焊盘gp的第三中间绝缘层62。

42.在实施例中,第二结构us还包括设置在堆叠结构gs以及中间 绝缘结构36、48和62上的上绝缘结构68、84、90和116。中间绝缘 结构36、48和62以及上绝缘结构68、84、90和116形成绝缘结构。

43.在实施例中,上绝缘结构68、84、90和116包括:顺序堆叠的 第一上绝缘层68、第二上绝缘层84、第三上绝缘层90和第四上绝缘 层。

44.在实施例中,半导体器件1还包括竖直存储结构71,其在第一区 mca中至少穿透堆叠结构gs。设置了多个竖直存储结构71。竖直存 储结构71向下延伸并且穿透堆叠结构gs且延伸到图案化结构23中。 例如,竖直存储结构71延伸穿过上图案化层23c和第一中间图案化层 23b1并且延伸到下图案化层23a中,以与下图案化层23a接触。竖直 存储结构71从堆叠结构gs向上延伸并且穿透第一上绝缘层68。竖 直存储结构71的上表面与第一上绝缘层68的上表面共面。

45.在实施例中,半导体器件1还包括支撑竖直结构81,其在第二区 sa中至少穿透堆叠结构gs。设置了多个支撑竖直结构81。支撑竖直 结构81延伸到图案化结构23中。例如,支

撑竖直结构81顺序地穿过 上图案化层23c和第二中间图案化层23b2延伸到下图案化层23a中, 以与下图案化层23a接触。支撑竖直结构81从堆叠结构gs向上延伸, 以穿透第一上绝缘层68。支撑竖直结构81的上表面与第一上绝缘层 68的上表面共面。

46.在实施例中,上面参考图1描述的分离结构87至少穿透堆叠结 构gs。分离结构87从堆叠结构gs向下延伸,以与图案化结构23的 下图案化层23a接触。分离结构87从堆叠结构gs向上延伸,以穿透 第一上绝缘层68和第二上绝缘层84。分离结构87的上表面与第二上 绝缘层84的上表面共面。

47.在实施例中,上面参考图1描述的贯通区ta位于第一内绝缘层 26i_1上。贯通区ta包括设置在与下栅层32g、中间栅层44g和上栅 层58g基本上相同的高度处的下水平绝缘层32d、中间水平绝缘层44d 和上水平绝缘层58d。在贯通区ta中,下层间绝缘层32a、中间层间 绝缘层44a和上层间绝缘层58a以及下水平绝缘层32d、中间水平绝 缘层44d和上水平绝缘层58d交替且重复地堆叠。下水平绝缘层32d、 中间水平绝缘层44d和上水平绝缘层58d由氮化硅形成,并且下层间 绝缘层32a、中间层间绝缘层44a和上层间绝缘层58a由氧化硅形成。

48.在实施例中,外围接触插塞111穿透第二结构us的至少一部分。 外围接触插塞111包括第一外围接触插塞111a、第二外围接触插塞 111b和第三外围接触插塞111c。

49.在实施例中,第一外围接触插塞111a与堆叠结构gs间隔开,穿 透中间绝缘结构36、48和62、外绝缘层26o、以及第一上绝缘层68、 第二上绝缘层84和第三上绝缘层90,并且与第一外围焊盘15a接触。 第一外围接触插塞111a的上表面与第三上绝缘层90的上表面共面。

50.在实施例中,第二外围接触插塞111b在贯通区ta中穿透下层间 绝缘层32a、中间层间绝缘层44a和上层间绝缘层58a、以及下水平绝 缘层32d、中间水平绝缘层44d和上水平绝缘层58d,穿透第一内绝缘 层26i_1、以及第一上绝缘层68、第二上绝缘层84和第三上绝缘层 90,并且与第二外围焊盘15b接触。第二外围接触插塞111b的上表面 与第三上绝缘层90的上表面共面。

51.在实施例中,第三外围接触插塞111c与堆叠结构gs间隔开,穿 透中间绝缘结构36、48和62、以及第一上绝缘层68、第二上绝缘层 84和第三上绝缘层90,并且与下图案化层23a接触。第三外围接触插 塞111c的上表面与第三上绝缘层90的上表面共面。

52.在实施例中,外围接触插塞111的下表面位于比竖直存储结构71 的下表面低的高度处,并且外围接触插塞111的上表面位于比竖直存 储结构71的上表面高的高度处。

53.在实施例中,半导体器件1还包括栅接触插塞106,其穿透第二 结构us的至少一部分并且电连接到栅层32g、44g和58g。每个栅接 触插塞106具有:在比栅层32g、44g和58g中的最下栅层32g_l低 的高度处的下表面;以及在比栅层32g、44g和58g中的最上栅层58g_u 高的高度处的上表面。

54.在实施例中,栅接触插塞106分别与栅焊盘gp接触。栅接触插 塞106分别延伸穿过栅焊盘gp。例如,一个栅接触插塞106电连接 到并且延伸穿过一个栅焊盘gp。缓冲绝缘层103设置在位于比栅焊 盘gp低的高度处的那些栅层与栅接触插塞106之间。例如,基于彼 此接触的一个栅焊盘gp和一个栅接触插塞106,缓冲绝缘层103设 置在位于比栅焊盘gp低的栅层与栅接触插塞106之间。缓冲绝缘层 103由氧化硅形成。

55.在实施例中,栅接触插塞106具有在比最下栅层38g_l低的高度 处的下表面和在

比最上栅层58g_u高的高度处的上表面。栅接触插塞 106的下表面位于比竖直存储结构71的下表面低的高度处,并且栅接 触插塞106的上表面位于比竖直存储结构71的上表面高的高度处。

56.在实施例中,半导体器件1包括:位线接触插塞119,其穿透上 绝缘结构68、84、90和116并且电连接到竖直存储结构71;以及上 接触插塞120,其穿透第四上绝缘层116并电连接到外围接触插塞111。

57.在实施例中,半导体器件1还包括:位线123,其在第四上绝缘 层116上并且通过位线接触插塞119电连接到竖直存储结构71;以及 外围互连124,其在第四上绝缘层116上并且通过上接触插塞120分 别电连接到第一外围接触插塞111a和第三外围接触插塞111c。第二外 围接触插塞111b通过一个上接触插塞120电连接到位线123。

58.在下文中,将参考图3a描述上面公开的竖直存储结构71和分离 结构87。图3a是图2b中的区域“a”的局部放大图。

59.结合图1至图2b参考图3a,在实施例中,竖直存储结构71的 在最下栅层32g_l与最上栅层58g_u之间的高度处的侧表面包括数量 为n的多个存储侧表面坡度改变部71s_1a和71s_1b。分离结构87的 侧表面包括设置在与m个坡度改变部71s_1b基本上相同的高度处的 数量为m的多个分离侧表面坡度改变部87s_1,其中,m<n。

60.这里,n是2或更大的自然数,并且m是小于n的自然数,例 如是1或更大的自然数。例如,m可以是n-1。例如,n可以是2并 且m可以是1。

61.在实施例中,m个分离侧表面坡度改变部87s_1位于与n个存储 侧表面坡度改变部71s_1a和71s_1b中比最下存储侧表面坡度改变部 71s_1a设置地高的存储侧表面坡度改变部71s_1b基本上相同的高度 处。

62.在实施例中,在比最上栅层58g_u高的高度处,竖直存储结构 71包括至少一个上侧表面坡度改变部71s_2。

63.在实施例中,在比最上栅层58g_u高的高度处,分离结构87包 括至少一个上侧表面坡度改变部87s_2。竖直存储结构71的上侧表面 坡度改变部71s_2和分离结构87的上侧表面坡度改变部87s_2位于基 本上相同的高度处。

64.在实施例中,“坡度改变部”指侧表面部,其在第一坡度的上侧 表面部与第二坡度的下侧表面之间具有第三坡度,如下定义。第一坡 度和第二坡度中的每一个是竖直的或接近竖直的坡度,并且第三坡度 比第一坡度和第二坡度中的每一个更缓或更不陡峭。第一坡度和第二 坡度中的每一个是陡峭的坡度,并且第三坡度是缓的坡度或更不陡峭 的坡度。例如,竖直存储结构71的侧表面包括:具有陡峭的坡度的下 侧表面部71sa;下侧表面部71sa上方并且具有陡峭的坡度的第一中间 侧表面部71sb;在下侧表面部71sa与第一中间侧表面部71sb之间并 且具有缓的坡度的第一存储侧表面坡度改变部71s_1a;第一中间侧表 面部71sb上方并且具有陡峭的坡度的第二中间侧表面部71sc;在第一 中间侧表面部71sb与第二中间侧表面部71sc之间并且具有缓的坡度 的第二存储侧表面坡度改变部71s_1b;第二中间侧表面部71sc上方并 且具有陡峭的坡度的上侧表面部71sd;以及在第二中间侧表面部71sc 与上侧表面部71sd之间并且具有缓的坡度的上侧表面坡度改变部 71s_2。这里,“陡峭的坡度”和“缓的坡度”是指示相对坡度的术语, 其中,缓的坡度比陡峭的坡度更不陡峭,不同侧部中的陡峭的坡度具 有不同的坡度,并且不同的坡度改变部上的缓的坡

度具有不同的坡度。

65.在实施例中,分离结构87的侧表面包括:具有陡峭的坡度的下 侧表面部87sa;下侧表面部87sa上方并且具有陡峭的坡度的中间侧表 面部87sb;在下侧表面部87sa与中间侧表面部87sb之间并且具有更 缓或更不陡峭的坡度的分离侧表面坡度改变部87s_1;中间侧表面部 87sb上方并且具有陡峭的坡度的上侧表面部87sc;以及在中间侧表面 部87sb与上侧表面部87sc之间并且具有更缓或更不陡的坡度的上坡 度改变部87s_2。

66.因此,在实施例中,即使下面没有单独的描述,“侧表面坡度改 变部”或“坡度改变部”也是设置在设置在侧表面坡度改变部的上部 处的上侧表面部的陡峭的坡度与设置在侧表面坡度改变部的下部处的 下侧表面部的陡峭的坡度之间并且具有缓的坡度的部分。

67.在实施例中,在术语“存储侧表面坡度改变部”和“分离侧表面 坡度改变部”中,术语“存储侧表面”和“分离侧表面”用于可区分 地描述不同组件的改变部并且可以用其他术语坡度替换。例如,“存储 侧表面坡度改变部”和“分离侧表面坡度改变部”可以分别被替换和 描述为“第一坡度改变部”和“第二坡度改变部”,或可以分别被替换 和描述为“第一侧表面坡度改变部”和“第二侧表面坡度改变部”。

68.在实施例中,在最下栅层32g_l与最上栅层58g_u之间的高度处, 竖直存储结构71的n个存储侧表面坡度改变部71s_1a和71s_1b在竖 直方向上位于至少三个相邻的栅堆叠组之间。例如,n个存储侧表面 坡度改变部71s_1a和71s_1b中的第一存储侧表面坡度改变部71s_1a 位于下栅堆叠组32g与中间栅堆叠组44g之间的高度处,并且第二存 储侧表面坡度改变部71s_1b位于中间栅堆叠组44g与上栅堆叠组58g 之间的高度处。

69.在实施例中,分离结构87的侧表面在基本上与最下存储侧表面 坡度改变部71s_1a相同的竖直高度处。

70.在实施例中,每个下栅层32g包括第一层31a和第二层31b。第 一层31a覆盖第二层31b的上表面和下表面并且在竖直存储结构71 和第二层31b之间延伸。此外,中间栅层44g和上栅层55g中的每一 个也包括具有基本上类似的结构的第一层和第二层。

71.在实施例中,第一层31a包括介电材料,并且第二层31b包括导 电材料。例如,第一层31a包括高k电介质(例如,alo),并且第二 层31b包括导电材料(例如,tin、wn、ti或w)。

72.在实施例中,第一层31a包括第一导电材料(例如,tin或w等), 并且第二层31b包括与第一导电材料不同的第二导电材料(例如,ti 或w等)。

73.在实施例中,下栅层32g、中间栅层44g和上栅层58g中的每一 个由掺杂多晶硅、金属半导体化合物(例如,tisi、tasi、cosi、nisi 或wsi)、金属氮化物(例如,tin、tan或wn)或金属(例如,ti 或w)中的至少一个形成。

74.在实施例中,竖直存储结构71包括:间隙填充绝缘层73;沟道 材料层75,其覆盖间隙填充绝缘层73的外表面和底表面;数据存储 结构72,其覆盖沟道材料层73的外表面和底表面;以及间隙填充绝 缘层73上的焊盘图案79。

75.在实施例中,数据存储结构72包括:第一介电层72b,其覆盖沟 道材料层75的外表面和底表面;数据存储层72d,其覆盖第一介电层 72b的外表面和底表面;以及第二介电层72a,其覆盖数据存储层72d 的外表面和底表面。第一介电层72b与沟道材料层73接触,并且数据 存储层72d与沟道材料层73间隔开。

76.在实施例中,间隙填充绝缘层73包括氧化硅,例如由原子层沉 积(ald)工艺形成

的ald氧化硅,或其中形成有空隙的氧化硅。

77.在实施例中,第一介电层72b包括氧化硅或掺杂有杂质的氧化硅。 第二介电层72a包括氧化硅和高k电介质中的至少一个。数据存储层 72d包括捕获电荷的材料,例如氮化硅。

78.在实施例中,数据存储层72d包括在诸如闪存器件之类的半导体 器件中存储数据的区域。沟道材料层73包括多晶硅。焊盘图案79包 括掺杂多晶硅、金属氮化物(例如,tin等)、金属(例如,w等) 或金属半导体化合物(例如,tisi等)中的至少一个。

79.在实施例中,图案化结构23的第一中间图案化层23b1穿透竖直 存储结构71的数据存储结构72,以与沟道材料层73接触。

80.在实施例中,位线接触插塞119包括:插塞图案118b;以及导电 衬里118a,其覆盖插塞图案118b的侧表面和底表面。

81.接下来,将参考图3b描述上面公开的外围接触插塞111。图3b 是图2b的区域b1和图2a的区域b2的局部放大图。在下文中,将 描述第一外围接触插塞111a和第二外围接触插塞111b中的一个的外 围接触插塞111。

82.结合图1至图3a参考图3b,在实施例中,在最下栅层32g_l与 最上栅层58g_u之间的高度处,与竖直存储结构71的侧表面类似, 外围接触插塞111的侧表面包括数量为n的多个外围接触侧表面坡度 改变部111s_1a和111s_1b,其设置在与数量为n的多个存储侧表面 坡度改变部71s_1a和71s_1b基本上相同的高度处。在比最上栅层 58g_u高的高度处,外围接触插塞111包括至少一个上侧表面坡度改 变部111s_2。竖直存储结构71的上侧表面坡度改变部71s_2和外围接 触插塞111的上侧表面坡度改变部111s_2设置在基本上相同的高度处。

83.在实施例中,外围接触插塞111的侧表面包括:下侧表面部111sa; 下侧表面部111sa上方的第一中间侧表面部111sb;在下侧表面部111sa 与第一中间侧表面部111sb之间并且具有比下侧表面部111sa和第一 中间侧表面部111sb中的每一个的坡度更缓或更不陡峭的坡度的第一 外围接触侧表面坡度改变部111s_1a;第一中间侧表面部111sb上方的 第二中间侧表面部111sc;在第一中间侧表面部111sb与第二中间侧表 面部111sc之间并且具有比第一中间侧表面部111sb和第二中间侧表 面部111sc中的每一个的坡度更缓或更不陡峭的坡度的第二外围接触 侧表面坡度改变部111s_1b;第二中间侧表面部111sc上方的上侧表面 部111sd;以及在第二中间侧表面部111sc与上侧表面部111sd之间并 且具有比第二中间侧表面部111sc和上侧表面部111sd中的每一个的 坡度更缓或更不陡峭的坡度的上侧表面坡度改变部111s_2。

84.在实施例中,外围接触插塞111包括:插塞图案113b;以及导电 衬里113a,其覆盖插塞图案113b的侧表面和底表面。插塞图案113b 包括导电材料(例如,钨),并且导电衬里113a包括导电材料(例如,ti或tin)。然而,实施例不限于此,并且在其他实施例中,导电材料 可以用除了所公开的材料以外的各种材料替换。

85.在实施例中,上接触插塞120包括:插塞图案120b;以及导电衬 里120a,其覆盖插塞图案120b的侧表面和底表面。

86.接下来,将参考图3c描述上面公开的栅接触插塞106和支撑竖 直结构81。图3c是图2a中的区域c的局部放大图。在下文中,将 描述栅接触插塞106中的一个。

87.结合图1至图3b参考图3c,在最下栅层32g_l与最上栅层58g_u 之间的高度处,与竖直存储结构71的侧表面类似,栅接触插塞106 的侧表面包括数量为n的多个栅接触侧表面坡度改变部106s_1a和 106s_1b,其设置在与数量为n的多个存储侧表面坡度改变部71s_1a 和71s_1b基本上相同的高度处。在比最上栅层58g_u高的高度处, 栅接触插塞106包括至少两个上侧表面坡度改变部106s_2a和106s_2b。

88.在实施例中,栅接触插塞106的至少两个上侧表面坡度改变部 106s_2a和106s_2b中设置在下部的第一上侧表面坡度改变部106s_2a 位于与竖直存储结构71的上侧表面坡度改变部71s_2基本上相同的高 度处。

89.在实施例中,栅接触插塞106的至少两个上侧表面坡度改变部 106s_2a和106s_2b中设置在上部的第二上侧表面坡度改变部106s_2b 位于比竖直存储结构71的上表面高的高度处。

90.在实施例中,栅接触插塞106包括:插塞图案108b;以及导电衬 里108a,其覆盖插塞图案108b的侧表面和底表面。插塞图案108b包 括导电材料(例如,钨),并且导电衬里108a包括导电材料(例如, ti或tin)。

91.在实施例中,栅接触插塞106包括水平延伸部106p,其从竖直部 沿水平方向延伸接触栅焊盘gp。当栅层设置在比与栅接触插塞106 接触的栅焊盘gp低的高度处时,如上所述,缓冲绝缘层103设置在 比栅焊盘gp低的高度处的栅层与栅接触插塞106之间,并且与水平 延伸部106p重叠。

92.在实施例中,与竖直存储结构71的侧表面类似,在最下栅层32g_l与最上栅层58g_u之间的高度处,支撑竖直结构81的侧表面 包括数量为n的多个支撑侧表面坡度改变部87s_1a和87s_1b,其设 置在与数量为n的多个存储侧表面坡度改变部71s_1a和71s_1b基本 上相同的高度处。在比最上栅层58g_u高的高度处,支撑竖直结构81 包括设置在与竖直存储结构71的上侧表面坡度改变部71s_2基本上相 同的高度处的上侧表面坡度改变部81s_2。

93.在实施例中,支撑竖直结构81由与竖直存储结构71基本上相同 的材料层形成。例如,支持竖直结构81包括:间隙填充绝缘层73’; 沟道材料层75’,其覆盖间隙填充绝缘层73’的外表面和底表面;以 及数据存储结构72’,其覆盖沟道材料层75’的外表面和底表面。数 据存储结构72’包括:第一介电层72b’,其覆盖沟道材料层75’的 外表面和底表面;数据存储层72d’,其覆盖第一介电层72b’的外表 面和底表面;以及第二介电层72a’,其覆盖数据存储层72d’的外表 面和底表面。

94.如上所述,在实施例中,在比最上栅层58g_u高的高度处,竖直 存储结构71的侧表面、每个外围接触插塞111的侧表面、以及支撑竖 直结构81的侧表面、以及每个栅接触插塞106的侧表面包括设置在基 本上相同的高度处的第一上坡度改变部71s_2、81s_2、111s_2和 106s_2a,并且每个栅接触插塞106的侧表面包括设置在比第一上坡度 改变部71s_2、81s_2、111s_2和106s_2a高的高度处的第二上坡度改 变部106s_2b。

95.接下来,将参考图4a和图4b描述根据本发明构思的修改的实施 例的半导体器件。图4a是沿图1的线i-i’截取的示意性截面图,并 且图4b是沿图1的线ii-ii’截取的示意性截面图。在参考图4a和图 4b的根据本发明构思的修改的实施例的半导体器件的描述中,将描述 上述半导体器件1的组件中被修改或被替换的组件,并且将省略与上 述组件基本上

相同的组件、根据上述组件可以很容易地理解的组件、 或根据上述附图可以很容易地理解的组件的描述。

96.参考图4a和图4b,在实施例中,半导体器件1’包括第一结构 ls和设置在第一结构ls上的第二结构us。上面参考图2a和图2b 描述的包括至少三个堆叠组gr1、gr2和gr3的堆叠结构gs被替换 为包括至少四个堆叠组gr1、gr2a、gr2b和gr3的堆叠结构gs’。

97.在实施例中,四个堆叠组gr1、gr2a、gr2b和gr3包括:下 堆叠组gr1;设置在下堆叠组gr1上的第一中间堆叠组gr2a;设置 在第一中间堆叠组gr2a上的第二中间堆叠组gr2b;以及设置在第二 中间堆叠组gr2b上的上堆叠组gr3。下堆叠组gr1包括交替堆叠的 下层间绝缘层32a和下栅层32g,第一中间堆叠组gr2a包括交替堆 叠的第一中间层间绝缘层44a1和第一中间栅层44g1,第二中间堆叠 组gr2b包括交替堆叠的第二中间层间绝缘层44a2和第二中间栅层 44g2,并且上堆叠组gr3包括交替堆叠的上层间绝缘层58a和上栅层 58g。

98.在实施例中,下栅层32g堆叠并且彼此间隔开并且形成下栅堆叠 组,第一中间栅层44g1堆叠并且彼此间隔开并且形成第一中间栅堆叠 组,第二中间栅层44g2堆叠并且彼此间隔开并且形成第二中间栅堆叠 组,以及上栅层55g堆叠并且彼此间隔开并且形成上栅堆叠组。在这 方面,附图标记32g、附图标记44g1、附图标记44g2和附图标记55g 也可以分别用于指代下栅堆叠组、第一中间栅堆叠组、第二中间栅堆 叠组和上栅堆叠组。

99.在实施例中,术语“下、第一中间、第二中间、和上”用于将栅 堆叠组相互区分,并且可以用其他术语替换。例如,术语“下、第一 中间、第二中间、和上”可以分别用术语“第一、第二、第三、和第 四”替换。

100.类似于上面参考图1至图2b描述的实施例,下栅层32g、第一中 间栅层44g1、第二中间栅层44g2和上栅层58g包括栅焊盘gp,栅焊 盘gp在下栅层32g、第一中间栅层44g1、第二中间栅层44g2和上栅 层58g的端部处并且以阶梯形状布置在第二区sa中。

101.在实施例中,第二结构us还包括覆盖堆叠结构gs

′

的至少一部 分的中间绝缘结构36、48a、48b和62。中间绝缘结构36、48a、48b 和62包括:第一中间绝缘层36,其覆盖下结构ls上的下栅层32g 的栅焊盘gp;第二中间绝缘层48a,其覆盖第一中间绝缘层36上的 第一中间栅层44g1的栅焊盘gp;第三中间绝缘层48b,其覆盖第二 中间绝缘层48a上的第二中间栅层44g2的栅焊盘gp;以及第四中间 绝缘层62,其覆盖第三中间绝缘层48b上的上栅层58g的栅焊盘gp。

102.在实施例中,第二结构us还包括上绝缘结构68、84、90和116, 其包括与上面参考图2a和图2b描述的那些基本上相同的第一上绝缘 层至第四上绝缘层68、84、90和116。

103.在实施例中,上面参考图1描述的贯通区ta包括设置在分别与 下栅层32g、第一中间栅层44g1、第二中间栅层44g2和上栅层58g 基本上相同的高度处的下水平绝缘层32d、第一中间水平绝缘层44d1、 第二中间水平绝缘层44d2和上水平绝缘层58d。

104.在实施例中,半导体器件1’还包括:在第一区mca中至少穿 透堆叠结构gs’的竖直存储结构171;在第二区sa中穿透堆叠结构 gs’的支撑竖直结构181;以及至少穿透堆叠结构gs’的分离结构 287。半导体器件1’还包括外围接触插塞211,其包括第一外围接触 插塞211a、第二外围接触插塞211b和第三外围接触插塞211c。

105.在下文中,将参考图5a描述上面公开的竖直存储结构171和分 离结构287。图5a是图4b的区域“a1”的局部放大图。

106.结合图4a和图4b参考图5a,竖直存储结构171的侧表面包括: 均具有陡峭的坡度的侧表面部171sa、侧表面部171sb1、侧表面部 171sb2、侧表面部171sc和侧表面部171sd;以及位于相邻的侧表面部 171sa、侧表面部171sb1、侧表面部171sb2、侧表面部171sc和侧表面 部171sd之间并且具有相对缓的坡度的侧表面坡度改变部。在竖直存 储结构171的侧表面上,侧表面坡度改变部可以包括:设置在最下栅 层32g_l与最上栅层58g_l之间的高度处的数量为n的多个存储侧表 面坡度改变部171s_1a、171s_1ab和171s_1b;以及设置在比最上栅层 58g_u高的高度处的至少一个上侧表面坡度改变部171s_2。

107.在实施例中,分离结构287的侧表面包括:均具有陡峭的坡度的 侧表面部287sa、侧表面部287sb、侧表面部287sc和侧表面部287sd; 以及位于相邻的侧表面部287sa、侧表面部287sb、侧表面部287sc和 侧表面部287sd之间并且具有相对缓的坡度的侧表面坡度改变部。在 分离结构287的侧表面上,侧表面坡度改变部包括:位于最下栅层 32g_l与最上栅层58g_u之间的高度处的数量为m的多个分离侧表面 坡度改变部287s_1a和287s_1b;以及位于比最上栅层58g_u高的高 度的至少一个上侧表面坡度改变部287s_2。竖直存储结构171的侧表 面的上侧表面坡度改变部171s_2和分离结构287的侧表面的上侧表面 坡度改变部287s_2设置在基本上相同的高度处。

108.在实施例中,分离结构287的侧表面的位于最下栅层32g_l与最 上栅层58g_u之间的高度处的数量为m的多个分离侧表面坡度改变 部287s_1a和287s_1b位于与n个存储侧表面坡度改变部171s_1a、 171s_1ab和171s_1b中的数量为m(m<n)的多个存储侧表面坡度改 变部171s_1ab和171s_1b基本上相同的高度处。例如,n个存储侧表 面坡度改变部171s_1a、171s_1ab和171s_1b中的m个存储侧表面坡 度改变部171s_1ab和171s_1b(其中m<n)位于基本上相同的高度处。 例如,m个分离侧表面坡度改变部287s_1a和287s_1b位于与n个存 储侧表面坡度改变部171s_1a、171s_1ab和171s_1b中位于比设置在 最下部的侧表面坡度改变部171s_1a高的m个存储侧表面坡度改变部 171s_1ab和171s_1b基本上相同的高度处。

109.n和m均是自然数,并且n大于m。例如,n是3或更大的自 然数,并且m是n-1。例如,n可以是3,并且m可以是2。

110.接下来,将参考图5b描述上面公开的外围接触插塞211中的一 个。图5b是图4a的区域“b2a”的局部放大图。

111.结合图4a、图4b和图5a参考图5b,在实施例中,外围接触插 塞211的侧表面包括:均具有陡峭的坡度的侧表面部211sa、侧表面 部211sb1、侧表面部211sb2、侧表面部211sc和侧表面部211sd;以 及设置在相邻的侧表面部211sa、侧表面部211sb1、侧表面部211sb2、 侧表面部211sc和侧表面部211sd之间并且具有相对缓的坡度的侧表 面坡度改变部。在外围接触插塞211的侧表面上,侧表面坡度改变部 包括:位于最下栅层32g_l与最上栅层58g_u之间的高度处的数量为 n的多个外围接触侧表面坡度改变部211s_1a、211s_1ab和211s_b; 以及位于比最上栅层58g_u的高度高的高度处的至少一个上侧表面坡 度改变部211s_2。

112.在实施例中,n个外围接触侧表面坡度改变部211s_1a、211s_1ab 和211s_b位于与上面参考图5a描述的n个存储侧表面坡度改变部 171s_1a、171s_1ab和171s_1b基本上相同的高度处。

113.在实施例中,外围接触插塞211的侧表面的上侧表面坡度改变部 211s_2位于与竖

直存储结构171的侧表面的上侧表面坡度改变部 171s_2基本上相同的高度处。

114.接下来,将参考图6和图7描述根据本发明构思的修改的实施例 的半导体器件。图6是沿图1的线ii-ii’截取的示意性截面图,并且 图7是图6的区域“a2”的局部放大图。在参考图6和图7描述根据 本发明构思的修改的实施例的半导体器件时,将描述上面参考图4b 和图5a描述的分离结构287的修改的示例。

115.参考图6和图7,在实施例中,上面参考图4b和图5a描述的分 离结构287被替换为图6和图7的分离结构387。例如,分离结构387 的侧表面包括:均具有陡峭的坡度的侧表面部387sa、侧表面部387sb 和侧表面部387sc;以及位于相邻的侧表面部387sa、侧表面部387sb 和侧表面部387sc之间并且具有相对缓的坡度的侧表面坡度改变部。 在分离结构387的侧表面上,侧表面坡度改变部包括:位于最下栅层 32g_l与最上栅层58g_u之间的高度处的n-2个分离侧表面坡度改变 部387s_1;以及位于比最上栅层58g_u高的高度处的至少一个上侧表 面坡度改变部387s_2。竖直存储结构171的侧表面的上侧表面坡度改 变部171s_2和分离结构387的侧表面的上侧表面坡度改变部387s_2 位于基本上相同的高度处。

116.如上面参考图5a所述,在实施例中,当位于最下栅层32g_l与 最上栅层58g_u之间的高度处的竖直存储结构171的侧表面包括n个 存储侧表面坡度改变部171s_1a、171s_1ab和171s_1b时,n-2是1或 更大的自然数,并且n是3或更大的自然数。

117.在实施例中,n-2个分离侧表面坡度改变部387s_1位于与n个存 储侧表面坡度改变部171s_1a、171s_1ab和171s_1b中设置在设置在 下部的下存储侧表面坡度改变部171s_1a与设置在上部的上存储侧表 面坡度改变部171s_1b之间的中间存储侧表面坡度改变部171s_ab基 本上相同的高度处。

118.在上面参考图2a和图2b描述的半导体器件1中,在实施例中, 外围电路9和外围电路13设置在堆叠结构gs下方。然而,本发明构 思的实施例不限于此。例如,在其他实施例中,外围电路9和外围电 路13设置在堆叠结构gs上。将参考图8描述外围电路9和外围电路 13设置在堆叠结构gs上的实施例。图8是根据本发明构思的实施例 的半导体器件的修改的示例的示意性截面图。

119.参考图8,在实施例中,半导体器件1”包括第一芯片结构ch1 和接合到第一芯片结构ch1的第二芯片结构ch2。第二芯片结构ch2 包括如上所述的图案化结构23、绝缘层26o和绝缘层26i_2、堆叠结 构gs、中间绝缘结构36、48和62、以及上绝缘结构68、84、90和 116。第二芯片结构ch2还包括与图2a的下绝缘结构21相对应的下 绝缘结构221。第二芯片结构ch2还包括栅接触插塞106,其在阶梯 区sa中穿透栅层32g、栅层44g和栅层58g的栅焊盘gp并且电连接 到栅焊盘gp。第二芯片结构ch2还包括如上所述的图2a的竖直存 储结构71、图2a的支撑竖直结构81、外围接触插塞111、分离结构 (图2b的87)、图2a的上接触插塞120、图2a的位线接触插塞119、 图2a的位线123、以及图2a的外围互连124。

120.在实施例中,第二芯片结构ch2还包括设置在栅接触插塞106 上的栅连接插塞121、以及设置在栅连接插塞121上的栅互连126。

121.在实施例中,第二芯片结构ch2还包括:第一接合图案155;以 及围绕第一接合图案155的侧表面的第一接合绝缘层150。第一接合 图案155电连接到位线123、栅互连126和外围互连124。第一接合图 案155包括金属(例如,铜)。

122.在实施例中,第一芯片结构ch1包括与如上所述的下结构ls的 那些类似的组件。

例如,第一芯片结构ch1包括:半导体衬底305; 半导体衬底305下方的外围电路311和外围电路313;电连接到外围 电路311和外围电路313并且接合到第一接合图案155的第二接合图 案315;以及接合到第一接合绝缘层150的第二接合绝缘层321。

123.在实施例中,第一芯片结构ch1还包括:设置在半导体衬底305 上的绝缘层360;设置在绝缘层360上的输入/输出焊盘380;以及输 入/输出连接图案370,其穿透半导体衬底305和绝缘层360并且将输 入/输出焊盘380电连接到外围电路311和外围电路313。

124.接下来,将参考图9a、图9b、图10a、图10b、图11a和图11b 描述根据本发明构思的实施例的形成半导体器件的方法的示例。图9a 和图9b是根据本发明构思的实施例的形成半导体器件的方法的流程 图;并且图10a、图10b、图11a和图11b是根据本发明构思的实施 例的形成半导体器件的方法的截面图。图10a和图11a是沿图1的线 i-i’截取的示意性截面图,并且图10b和图11b是沿图1的线ii-ii

’ꢀ

截取的示意性截面图。

125.参考图1、图9a、图10a和图10b,在实施例中,在操作s10 中形成下结构ls。下结构ls可以被称为第一结构。所形成的下结构 ls包括:半导体衬底5;器件隔离层7s,其限定半导体衬底5上的外 围有源区7a;形成在半导体衬底5上的外围电路9和外围电路13;外 围焊盘15,其电连接到外围电路9和外围电路13;以及下绝缘结构 21,其覆盖半导体衬底5上的外围电路9和外围电路13以及外围焊盘 15。外围电路9和外围电路13包括:电路元件9,例如包括外围栅极 9b和外围源极/漏极9a的晶体管;以及电路互连13,其电连接到电路 元件9。外围焊盘15电连接到电路互连13。

126.在实施例中,外围焊盘15包括第一外围焊盘至第三外围焊盘15a、 15b和15c。在实施例中,每个外围焊盘15包括导电材料(例如,诸 如钨之类的金属)。

127.在实施例中,下结构ls还包括:形成在每个外围焊盘15上的封 盖层17;以及形成在封盖层17上的蚀刻停止层19。在实施例中,封 盖层17由硅层形成,并且蚀刻停止层19由绝缘材料(例如,氧化硅 或氮化硅)形成。

128.在实施例中,形成下结构ls还包括:在下绝缘结构21上形成图 案化结构23以及绝缘层26i_1、绝缘层26i_2和绝缘层26o。绝缘层 26i_1、绝缘层26i_2和绝缘层26o包括:设置在图案化结构23外部 的外绝缘层26o;穿透图案化结构23的第一内绝缘层26i_1;以及穿 透图案化结构23的第二内绝缘层26i_2。

129.在实施例中,图案化结构23包括顺序堆叠的多个图案化层。例 如,图案化结构23包括:下图案化层23a;彼此间隔开并且设置在下 图案化层23a上的中间图案化层23b;以及设置在中间图案化层23b 上的上图案化层23c。下图案化层23a、中间图案化层23b和上图案化 层23c中的至少一个是硅层。例如,下图案化层23a和上图案化层23c 均是硅层(例如,具有n型导电性的硅层),并且中间图案化层23b 是与硅层不同的材料层(例如,氧化硅层和/或氮化硅层)。

130.在实施例中,在操作s15中形成第一模塑组30m。形成第一模塑 组30m包括:形成交替且重复堆叠的第一层间绝缘层32a和第一牺牲 栅层32b;图案化第一层间绝缘层32a和第一牺牲栅层32b以形成阶 梯形状;以及在阶梯形状的第一牺牲栅层32b的部分上形成焊盘层34。 焊盘层34可以形成在阶梯形状的第一牺牲栅层32b的端部上。第一层 间绝缘层32a和第一牺牲栅层32b中的最下层和最上层是第一层间绝 缘层。第一层间绝缘层32a由氧化硅形成。第一牺牲栅层32b和焊盘 层34由氮化硅或多晶硅形成。

131.在实施例中,第一中间绝缘层36形成在下结构ls上,并且覆盖 阶梯形状的第一牺牲栅层32b的阶梯形状部分和焊盘层34。

132.在实施例中,在操作s20中形成下竖直牺牲结构39a、39b、39c 和39d。下竖直牺牲结构39a、39b、39c和39d分别形成在将形成上 面参考图2a和图2b描述的竖直存储结构71、支撑竖直结构81、栅 接触插塞106和外围接触插塞111的区域中。

133.参考图1、图9a、图9b、图11a和图11b,在实施例中,在操 作s25中形成第二模塑组42m。形成第二模塑组42m包括:形成交替 且重复堆叠的第二层间绝缘层44a和第二牺牲栅层44b;图案化第二 层间绝缘层44a和第二牺牲栅层44b以形成阶梯形状;以及在阶梯形 状的第二牺牲栅层44b的部分上形成焊盘层46。焊盘层46可以形成 在阶梯形状的第二牺牲栅层44b的端部上。第二层间绝缘层44a和第 二牺牲栅层44b中的最下层和最上层是第二层间绝缘层。第二层间绝 缘层44a由氧化硅形成。第二牺牲栅层44b和焊盘层46由氮化硅或多 晶硅形成。

134.在实施例中,第二中间绝缘层48形成在第一中间绝缘层36上, 并且覆盖阶梯形状的第二牺牲栅层44b的阶梯形状部分和焊盘层46。

135.在实施例中,在操作s30中,形成分别与下竖直牺牲结构39a、 39b、39c和39d接触的中间竖直牺牲结构51a、51b、51c和51d,并 且形成穿透第一模塑组30m和第二模塑组42m的下牺牲分离结构52。 下牺牲分离结构52与下图案化层23a间隔开并且与上图案化层23c 接触。下牺牲分离结构52与中间图案化层23b间隔开。

136.在实施例中,在操作s35中形成第三模塑组56m。形成第三模塑 组56m包括:形成交替且重复堆叠的第三层间绝缘层58a和第三牺牲 栅层58b;图案化第三层间绝缘层58a和第三牺牲栅层58b以形成阶 梯形状;以及在阶梯形状的第三牺牲栅层58b的部分上形成焊盘层60。 焊盘层60可以形成在阶梯形状的第三牺牲栅层58b的端部上。第三层 间绝缘层58a和第三牺牲栅层58b的最下层和最上层是第三层间绝缘 层。第三层间绝缘层58a由氧化硅形成。第三牺牲栅层58b和焊盘层 60由氮化硅或多晶硅形成。

137.在实施例中,第三中间绝缘层62形成在第二中间绝缘层48上, 并且覆盖阶梯形状的第三牺牲栅层58b的阶梯形状部分和焊盘层60。

138.在实施例中,在操作s40中,形成分别与中间竖直牺牲结构51a、 51b、51c和51d接触的上竖直牺牲结构64a、64b、64c和64d,并且 形成穿透第三模塑组56m以与下牺牲分离结构52接触的上牺牲分离 结构65。

139.在实施例中,下竖直牺牲结构39a、39b、39c和39d、中间竖直 牺牲结构51a、51b、51c和51d、以及上竖直牺牲结构64a、64b、64c 和64d构成竖直牺牲结构66a、66b、66c和66d,并且下牺牲分离结 构52和上牺牲分离结构65构成牺牲分离结构67。

140.在实施例中,现在参考图9b,在操作s45中,竖直牺牲结构66a、 66b、66c和66d分别形成在将形成竖直存储结构71、支撑竖直结构 81、栅接触插塞106和外围接触插塞111的区域中。例如,竖直牺牲 结构66a、66b、66c和66d包括:用于形成竖直存储结构71的存储牺 牲竖直结构66a;用于形成支撑竖直结构81的支撑牺牲竖直结构66b; 用于形成外围接触插塞111的外围接触竖直牺牲结构66c;以及用于 形成栅接触插塞106的栅接触牺牲竖直结构66d。

141.参考图1、图9b、图11a、图11b、图2a和图2b,在实施例中, 在竖直牺牲结构66a、

66b、66c和66d、第三模塑组56m、以及第三 中间绝缘层62上形成第一上绝缘层68。

142.在实施例中,形成穿透第一上绝缘层68的孔,其分别暴露存储 牺牲竖直结构66a和支撑牺牲竖直结构66b,并且去除暴露的存储牺 牲竖直结构66a和暴露的支撑牺牲竖直结构66b以形成存储竖直孔和 支撑竖直孔,并且分别在存储竖直孔和支撑竖直孔中形成竖直存储结 构71和支撑竖直结构81。

143.在实施例中,在第一上绝缘层68上形成第二上绝缘层84。在操 作s50中形成初步栅接触插塞。形成初步栅接触插塞包括:形成暴露 栅接触牺牲竖直结构66d的孔,其顺序穿过第二上绝缘层84和第一上 绝缘层68;去除由孔所暴露的栅接触牺牲竖直结构66d以形成初步栅 接触孔;部分地蚀刻由初步栅接触孔所暴露的牺牲栅层32b、牺牲栅 层44b和牺牲栅层58b以及焊盘层34、焊盘层56和焊盘层60以形成 空间;形成填充通过部分地蚀刻不与焊盘层34、焊盘层56和焊盘层 60接触的那些牺牲栅层32b、牺牲栅层44b和牺牲栅层58b而形成的 空间的缓冲绝缘层103;以及形成部分地填充通过部分地蚀刻焊盘层 34、焊盘层56和焊盘层60以及与焊盘层34、焊盘层56和焊盘层60 接触的那些牺牲栅层32b、牺牲栅层44b和牺牲栅层58b而形成的空 间的材料层。

144.在实施例中,在操作s55中形成隔离沟槽。形成隔离沟槽包括: 形成顺序穿透第一上绝缘层68和第二上绝缘层84的开口,其暴露牺 牲分离结构67;以及去除暴露的牺牲分离结构67。

145.在实施例中,在隔离沟槽的侧壁上形成牺牲间隔物以暴露在第一 区mca中的中间图案化层23b的下部处的中间图案化层,去除在第 一区mca的下部处的暴露的中间图案化层,在通过去除暴露的中间 图案化层形成的空间中形成第一中间图案化层23b1,以及去除牺牲间 隔物。在第二区sa的下部处的中间图案化层23b的中间图案化层保 留并且形成第二中间图案化层23b2。

146.在实施例中,在操作s60中,第一模塑组至第三模塑组30m、42m 和56m中的牺牲栅层32b、牺牲栅层44b和牺牲栅层58b被栅层32g、 栅层44g和栅层58g替换。例如,蚀刻由隔离沟槽暴露的牺牲栅层32b、 牺牲栅层44b和牺牲栅层58b以形成空隙,并且在空隙中形成栅层32g、 栅层44g和栅层58g。

147.在实施例中,在蚀刻牺牲栅层32b、牺牲栅层44b和牺牲栅层58b 以形成空隙的工艺期间,竖直存储结构71和支撑竖直结构81用作防 止层间绝缘层32a、层间绝缘层44a和层间绝缘层58a弯曲或变形的 支撑。

148.在实施例中,在贯通区ta中,牺牲栅层32b、牺牲栅层44b和 牺牲栅层58b的一部分保留,以形成水平绝缘层32d、水平绝缘层44d 和水平绝缘层58d。

149.在实施例中,在第二上绝缘层84上形成第三上绝缘层90。在操 作s70中形成栅接触插塞106和外围接触插塞111。形成栅接触插塞 106和外围接触插塞111包括:形成穿透第三上绝缘层90并且暴露初 步栅接触插塞的孔;形成穿透第一上绝缘层至第三上绝缘层68、84 和90并且暴露外围接触竖直牺牲结构66c的孔;去除暴露的初步栅接 触插塞和暴露的外围接触竖直牺牲结构66c,以分别形成栅接触孔和 外围接触孔;以及分别用导电材料填充栅接触孔和外围接触孔。缓冲 绝缘层103保留,同时去除暴露的初步栅接触插塞。

150.在实施例中,在第三上绝缘层90上形成第四上绝缘层116。在操 作s75中执行互连工艺。执行互连工艺包括:形成穿透第一上绝缘层 至第四上绝缘层68、84、90和116并且电

连接到竖直存储结构71的 位线接触插塞119;形成穿透第四上绝缘层116并且电连接到外围接 触插塞111的上接触插塞120;以及形成位线123和外围互连124。

151.图12示意性地示出了包括根据本发明构思的实施例的半导体器 件的数据存储系统。

152.参考图12,根据本发明构思的实施例的数据存储系统1000包括 半导体器件1100和电连接到半导体器件1100的控制器1200。数据 存储系统1000可以是包括半导体器件1100的存储设备或包括该存储 设备的电子设备。例如,数据存储系统1000可以是包括半导体器件 1100的固态驱动器(ssd)设备、通用串行总线(usb)、计算系统、 医疗设备或通信设备。

153.在实施例中,数据存储系统1000是存储数据的电子系统。

154.在实施例中,半导体器件1100可以是根据上面参考图1至图8 描述的实施例中的任何一个的半导体器件,或者可以由上面参考图9a 至图11b描述的用于形成半导体器件的方法制造。半导体器件1100 包括第一结构1100f和第一结构1100f上的第二结构1100s。

155.在实施例中,第一结构1100f是包括解码器电路1110、页缓冲器 1120和逻辑电路1130的外围电路结构。例如,第一结构1100f包括 上面描述的图2a的外围电路9。

156.在实施例中,第二结构1100s是存储单元结构,其包括位线bl、 公共源极线csl、字线wl、第一栅极上线ul1和第二栅极上线ul2、 第一栅极下线ll1和第二栅极下线ll2、以及位线bl和公共源极线 csl之间的存储单元串cstr。

157.在实施例中,上述图案化结构23包括具有n型导电性的硅层, 并且n型导电性硅层是公共源极线csl。

158.在实施例中,在第二结构1100s中,每个存储单元串cstr包括 与公共源极线csl相邻的下晶体管lt1和lt2、与位线bl相邻的上 晶体管ut1和ut2、以及设置在下晶体管lt1和lt2与上晶体管ut1 和ut2之间的多个存储单元晶体管mct。下晶体管lt1和lt2的数 量以及上晶体管ut1和ut2的数量可以根据实施例进行不同地修改。

159.在实施例中,上晶体管ut1和ut2均包括串选择晶体管,并且 下晶体管lt1和lt2均包括接地选择晶体管。栅极下线ll1和栅极下 线ll2分别是下晶体管lt1的栅电极和下晶体管lt2的栅电极。字线 wl是存储单元晶体管mct的栅电极,并且栅极上线ul1和栅极上 线ul2分别是上晶体管ut1的栅电极和上晶体管ut2的栅电极。

160.在实施例中,上述栅层32g、栅层44g和栅层58g构成栅极下线 ll1和栅极下线ll2、字线wl、以及栅极上线ul1和栅极上线ul2。

161.在实施例中,下晶体管lt1和下晶体管lt2均包括串联连接的下 擦除控制晶体管lt1和接地选择晶体管lt2。上晶体管ut1和上晶体 管ut2均包括串联连接的串选择晶体管ut1和上擦除控制晶体管 ut2。下擦除控制晶体管lt1和上擦除控制晶体管ut1中的至少一个 用于擦除操作,以使用栅极感应漏极泄露(gidl)现象删除存储在存 储单元晶体管mct中的数据。

162.在实施例中,公共源极线csl、第一栅极下线ll1和第二栅极下 线ll2、字线wl、以及第一栅极上线ul1和第二栅极上线ul2通过 从第一结构1100f延伸到第二结构1100s的第一连接互连1115与解码 器电路1110电连接。

163.在实施例中,位线bl通过从第一结构1100f延伸到第二结构 1100s的第二连接互

连1125电连接到页缓冲器1120。位线bl是上述 位线123。

164.在实施例中,在第一结构1100f中,解码器电路1110和页缓冲 器1120对多个存储单元晶体管mct中的至少一个选择的存储单元晶 体管执行控制操作。解码器电路1110和页缓冲器1120由逻辑电路 1130控制。半导体器件1000通过电连接到逻辑电路1130的输入/输 出焊盘1101与控制器1200通信。输入/输出焊盘1101通过输入/输出 连接互连1135电连接到逻辑电路1130,输入/输出连接互连1135从 第一结构1100f延伸到第二结构1100s。

165.在实施例中,控制器1200包括处理器1210、nand控制器1220 和主机接口1230。在一些实施例中,数据存储系统1000包括多个半 导体器件1100。在这种情况下,控制器1200控制多个半导体器件1000。

166.在实施例中,处理器1210控制数据存储系统1000和控制器1200 的整体操作。处理器1210根据预加载的固件操作,并且通过控制 nand控制器1220来访问半导体器件1100。nand控制器1220包 括nand接口1221,其处理与半导体器件1100的通信。通过nand 接口1221,可以发送用于控制半导体器件1100的控制命令、要被写 入半导体器件1100的存储单元晶体管mct的数据、以及要从存储单 元晶体管mct读取的数据。主机接口1230提供数据存储系统1000 和外部主机之间的通信功能。当通过主机接口1230从外部主机接收 到控制命令时,处理器1210响应于控制命令而控制半导体器件1100。

167.图13是包括根据本发明构思的实施例的半导体器件的数据存储 系统的透视图。

168.参考图13,根据本发明构思的实施例的数据存储系统2000包括 主基板2001、安装在主基板2001上的控制器2002、一个或多个半导 体封装2003、以及dram 2004。半导体封装2003和dram 2004通 过形成在主基板2001上的互连图案2005连接到控制器2002。

169.在实施例中,主基板2001包括连接器2006,其包括耦合到外部 主机的多个引脚。连接器2006中的多个引脚的数量和布置可以根据 数据存储系统2000和外部主机之间的通信接口变化。在实施例中, 数据存储系统2000可以根据以下各种接口中的任何一个与外部主机 通信:例如通用串行总线(usb)、外围组件互连快速(pci-express)、 串行高级技术附件(sata)、以及用于通用闪存(ufs)的m-phy。 在实施例中,数据存储系统2000通过由外部主机通过连接器2006供 应的电力操作。数据存储系统2000还包括电力管理集成电路(pmic), 其向控制器2002和半导体封装2003分配从外部主机接收的电力。

170.在实施例中,控制器2002可以将数据写入到半导体封装2003 中或从半导体封装2003读取数据,并且可以提高数据存储系统2000 的操作速度。

171.在实施例中,dram 2004是减轻用作数据存储空间的半导体封 装2003与外部主机之间的速度差异的缓冲存储器。数据存储系统 2000中的dram 2004还作为高速缓冲存储器操作,并且在半导体封 装2003的控制操作中提供用于暂时存储数据的空间。当数据存储系 统2000中包括dram 2004时,除了控制半导体封装2003的nand 控制器之外,控制器2002还包括控制dram 2004的dram控制器。

172.在实施例中,半导体封装2003包括彼此间隔开的第一半导体封 装2003a和第二半导体封装2003b。第一半导体封装2003a和第二半 导体封装2003b中的每一个是包括多个半导体芯片2200的半导体封 装。每个半导体芯片2200包括根据上面参考图1至图3描述的实施 例中的任何一个的半导体器件或由上面参考图9a至图11b描述的形 成半导体器件的方法制造的半导体器件。

173.在实施例中,第一半导体封装2003a和第二半导体封装2003b 中的每一个包括:封装基板2100;封装基板2100上的半导体芯片2200; 设置在每个半导体芯片2200的下表面上的粘合层2300;连接结构 2400,其将半导体芯片2200电连接到封装基板2100;以及模塑层2500, 其覆盖封装基板2100上的半导体芯片2200和连接结构2400。

174.在实施例中,封装基板2100是包括封装上焊盘2130的印刷电路 板。每个半导体芯片2200包括输入/输出焊盘2210。

175.在实施例中,连接结构2400是将输入/输出焊盘2210与封装上 焊盘2130彼此电连接的接合线。因此,在第一半导体封装2003a和 第二半导体封装2003b中的每一个中,半导体芯片2200通过接合线 彼此电连接,并且可以电连接到封装基板2100的封装上焊盘2130。 备选地,根据实施例,在第一半导体封装2003a和第二半导体封装 2003b中的每一个中,半导体芯片2200通过包括硅通孔(tsv)的连 接结构而不是接合线类型的连接结构2400彼此电连接。

176.在实施例中,控制器2002和半导体芯片2200被包括在一个封装 中。例如,控制器2002和半导体芯片2200安装在与主基板2001不 同的单独的插入基板上,并且控制器2002和半导体芯片2200通过在 插入基板上形成的布线彼此连接。

177.图14是根据本发明构思的示例实施例的半导体封装的截面图。 图14示出了图13的半导体封装2003,并且概念性地示出了图13的 半导体封装2003沿着线iii-iii’截取的区域。

178.参考图14,在实施例中,半导体封装2003的封装基板2100是印 刷电路板。封装基板2100包括:封装基板主体部2120;设置在封装 基板主体部2120的上表面上的封装上焊盘2130;设置在封装基板主 体部2120的下表面上或通过下表面暴露的下焊盘2125;以及内互连 2135,其在封装基板主体部2120中将上焊盘2130与下焊盘2125彼此 电连接。上焊盘2130电连接到连接结构2400。通过导电连接部2800 将下焊盘2125连接到数据存储系统2000的主基板2010的互连图案 2005。

179.在实施例中,每个半导体芯片2200包括:半导体衬底3010;以 及顺序堆叠在半导体衬底3010上的第一结构3100和第二结构3200。 第一结构3100包括:包括外围互连3110的外围电路区。第二结构3200 包括:公共源极线3205;设置在公共源极线3205上的栅堆叠结构3210; 穿透栅堆叠结构3210的存储沟道结构3220和隔离结构3230;电连接 到存储沟道结构3220的位线3240;以及电连接到栅堆叠结构3210的 字线wl的图2a中的栅接触插塞106。第一结构3100包括图12的 第一结构1000f,并且第二结构3200包括图12的第二结构1000s。

180.在实施例中,每个半导体芯片2200包括:贯通互连3245,其电 连接到第一结构3100的外围互连3110并且延伸到第二结构3200中。 贯通互连3245穿透栅堆叠结构3210并且还设置在栅堆叠结构3210 外部。

181.在实施例中,每个半导体芯片2200还包括:输入/输出连接互连 3265,其电连接到第一结构3100的外围互连3110并且延伸到第二结 构中;以及输入/输入焊盘2210,其电连接到输入/输出连接互连3265。

182.在图14中,在实施例中,由附图标记1指示的半导体器件1的 放大部分示出了图14的半导体芯片2200可以被修改为包括图2a所 示的截面结构。因此,每个半导体芯片2200包

括根据上面参考图1 至图8描述的实施例中的任何一个的半导体器件1或由上面参考图9a 至图9b描述的形成半导体器件的方法制造的半导体器件1。

183.如上所述,根据本发明构思的实施例,因为栅层可以沿竖直方向 堆叠,所以可以增加半导体器件的集成度。因此,可以提供具有增加 的集成度的半导体器件和包括该半导体器件的数据存储系统。

184.根据本发明构思的实施例,提供了同时执行形成竖直存储结构、 支撑竖直结构、栅接触插塞、外围接触插塞和分离结构的半导体工艺 中的一些半导体工艺而同时增加沿竖直方向堆叠的栅层的数量的方法。 因此,生产率可以增加,并且半导体器件的集成度增加。

185.虽然上面已经示出和描述了实施例,但将对本领域技术人员显而 易见的是,在不脱离由所附权利要求限定的本发明构思的范围的情况 下,可以做出修改和变化。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1