碳化硅半导体装置的制造方法与流程

1.本发明涉及一种碳化硅半导体装置的制造方法。

背景技术:

2.以往,在评价将碳化硅(sic)作为半导体材料的碳化硅半导体装置(半导体芯片)的可靠性时,通过利用结晶缺陷检查装置(例如lasertec株式会社制的sic晶片缺陷检查/审查装置sica88)来检测半导体晶片(sic晶片)的表面和内部的结晶缺陷,从而筛选出从半导体晶片切断而单片化的多个半导体芯片中的不合格芯片。由结晶缺陷检查装置检测出的包含结晶缺陷的半导体芯片与电特性试验的结果无关,或者不进行电特性试验,全部无例外地作为不合格芯片。

3.对以往的碳化硅半导体装置的制造方法进行说明。图11是示出以往的碳化硅半导体装置的制造方法的概要的流程图。首先,准备将碳化硅作为半导体材料的半导体晶片(sic晶片)(步骤s101)。半导体晶片是在由碳化硅形成的起始晶片上使外延层外延生长而成的外延晶片。接着,在半导体晶片的外延层表面(主面)形成用于表示半导体晶片的结晶缺陷的位置(与晶片表面平行的方向的坐标)和/或制造工艺的校准的标记(步骤s102)。

4.接着,利用结晶缺陷检查装置来检测半导体晶片的外延层的结晶缺陷,基于在步骤s102的处理中形成的标记来获取该结晶缺陷的位置信息等(步骤s103)。在步骤s103的处理中,检测出在外延层的外延生长中产生的、因异物混入和/或碳(c)夹杂物而引起的塌陷和大凹坑、因多型(多晶型)夹杂物而引起的三角缺陷、以及因贯通螺旋位错(tsd:threading screw dislocation)而引起的侧面型缺陷和胡萝卜型缺陷。

5.接着,进行用于在半导体晶片的各芯片区(成为半导体芯片的区域)形成预定的元件结构的各种工艺(步骤s104)。接着,切断(切割)半导体晶片而使半导体晶片的各芯片区单片化为一个个半导体芯片(sic芯片)(步骤s105)。接着,基于在步骤s103的处理中获取的位置信息,将完全不包含在步骤s103的处理中检测出的结晶缺陷的半导体芯片筛选为合格品候选(合格芯片)(步骤s106)。即使半导体芯片包含一个在步骤s103的处理中检测出的结晶缺陷,也会作为不合格芯片而被去除。

6.接着,针对在步骤s106的处理中作为合格品候选的各半导体芯片,分别进行预定的通电试验来检查电特性(步骤s107),基于步骤s107的结果来判定是否满足预先获得的合格品规格(步骤s108)。合格品规格是能够确保碳化硅半导体装置的预定耐量和预定的可靠性的各特性的极限值,并且是预先获取的。其后,基于步骤s108的结果,将满足合格品规格的半导体芯片筛选为合格品(合格芯片)(步骤s109),结束碳化硅半导体装置的评价。

7.作为以往的碳化硅半导体装置的制造方法而提出了如下方法:在外观检查中,在芯片的尺寸比相机的视野尺寸更大,将芯片分割为多个而进行拍摄的情况下,为了防止产生疑似缺陷,基于校准图案的位置,从拍摄图像切出检查图像进行外观检查(例如,参照下述专利文献1)。另外,作为以往的半导体晶片而提出了一种半导体晶片,通过将正交的第一划线和第二划线中的第一划线配置在与基板结晶的裂开方向平行的方向上,并且将辅助图

案集中配置在与隐形切割的激光照射区域重叠的位置,从而减少崩边和/或裂纹的产生(例如,参照下述专利文献2。)。

8.现有技术文献

9.专利文献

10.专利文献1:国际公开第2018/029786号

11.专利文献2:日本特开2016-134427号公报

技术实现要素:

12.技术问题

13.图12是示出以往的半导体晶片的俯视图。在半导体晶片150设置有划线161,该划线161表示切断半导体晶片150而使半导体芯片单体化时的切断位置。图13是示出以往的半导体晶片的划线的俯视图。图13是图12的部分a的放大图。

14.图14是示出以往的半导体晶片的划线内的标记的俯视图。图14是图13的部分b的放大图。在半导体晶片150中设置有标记162,该标记162表示结晶缺陷的位置和/或制造工艺的校准。这些标记162设置在划线161内。

15.在结晶缺陷检查装置检测出结晶缺陷时,结晶缺陷检查装置被设定为识别划线161的位置而不进行该处的检查。图15是示出以往的半导体晶片的划线与结晶缺陷检查装置所识别的划线的俯视图。然而,如图15所示,设置于半导体晶片150的划线161与结晶缺陷检查装置所识别的划线161a不能够完全一致而产生偏离。

16.图16是将以往的半导体晶片的划线内的标记识别为缺陷的情况下的俯视图。若产生偏离,则由于标记162的标记端部分163a的形状与被称为边缘线的结晶线状的缺陷类似,所以有时结晶缺陷检查装置将标记162的标记端部分163a错误地误识别为结晶缺陷,该边缘线沿着与半导体晶片150的定向平面平行的方向延伸。

17.由此,在上述以往的碳化硅半导体装置的制造方法中,由于该误识别,本来为合格品的芯片被判定为不合格品,并且作为不合格芯片而被去除。因此,在步骤s106的处理中作为不合格芯片而被去除的半导体芯片中,包括具有能够作为合格品而使用的电特性的半导体芯片。由于如此地将能够作为合格品使用的半导体芯片作为不合格芯片而去除,所以合格品率降低而导致芯片成本的上升。

18.为了解决上述现有技术的课题,本发明的目的在于提供一种能够提高合格品率的碳化硅半导体装置的制造方法。

19.技术方案

20.为了解决上述课题并实现本发明的目的,本发明的碳化硅半导体装置的制造方法具有如下特征。首先,进行形成半导体晶片的第一工序,该半导体晶片是在由碳化硅构成的起始基板上使外延层外延生长而成的半导体晶片。接着,进行在设置于所述半导体晶片的划线中形成标记的第二工序。接着,进行第三工序,通过结晶缺陷检查装置来检查所述外延层而检测所述外延层的结晶缺陷。接着,进行第四工序,在所述半导体晶片形成预定的元件结构。接着,在所述第四工序之后,进行切割所述半导体晶片而使其单片化为半导体芯片的第五工序。接着,进行将在所述第三工序中没有检测出所述结晶缺陷的所述半导体芯片筛选为合格品候选的第六工序。将所述结晶缺陷检查装置所识别的所述划线的端与设置在所

述半导体晶片的所述划线没有偏离的情况下的所述标记的端之间的距离设为10μm以上且25μm以下

21.另外,本发明的碳化硅半导体装置的制造方法在上述发明的基础上,其特征在于,使所述结晶缺陷检查装置所识别的所述划线的宽度比设置于所述半导体晶片的所述划线的宽度大。

22.另外,本发明的碳化硅半导体装置的制造方法在上述发明的基础上,其特征在于,所述结晶缺陷检查装置所识别的所述划线的端位于所述半导体芯片的沟道截止部。

23.另外,本发明的碳化硅半导体装置的制造方法在上述发明的基础上,其特征在于,所述结晶缺陷检查装置所识别的所述划线的宽度与设置于所述半导体晶片的所述划线的宽度相同。

24.另外,本发明的碳化硅半导体装置的制造方法在上述发明的基础上,其特征在于,所述划线沿《11-20》方向与《1-100》方向被设置为格子状,将所述结晶缺陷检查装置所识别的所述划线中的所述《11-20》方向的划线的端与设置在所述半导体晶片的所述划线没有偏离的情况下的所述标记的端之间的距离设为10μm以上且25μm以下。

25.为了解决上述课题并实现本发明的目的,本发明的碳化硅半导体装置的制造方法具有如下特征。首先,进行形成半导体晶片的第一工序,该半导体晶片是在由碳化硅构成的起始基板上使外延层外延生长而成的半导体晶片。接着,进行在设置于所述半导体晶片的划线中形成标记的第二工序。接着,进行第三工序,通过结晶缺陷检查装置来检查所述外延层而检测所述外延层的结晶缺陷。接着,进行在所述半导体晶片形成预定的元件结构的第四工序。接着,在所述第四工序之后,进行切割所述半导体晶片而使其单片化为半导体芯片的第五工序。接着,进行第六工序,将在所述第三工序中没有检测出所述结晶缺陷的所述半导体芯片筛选为合格品候选。所述划线沿《11-20》方向与《1-100》方向被设置为格子状,在第二工序中,将所述标记仅设置于所述《1-100》方向的划线。

26.根据上述发明,将结晶缺陷检查装置所识别的划线的端与设置在所述半导体晶片的划线没有偏离的情况下的所述标记的端之间的距离设为10μm以上且25μm以下。例如,使结晶缺陷检查装置所识别的划线的宽度比设置于半导体晶片的划线的宽度宽。例如,使标记的大小比设置于半导体晶片的划线的宽度小。另外,使标记仅存在于《1-100》方向的划线上、或者使所述标记存在于《1-100》方向的划线上的比率增多。由此,即使结晶缺陷检查装置所识别的划线与设置于半导体晶片的划线偏离,也没有结晶缺陷检查装置将标记误识别为结晶缺陷而将检测出该结晶缺陷的半导体芯片作为不合格芯片而被去除的情况。如此,能够使以往因过度检测而成为不合格的半导体芯片变为合格品,因此能够提高合格品率并且伴随于此降低芯片成本。

27.技术效果

28.根据本发明的碳化硅半导体装置的制造方法,发挥了能够提高合格品率,并且能够降低芯片成本这一效果。

附图说明

29.图1是示出从正面侧观察通过实施方式一的碳化硅半导体装置的制造方法而得的半导体晶片的状态的俯视图。

30.图2是示出从正面侧观察从图1的半导体晶片切断而得的半导体芯片的布局的俯视图。

31.图3是示出实施方式一的碳化硅半导体装置的结构的截面图。

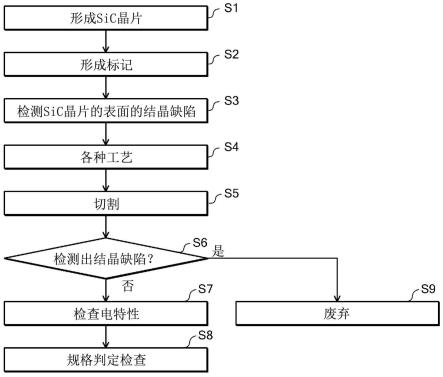

32.图4是示出实施方式一的碳化硅半导体装置的制造方法的概要的流程图

33.图5是示出实施方式一的半导体晶片的划线与结晶缺陷检查装置所识别的划线的俯视图。

34.图6是示出实施方式一的半导体晶片的划线内的标记的俯视图。

35.图7是示出实施方式一的半导体晶片的划线内的标记的位置的俯视图。

36.图8是示出实施方式一的半导体晶片的划线内的标记和线状的结晶缺陷的俯视图。

37.图9是示出实施方式二的半导体晶片内的标记的位置的俯视图(其一)。

38.图10是示出实施方式二的半导体晶片内的标记的位置的俯视图(其二)。

39.图11是示出以往的碳化硅半导体装置的制造方法的概要的流程图。

40.图12是示出以往的半导体晶片的俯视图。

41.图13是示出以往的半导体晶片的划线的俯视图。

42.图14是示出以往的半导体晶片的划线内的标记的俯视图。

43.图15是示出以往的半导体晶片的划线与结晶缺陷检查装置所识别的划线的俯视图。

44.图16是将以往的半导体晶片的划线内的标记识别为缺陷的情况下的俯视图。

45.符号说明

46.1n

+

型漏区

47.2an型缓冲区

48.2bn-型漂移区

49.3n型电流扩散区

50.4p型基区

51.5n

+

型源区

52.6p

++

型接触区

53.7沟槽

54.8栅极绝缘膜

55.9栅电极

56.10碳化硅半导体装置

57.11层间绝缘膜

58.12阻挡金属

59.13欧姆电极

60.14正面电极

61.15背面电极

62.21、22p

+

型区

63.30半导体芯片

64.31、55n

+

型起始基板

65.32 n型外延层

66.33 n-型外延层

67.34 p型外延层

68.35 外延层

69.41 有源区

70.42 边缘终端区

71.43 沟道截止部

72.50、150 半导体晶片

73.51 半导体晶片的芯片区

74.53 半导体晶片的无效区

75.54 定向平面

76.61、161 划线

77.61a、61b、161a 结晶缺陷检查装置所识别的划线

78.62、62a、162 标记

79.63a、63b、163a 标记端部分

80.64 线状的结晶缺陷

具体实施方式

81.以下,参照附图,对本发明的碳化硅半导体装置的制造方法的优选实施方式进行详细说明。在本说明书和附图中,前缀有n或p的层或区域分别表示电子或空穴为多数载流子的层或区域。另外,标记于n或p的+和-分别表示杂质浓度比未标记+和-的层或区域的杂质浓度高和低。包含+和-的n或p的标记相同的情况表示接近的浓度,浓度不限于同等。应予说明,在以下实施方式的说明和附图中,对同样的构成标记相同的符号,并省略重复的说明。另外,在本说明书中,在密勒指数的标记中,

“‑”

表示跟随其后的指数的横杠(

バー

,bar),且通过在指数前标记

“‑”

来表示负的指数。而且,考虑制造中的偏差,相同或同等的记载可以包含到5%以内。

82.(实施方式一)

83.实施方式一的碳化硅半导体装置的制造方法适合于例如肖特基势垒二极管(sbd:schottky barrier diode)、mosfet(metal oxide semiconductor field effect transistor:具备由金属-氧化膜-半导体这三层结构构成的绝缘栅的mos型场效应晶体管),但是也可以适用于pin(p-intrinsic-n)二极管、igbt(insulated gate bipolar transistor:绝缘栅型双极晶体管)。

84.在此,针对使用碳化硅(sic)制作(制造)而成的碳化硅半导体装置,示出沟槽栅结构的n沟道型的纵型mosfet。图1是示出从正面侧观察通过实施方式的碳化硅半导体装置的制造方法而得的半导体晶片的状态的俯视图。图2是示出从正面侧观察从图1的半导体晶片切断而得的半导体芯片的布局的俯视图。在图2中示出图1的半导体晶片50的一个芯片区51的切断后的状态。图3是示出实施方式一的碳化硅半导体装置的结构的截面图。

85.半导体晶片50是在由碳化硅构成的n

+

型起始晶片(参照图3,在切割后成为图3的n

+

型起始基板31的部分)上使外延层(参照图3,在切割后成为图3的外延层35的部分)外延生

spreading layer)。p

+

型区21、p

+

型区22具有使施加到沟槽7的底面的栅极绝缘膜8的电场缓解的功能。p

+

型区21与p型基区4分离而设置,所述p

+

型区21在深度方向上与沟槽7的底面对置。p

+

型区21也可以到达沟槽7的底面。p

+

型区22与p

+

型区21及沟槽7分离而设置在彼此相邻的沟槽7之间,并且与p型基区4接触。

95.p型基区4设置在半导体芯片30的正面与n-型漂移区2b之间。p型基区4是p型外延层34的除n

+

型源区5和p

++

型接触区6以外的部分。n

+

型源区5和p

++

型接触区6分别选择性地设置在半导体芯片30的正面与p型基区4之间。n

+

型源区5和p

++

型接触区6与p型基区4接触,并且在后述的层间绝缘膜11的接触孔与欧姆电极13欧姆接触。

96.也可以不设置p

++

型接触区6。在不设置p

++

型接触区6的情况下,p型基区4代替p

++

型接触区6而与欧姆电极13欧姆接触。这些n型电流扩散区3、p

+

型区21、p

+

型区22、n

+

型源区5以及p

++

型接触区6是通过离子注入而形成的扩散区,并选择性地设置在外延层35以及外延层34的内部。沟槽7贯通n

+

型源区5和p型基区4而到达n型电流扩散区3(在不设置n型电流扩散区3的情况下为n-型漂移区2b)。

97.在沟槽7的内部隔着栅极绝缘膜8而设置有栅电极9。层间绝缘膜11设置在半导体芯片30的正面,并且覆盖栅电极9。在层间绝缘膜11与后述的正面电极14之间的整个面也可以设置有例如防止金属原子从正面电极14侧向栅电极9侧扩散的阻挡金属12。欧姆电极13是在层间绝缘膜11的接触孔中设置在半导体芯片30的正面上的硅化物膜。欧姆电极13与p型基区4、n

+

型源区5以及p

++

型接触区6电连接。

98.正面电极14以埋入层间绝缘膜11的接触孔的方式在有源区41设置在半导体芯片30的正面的大致整个面。正面电极14经由欧姆电极13而与p型基区4、n

+

型源区5以及p

++

型接触区6电连接。阻挡金属12、欧姆电极13以及正面电极14作为源极而起作用。背面电极15设置在半导体芯片30的背面、例如《000-1》面(c面)、(n

+

型起始基板31的背面)整个面,与n

+

型漏区1电连接。背面电极15作为漏极而起作用。

99.(实施方式一的碳化硅半导体装置的制造方法)

100.接着,对实施方式一的碳化硅半导体装置的制造方法进行说明。图4是示出实施方式一的碳化硅半导体装置的制造方法的概要的流程图。

101.首先,形成将碳化硅作为半导体材料的半导体晶片(sic晶片)50(步骤s1:第一工序)。半导体晶片50是在n

+

型起始基板31上使外延层35外延生长而成的。在步骤s1的处理中,可以准备由碳化硅构成的起始晶片55来制作半导体晶片50,也可以购买半导体晶片50本身。

102.接着,在半导体晶片50的主面(外延层35侧的表面)的划线中形成标记(步骤s2:第二工序)。划线也被称为切割线,是形成在半导体晶片50的主面(图3的外延层35侧的表面)的线状区域,并且表示将半导体芯片单体化时的切断位置。例如,划线的宽度为100μm左右。

103.接着,通过结晶缺陷检查装置而进行检查,检测并获取半导体晶片50的外延层35的表面和内部的结晶缺陷的种类、大小(长度或表面积等)以及位置信息(步骤s3:第三工序)。结晶缺陷检查装置是例如lasertec株式会社制的sic晶片缺陷检查/审查装置sica88。在步骤s3的处理中检测出的结晶缺陷是形成于外延层的异物缺陷、三角缺陷以及扩展缺陷。这些结晶缺陷的大小和位置信息基于例如在步骤s2的处理中形成的标记来获取。

104.在此,图5是示出实施方式一的半导体晶片的划线与结晶缺陷检查装置所识别的

划线的俯视图。在图5中,利用细线表示的划线61是设置于半导体晶片50的划线,利用虚线表示的划线61a是以往的结晶缺陷检查装置所识别的划线,利用粗线表示的划线61b是实施方式一的结晶缺陷检查装置所识别的划线(图6也相同)。

105.在此,由于划线61通过切割而被大量切除,并且残留的部分也不流通电流,所以即使在划线61内存在结晶缺陷也没有问题。因此,结晶缺陷检查装置以不检查划线61内的结晶缺陷的方式预先设定划线61的位置位于哪。结晶缺陷检查装置所识别的划线61a、61b是指设定在结晶缺陷检查装置的划线的位置。另外,利用单点划线表示的标记62a是在结晶缺陷检查装置中设置在半导体晶片的划线没有偏离的情况下的设置于划线61的标记62的位置。

106.在实施方式一中,将结晶缺陷检查装置所识别的划线61b的端与标记62a的端之间的距离h1设为10μm以上且25μm以下。结晶缺陷检查装置所识别的划线61b的端与标记62a的端之间的距离h1是指划线61b的宽度与标记62的宽度之差的一半。在此,以往的结晶缺陷检查装置所识别的划线61a的宽度是与设置于半导体晶片50的划线61相同的宽度。在实施方式一中,使结晶缺陷检查装置所识别的划线61b的宽度比设置于半导体晶片50的划线61的宽度宽,将结晶缺陷检查装置所识别的划线61b的端与标记62a的端之间的距离h1设为10μm以上且25μm以下。

107.例如,通过使划线61b如图5的箭头所示那样地向外侧(与划线61b正交的方向)每次扩大宽度l1,从而调整从结晶缺陷检查装置所识别的划线61b的端起到标记62a的端为止的距离h1。结晶缺陷检查装置所识别的划线61b的宽度能够通过结晶缺陷检查装置的设定来改变。从结晶缺陷检查装置所识别的划线61b的端起到标记62a的端为止的距离h1例如为10μm以上且25μm以下,优选为15μm以上且20μm以下。该值是基于设置在半导体晶片50的划线61与结晶缺陷检查装置所识别的划线61b之间的偏离为10μm以内的。另外,这是因为若大于25μm,则不能够检测出原本应检测的结晶缺陷。

108.在此,在碳化硅半导体装置中,在边缘终端区42的最外周设置有沟道截止部43(参照图2)。由于从沟道截止部43起的外侧不流通电流,所以即使存在结晶缺陷也不给导通电压等元件特性带来影响。因此,也可以将结晶缺陷检查装置所识别的划线61b的端的位置扩展到沟道截止部43为止。在该情况下,结晶缺陷检查装置所识别的划线61b的端位于半导体芯片的沟道截止部43。向外侧扩展的宽度l1优选为从芯片端部起到沟道截止部43的靠有源区41侧的端部为止的距离l2(参照图2)以下。在该距离l2中包括从芯片端部起到沟道截止部43的靠边缘终端区42侧的端部为止的距离l3(未图示)、以及沟道截止部43的宽度。因此,通过使距离l3和/或沟道截止部43的宽度变大,从而能够使距离l2变大,并且能够使向外侧扩展的宽度l1变大。

109.通过如此操作,即使结晶缺陷检查装置所识别的划线61b与设置于半导体晶片50的划线61偏离,标记62也会进入到结晶缺陷检查装置所识别的划线61b内。因此,能够消除结晶缺陷检查装置将标记62误识别为结晶缺陷的情况。

110.另外,结晶缺陷检查装置所识别的划线也可以保持以往的划线61a的状态而使标记62变小。图6是示出实施方式一的半导体晶片的划线内的标记的俯视图。如图6所示,通过使在步骤s2中形成的标记62变得小于以往的大小,从而使标记62的大小变得小于划线61的宽度。如此,在实施方式一中,使结晶缺陷检查装置所识别的划线61a的宽度大于标记62的

大小。

111.例如,若将划线61与标记62的端部之间的距离设为h2,则标记62成为从划线61的端向内侧离开h2以上的大小。例如,h2为10μm以内,因此标记62成为从划线61的端向内侧离开10μm以上的大小。另外,若使标记62变得过小则变得难以定位,因此优选从划线61的端起到标记62的端部为止的距离为25μm以下。

112.通过如此地操作,从而即使划线61与结晶缺陷检查装置所识别的划线61a存在偏离,划线61内的标记62也会进入到结晶缺陷检查装置所识别的划线61a内。因此,即使在结晶缺陷检查装置所识别的划线61a的宽度与设置于半导体晶片50的划线61的宽度相同的情况下,也能够消除结晶缺陷检查装置将标记62误识别为结晶缺陷的情况。

113.另外,图7是示出实施方式一的半导体晶片的划线内的标记的位置的俯视图。划线61设置于定向平面54的方向的《11-20》方向、以及与定向平面54正交的《1-100》方向。在实施方式一中,也可以使标记62仅存在于《1-100》方向的划线61上(图7的区域a)、或者使所述标记62存在于《1-100》方向的划线61上的比率增多。

114.图8是示出实施方式一的半导体晶片的划线内的标记和线状的结晶缺陷的俯视图。线状的结晶缺陷64在定向平面54的方向的《11-20》方向上线状地生长。因此,结晶缺陷检查装置将沿《11-20》方向延伸的棒状的形状识别为线状的结晶缺陷64。在此,在《11-20》方向的划线61与结晶缺陷检查装置所识别的划线61b偏离的情况下,标记端部分63a成为沿《11-20》方向延伸的棒状的形状。由于该形状与线状的结晶缺陷64相似,所以结晶缺陷检查装置误识别为线状的结晶缺陷64。另一方面,在《1-100》方向的划线61与结晶缺陷检查装置所识别的划线61b偏离的情况下,标记端部分63b成为沿《1-100》方向延伸的棒状的形状,形状与线状的结晶缺陷64不同,结晶缺陷检查装置不将标记端部分63b识别为线状的结晶缺陷。

115.因此,通过使标记62仅存在于《1-100》方向的划线61上(图7的区域a)、或者使所述标记62存在于《1-100》方向的划线61上的比率增多,从而能够减少结晶缺陷检查装置将标记62误识别为结晶缺陷的情况。此时,仅在《1-100》方向的划线61上设置标记62的构成包括在《11-20》方向的划线61与《1-100》方向的划线61之间的交点设置标记62的构成。

116.如此,《1-100》方向的划线61内的标记62不会误被识别为结晶缺陷,因此,如图5所示,无需扩大结晶缺陷检查装置所识别的划线61b的宽度。例如,在比设置于半导体晶片50的划线61的宽度宽的情况下,也可以仅使《11-20》方向的结晶缺陷检查装置所识别的划线61b的宽度比设置于半导体晶片50的划线61的宽度宽。

117.另外,也能够将使结晶缺陷检查装置所识别的划线61b的宽度大于标记62的大小的情况、以及使标记62仅存在于《1-100》方向的划线61上或者使所述标记62存在于《1-100》方向的划线61上的比率增多的情况组合。例如,能够将减小到以往的大小的一半以下的尺寸的标记62仅配置在《1-100》方向的划线61上。

118.另外,虽然标记62如图5等所示那样地成为四边的形状,但是通过将该形状设为菱形等不与划线61平行的线的形状,从而能够进一步减少结晶缺陷检查装置的误检测。

119.接着,进行用于在半导体晶片50的各芯片区形成预定的元件结构(参照图3)的各种工艺(步骤s4:第四工序)。以下示出各种工艺的概要。首先,通过外延生长和离子注入,在外延层35选择性地形成n型外延层32、n-型外延层33、以及n型电流扩散区3。接着,通过光刻

safety operation area)、以及短路电流切断时的安全动作区域(scsoa:short circuit safe operation area)。在该情况下,合格品规格的上限值是成为额定时的漏电流值。

130.另外,在利用漏电流值来设定合格品规格的情况下,用于耐量评价的电特性是指例如连续通电时的正向浪涌电流耐量、连续通电寿命、连续通电时的反向恢复耐量、连续通电时的雪崩耐量、连续通电时的rbsoa、以及、连续通电时的scsoa。在该情况下,合格品规格是这些电特性的从设计值的变动量成为预定比率(例如20%)以下时的漏电流值的范围。此外,在mosfet中,在利用漏电流值来设定合格品规格的情况下,用于耐量评价的电特性是指栅极绝缘膜的绝缘破坏耐量。

131.栅极绝缘膜的绝缘破坏耐量是指例如时间零绝缘破坏(tzdb:time zero dielectric breakdown)耐量、将漏极和源极接地的状态下的因栅极电压施加而引起的经时绝缘破坏(tddb:time dependent dielectric breakdown)耐量、以及将源极接地的状态下的因对漏极施加预定电压(例如1200v)和施加栅极电压而引起的经时绝缘破坏(tddb)耐量。在该情况下,合格品规格是栅极绝缘膜8的绝缘破坏耐量的从设计值的变动量成为预定比率(例如20%)以下时的漏电流值(漏电流idss的电流值)的范围。

132.另外,在利用漏电流值来设定合格品规格的情况下,用于可靠性评价的试验是指,例如通过高温下的高电压施加来评价电特性的高温高电压施加试验、通过高温高湿下的高电压施加来评价电特性的高温高湿高电压施加试验、通过间断性地通电而交替地反复进行自发热和冷却从而评价因热疲劳而引起的动作寿命的功率循环(power cycle)试验、以及通过低温下的高电压施加来评价电特性的低温高电压施加试验。在该情况下,合格品规格是在从这些试验中得到的电特性的设计值的变动量成为预定比率(例如20%)以下时的漏电流值的范围。

133.虽然此处省略说明,但是除用于上述耐量评价和可靠性评价的试验以外,还进行用于确认或评价不影响耐量和/或可靠性的条件的其他的各种试验。这些其他的试验在即使在半导体晶片的状态下进行也没有障碍的情况下,可以在步骤s5的处理后且步骤s6的处理前的时刻进行,也可以在步骤s6的处理后对半导体芯片30进行。在步骤s7中,进行在半导体晶片50的状态下难以进行的试验、在加热或冷却到预定温度的情况等下若在半导体晶片50的状态下进行则耗费时间的试验即可。

134.接着,基于步骤s7的结果和预先获取的合格品规格来进行合格品候选的半导体芯片30的规格判定(步骤s8)。在步骤s8的处理中,对合格品候选的全部半导体芯片30适用一个合格品规格。由此,碳化硅半导体装置10的制造完成。

135.如上所述,根据实施方式一,将结晶缺陷检查装置所识别的划线的端与标记的端之间的距离设为10μm以上且25μm以下。例如,使结晶缺陷检查装置所识别的划线的宽度比设置于半导体晶片的划线的宽度宽。例如,使标记的大小比设置于半导体晶片的划线的宽度小。另外,使标记仅存在于《1-100》方向的划线上、或者使所述标记存在于《1-100》方向的划线上的比率增多。由此,即使结晶缺陷检查装置所识别的划线与设置于半导体晶片的划线偏离,也没有结晶缺陷检查装置将标记误识别为结晶缺陷而将检测出该结晶缺陷的半导体芯片作为不合格芯片而去除的情况。如此,能够使以往因过度检测而成为不合格的半导体芯片变为合格品,因此能够实现合格品率的提高、以及伴随于此的芯片成本的降低。

136.(实施方式二)

137.实施方式二的碳化硅半导体装置的结构与实施方式一(图3)相同,因此省略记载。另外,实施方式二的碳化硅半导体装置的制造方法相对于示出实施方式一的碳化硅半导体装置的制造方法的概要的流程图(图4),步骤s2和步骤s3不同。因此,仅对步骤s2和步骤s3进行说明。

138.在实施方式二中,在步骤s2中,在半导体晶片50的主面(外延层35侧的表面)的专用的芯片配置区或无效区53形成标记62。图9和图10是示出实施方式二的半导体晶片内的标记的位置的俯视图。如图9和图10所示,在实施方式二中,将标记62配置在除划线61内以外的区域。即,不将标记62配置在划线61内。

139.图9是将标记62配置在专用的芯片配置区的情况下的俯视图。在此,专用的芯片配置区是指,在半导体晶片50的芯片区之中形成标记62而不成为半导体芯片30的区域。由于标记62用于校准,所以最少配置三处,优选配置五处。在图9中,虽然标记62配置为十字形,但是除此以外也可以配置为四边形。

140.另外,在半导体晶片50上,为了进行设备的制造工艺的各工序中的管理、确认或检查等,在形成设备的晶片面内形成pcm(process control monitor:工艺控制监视器)。由于形成pcm的区域(pcm芯片)不成为作为产品的半导体芯片30,所以优选使专用的芯片配置区成为pcm芯片。由此,不会因专用的芯片配置区而使从半导体晶片制造出的半导体芯片30的数量减少。

141.在此,通过在将标记62配置于专用的芯片配置区的情况下,使结晶缺陷检查装置不检查专用的芯片配置区,从而结晶缺陷检查装置能够不将标记62识别为结晶缺陷。另外,虽然在将标记62配置于pcm芯片的情况下,结晶缺陷检查装置将标记62识别为结晶缺陷,但是由于pcm芯片用于检测产品的特性并且不会成为产品,所以没有问题。

142.图10是将标记62配置在无效区53的情况下的俯视图。无效区53是指半导体晶片50的最外侧的芯片区51与半导体晶片50的端部之间的、不被用作半导体芯片30的部分。通过将标记62配置在无效区53,从而不会减少从半导体晶片50制造出的半导体芯片30的数量。另外,也可以将芯片区51内的专用的芯片配置区和外周的无效区53组合而配置为例如x字状。其中,在将标记62设置于外周的无效区53的情况下,需要使标记62不过于设置在外侧。

143.如此,在实施方式二中,将标记62形成在专用的芯片配置区或无效区53。因此,即使结晶缺陷检查装置所识别出的划线61a与设置于半导体晶片50的划线61偏离,也不会将标记62误识别为结晶缺陷。因此,消除了结晶缺陷检查装置将标记62误识别为结晶缺陷而作为不合格芯片被去除的情况,能够使以往因过度检测而成为不合格的芯片变为合格品,因此能够提高合格品率,并且伴随于此而降低芯片成本。

144.另外,在实施方式二中,在步骤s2中,能够在不改变结晶缺陷检查装置所识别的划线61a的宽度的情况下,通过结晶缺陷检查装置进行检查。这是因为标记62不在划线61内。因此,不需要改变结晶缺陷检查装置所识别的划线61a的宽度,也能够适用于无法通过设定来改变该宽度的结晶缺陷检查装置。

145.如上所述,根据实施方式二,在半导体晶片的主面的专用的芯片配置区或无效区形成标记。由此,即使结晶缺陷检查装置所识别的划线与设置于半导体晶片的划线偏离,也没有结晶缺陷检查装置将标记误识别为结晶缺陷而作为不合格芯片被去除的情况,能够使以往因过度检测而成为不合格的芯片变为合格品,因此能够提高合格品率并且伴随于此而

降低芯片成本。

146.(实施方式一、实施方式二的效果)

147.针对使用sica装置作为结晶缺陷检查装置而判定为存在结晶缺陷的芯片,在通过目视进行检查时,在大致三成的芯片中不存在结晶缺陷。该大致三成的芯片是sica装置将标记误识别为线状的结晶缺陷的芯片。因此,在实施方式的制造方法中,能够几乎消除sica装置的误识别,因此能够使由sica装置判定为不合格的芯片中的大致三成的芯片成为合格品,能够提高合格品率。

148.以上,本发明能够在不脱离本发明的主旨的范围内进行各种改变,在上述各实施方式中,例如各部分的尺寸和/或杂质浓度等根据所要求的规格等进行各种设定。另外,在上述各实施方式中,虽然以mosfet为例进行了说明,但是各实施方式也能够适用于sbd。另外,在上述各实施方式中,虽然对sic的情况进行了说明,但是各实施方式也能够适用于gan。另外,在各实施方式中,将第一导电型设为n型,将第二导电型设为p型,但是本发明将第一导电型设为p型,将第二导电型设为n型也同样成立。

149.工业上的可利用性

150.如上所述,本发明的碳化硅半导体装置的制造方法在从六英寸的半导体晶片量产半导体芯片(碳化硅半导体装置)的情况下是有用的,特别适合于sbd或mosfet的制造。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1