半导体晶片的制作方法

半导体晶片

1.本技术是申请日为2018年11月2日、申请号为201880077213.0的中国专利发明申请“具有改进强度的半导体晶片”的分案申请。

技术领域

2.本公开涉及半导体装置,且特别是涉及具有增加强度的半导体装置及其制造方法。

背景技术:

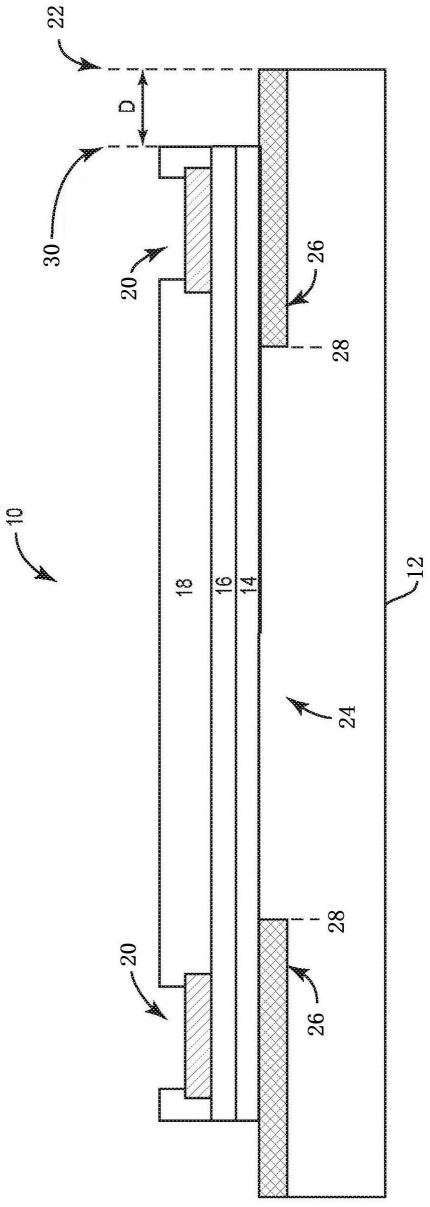

3.可在半导体晶片上一起制造许多半导体装置。为了说明的目的,图1示出了常规半导体晶片10,常规半导体晶片10包括基底12、基底12上方的第一钝化层14、第一钝化层14上方的第二钝化层16、第二钝化层16上方的第三钝化层18,以及多个接触焊盘20。基底12的边界由基底终止边缘22限定。基底12包括有源区域24以及有源区域24周围的势垒区域26,在该有源区域中,例如可通过一个或多个注入区域和一个或多个金属化层来提供多个半导体装置(未示出)。势垒区域26将有源区域24与基底终止边缘22电隔离,并因此与周围环境电隔离。势垒区域26总体上被设置为降低基底12的导电性的注入物,但也可以是蚀刻台面或浅沟槽隔离(sti)。通常,势垒区域26从内部势垒区域终止边缘28延伸到基底终止边缘22,以形成围绕常规半导体晶片10的周边的势垒。

4.第一钝化层14设置在有源区域24上方,并在势垒区域26上方延伸到钝化终止边缘30。第二钝化层16在第一钝化层14上方,并类似地延伸到钝化终止边缘30。第三钝化层18在第二钝化层16上方,并类似地延伸到钝化终止边缘30。接触焊盘20可设置在第二钝化层16上,并经由第三钝化层18中的一个或多个开口暴露于外部环境,尽管未示出,但第一钝化层14和第二钝化层16内的金属化层可将接触焊盘耦接到有源区域24中的一个或多个半导体装置。钝化终止边缘30从基底终止边缘22内移一定距离d。

5.第一钝化层14、第二钝化层16和第三钝化层18被设置成将有源区域24中的半导体装置与周围环境电气地且物理地隔离。然而,当常规半导体晶片10处于潮湿环境中并经受高温和/或偏压时,第一钝化层14、第二钝化层16和第三钝化层18中的一个或多个可从其下方层脱层,以允许湿气渗入有源区域24。这可能导致常规半导体晶片10的故障。此问题由于操作有源区域24中的一个或多个半导体装置所产生的电场而恶化,该电场可能在钝化终止边缘30处非常高。此电场可能从钝化终止边缘30朝向有源区域24吸引湿气,并由此导致如上所述的常规半导体晶片10的故障。

6.鉴于上述情况,需要一种具有改进强度的半导体晶片及其制造方法。

技术实现要素:

7.本公开涉及半导体装置,且特别是涉及具有增加强度的半导体装置及其制造方法。在一个实施例中,半导体晶片包括基底、基底上方的第一钝化层,以及第一钝化层和基底上方的第二钝化层。基底具有由基底终止边缘限定的边界。第一钝化层在基底上方,使得

其终止于第一钝化终止边缘,该第一钝化终止边缘从基底终止边缘内移第一距离。第二钝化层在第一钝化层和基底上方,使得其终止于第二钝化终止边缘,该第二钝化终止边缘从基底终止边缘内移第二距离。第二距离小于第一距离,使得第二钝化层与第一钝化层重叠。通过使第二钝化层与第一钝化层重叠,因为可防止湿气穿透第一钝化层和第二钝化层,所以可显著地增加半导体晶片的强度。

8.在一个实施例中,一种用于制造半导体晶片的方法包括以下步骤:设置基底;在基底上方设置第一钝化层;以及在第一钝化层上方设置第二钝化层。基底具有由基底终止边缘限定的边界。第一钝化层在基底上方,使得其终止于第一钝化终止边缘,该第一钝化终止边缘从基底终止边缘内移第一距离。第二钝化层设置在第一钝化层和基底上方,使得其终止于第二钝化终止边缘,该第二钝化终止边缘从基底终止边缘内移第二距离。第二距离小于第一距离,使得第二钝化层与第一钝化层重叠。通过使第二钝化层与第一钝化层重叠,因为可防止湿气穿透第一钝化层和第二钝化层,所以可显著地增加半导体晶片的强度。

9.在结合附图阅读了以下优选实施例的详细描述之后,本领域技术人员将理解本公开的范围并认识到其附加方面。

附图说明

10.结合到本说明书中并形成本说明书的一部分的附图示出了本公开的若干方面,并且与该描述一起用于解释本公开的原理。

11.图1示出了常规半导体晶片。

12.图2至图13示出了根据本公开的各种实施例的半导体晶片。

13.图14是描述了根据本公开的各种实施例的用于制造半导体晶片的方法的流程图。

具体实施方式

14.下面阐述的实施例代表了使得本领域技术人员能够实践实施例的必要信息,并且示出了实践实施例的最佳模式。在根据附图阅读以下描述时,本领域技术人员将理解本公开的概念,并且将认识到本文未具体解决的这些概念的应用。应理解,这些概念和应用落入本公开和所附权利要求的范围内。

15.应理解,尽管术语第一、第二等可在本文用来描述各种元件,但这些元件不应受这些术语的限制。这些术语仅用于将一个元件与另一个元件区分。例如,在不脱离本公开的范围的情况下,第一元件可以被称为第二元件,并且类似地,第二元件可以被称为第一元件。如本文所使用的,术语“和/或”包括一个或多个相关联的所列项目的任何和所有组合。

16.应理解,当诸如层、区域或基底的元件被称为在另一元件“上”或延伸到另一元件“上”时,其可直接在该另一元件上或直接延伸到该另一元件上,或者也可存在中间元件。相反,当元件被称为“直接在另一元件上”或“直接延伸到”另一元件上时,不存在中间元件。同样,应理解,当诸如层、区域或基底的元件被称为在另一元件“上方”或在另一元件“上方”延伸时,其可直接在该另一元件上方或直接在该另一元件上方延伸,或者也可存在中间元件。相反,当元件被称为“直接在另一元件上方”或“直接在另一元件上方”延伸时,不存在中间元件。还将理解,当元件被称为“连接”或“耦接”到另一元件时,其可直接连接或耦接到该另一元件,或者可存在中间元件。相反,当元件被称为“直接连接”或“直接耦接”到另一元件

时,不存在中间元件。

17.相对性术语,例如“下方”或“上方”或“上”或“下”或“水平”或“竖直”在本文中可用于描述如图所示的一个元件、层或区域与另一个元件、层或区域的关系。应理解,这些术语和上面讨论的那些术语旨在包括除了图中所示的定向之外的装置的不同定向。

18.本文所使用的术语仅用于描述特定实施例的目的,并非旨在限制本公开。如本文所使用的,单数形式“一”、“一个”和“该”旨在也包括复数形式,除非上下文另有明确指示。还将理解,术语“包括”、“包含”、“含有”和/或“具有”当在本文中使用时指定所陈述的特征、整数、步骤、操作、元件和/或部件的存在,但不排除一个或多个其他特征、整数、步骤、操作、元件、部件和/或其组的存在或添加。

19.除非另有定义,否则本文使用的所有术语(包括技术和科学术语)具有与本公开所属领域的普通技术人员通常理解的相同含义。还应理解,本文使用的术语应解释为具有与其在本说明书的上下文和相关技术中的含义一致的含义,并且不应解释为理想化的或过于正式的意义,除非本文明确地这样定义。

20.图2示出了根据本公开的一个实施例的半导体晶片32。半导体晶片32包括基底34、基底34上方的第一钝化层36、第一钝化层36和基底34上方的第二钝化层38、第二钝化层38上方的第三钝化层40,以及多个接触焊盘42。基底34的边界由基底终止边缘44限定。基底34包括有源区域46以及有源区域46周围的势垒区域48,在该有源区域中,例如可通过一个或多个注入区域和一个或多个金属化层来提供多个半导体装置(未示出)。势垒区域48将有源区域46与基底终止边缘44电隔离,并因此与周围环境电隔离。势垒区域48可设置为降低基底34的导电性的注入区域(例如,注入氮、氢、氦、镁、锆、氪、氩和/或铁的区域),并且可从势垒区域内边缘50延伸到基底终止边缘44。半导体装置可包括任何类型的装置,例如二极管、高电子迁移率晶体管(hemt)、场效应晶体管(fet)、金属氧化物半导体场效应晶体管(mosfet)等。

21.第一钝化层36设置在有源区域46上方,并在势垒区域48上方延伸到第一钝化终止边缘52。第二钝化层38在第一钝化层36和基底34上方,并延伸到第二钝化终止边缘54。第三钝化层40在第二钝化层38上方,并且类似地延伸到第二钝化终止边缘54。接触焊盘42可设置在第二钝化层38上,并且经由第三钝化层40中的一个或多个开口暴露于外部环境。尽管未示出,但第一钝化层36和第二钝化层38内的金属化层可将接触焊盘耦接到有源区域46中的一个或多个半导体装置。

22.第一钝化终止边缘52从基底终止边缘44内移第一距离d1。在各种实施例中,第一距离d1可以在1μm至150μm之间。第二钝化终止边缘54从基底终止边缘44内移第二距离d2。在各种实施例中,第二距离d2可以在0.5μm至50μm之间。值得注意的是,第二距离d2小于第一距离d1,使得第二钝化层38和第三钝化层40与第一钝化层36重叠,因此,第一钝化终止边缘52通过第二钝化层38和第三钝化层40与周围环境屏蔽。以此方式设置第一钝化层36、第二钝化层38和第三钝化层40通过防止湿气进入有源区域46中而增加了半导体晶片32的强度。在一个实施例中,第一距离d1与第二距离d2之间的差值大于0.5μm且小于100μm。通常,第一距离d1与第二距离d2之间的差值可大于x且小于y。在各种实施例中,x可以是1μm、2μm、3μm、4μm、5μm、6μm、7μm、8μm、9μm、10μm,以及至多但不包括50μm。对于这些实施例中的任一种,y可以是50μm、60μm、70μm、80μm、90μm,以及至多100μm。

23.虽然仅示出了三个钝化层,但在不脱离本公开的原理的情况下,本文讨论的原理可应用于任何数量的钝化层。此外,第一钝化层36、第二钝化层38和第三钝化层40本身可包括多个层。最后,本公开的原理可应用于少至两个钝化层。也就是说,第三钝化层40在以上讨论的实施例中是可选的。另外,虽然基底34被示出为单个层,但基底34可包括多个层(例如,载体层和在载体层的顶部上的一个或多个外延层)。在这些实施例中,可通过一个或多个外延层而不是载体层来提供势垒区域48。在一个实施例中,基底34可包括氮化镓(gan)。在其他实施例中,基底34可包括硅(si)、碳化硅(sic)或任何其他半导体材料系统。

24.在一个实施例中,第一钝化层36、第二钝化层38和第三钝化层40包括化学计量和非化学计量的氧化铝、二氧化硅、氮化硅、氮氧化硅、氧化硅和/或氧化锆的配方。此外,在一些实施例中,第一钝化层36、第二钝化层38和第三钝化层40的成分可以交替。分开地施加钝化层和/或使钝化层的成分交替可减少横过多于一个层的层中的缺陷(例如,针孔)的存在,以防止有源区域46暴露于外部环境。

25.图3示出了根据本公开的一个实施例的半导体晶片32的俯视图,其示出了第一钝化终止边缘52和第二钝化终止边缘54相对于基底终止边缘44的相对位置。如图所示,第一钝化终止边缘52和第二钝化终止边缘54从半导体晶片32的周边内移,使得第二钝化终止边缘54嵌套在基底终止边缘44内并且第一钝化终止边缘52嵌套在第二钝化终止边缘54内。

26.图4示出了根据本公开的附加实施例的半导体晶片32。图4所示的半导体晶片32与图2所示的基本上相同,除了图4中的第三钝化层40在第二钝化层38上方延伸到第三钝化终止边缘56,该第三钝化终止边缘从基底终止边缘44内移第三距离d3。第三距离d3小于第二距离d2,使得第三钝化层40与第一钝化层36和第二钝化层38重叠。这样做可进一步增加半导体晶片32的强度,因为其可在第二钝化终止边缘54与周围环境之间提供势垒,并且在第一钝化终止边缘52与周围环境之间提供附加势垒。因为钝化层可分开设置和/或在成分上交替,所以这些层可在不同条件下抵抗脱层,这可在较宽范围的环境条件下防止湿气进入。

27.在图4所示的实施例中,第一距离d1可以更大,使得其可以在1.5μm至250μm之间。第二距离d2可以在1μm至150μm之间。第三距离可以在0.5μm至50μm之间。在一个实施例中,第一距离d1与第二距离d2之间的差值大于5μm且小于50μm。类似地,第二距离d2与第三距离d3之间的差值大于0.5μm且小于50μm。通常,第一距离d1与第二距离d2之间的差值以及第二距离d2与第三距离d3之间的差值可以大于x且小于y。在各种实施例中,x可以是1μm、2μm、3μm、4μm、5μm、6μm、7μm、8μm、9μm、10μm,以及至多但不包括50μm。对于这些实施例中的任一种,y可以是50μm、60μm、70μm、80μm、90μm,以及至多100μm。

28.图5示出了根据本公开的一个实施例的半导体晶片32的俯视图,其示出了第一钝化终止边缘52、第二钝化终止边缘54和第三钝化终止边缘56相对于基底终止边缘44的相对位置。如图所示,第一钝化终止边缘52、第二钝化终止边缘54和第三钝化终止边缘56从半导体晶片32的周边内移,使得第三钝化终止边缘56嵌套在基底终止边缘44内,第二钝化终止边缘54嵌套在第三钝化终止边缘56内,并且第一钝化终止边缘52嵌套在第二钝化终止边缘54内。

29.如上所述,电场在任何钝化层的终止边缘处的建立可有助于湿气和/或离子进入,因为其可将颗粒吸引向有源区域46,并由此促进其脱层。为了减轻这种效应,图6示出了图2所示的半导体晶片32的一侧的放大图,其还包括电荷重新分配路径58。电荷重新分配路径

58被设置为基底34上的在第一钝化终止边缘52与第二钝化终止边缘54之间的金属层。虽然未示出,但在一些实施例中,电荷重新分配路径58可设置在第一钝化终止边缘52内或者可横穿第一钝化终止边缘52和/或第二钝化终止边缘54。在一个实施例中,电荷重新分配路径58可设置在半导体晶片32的周边周围并耦接到固定电位,诸如地面。

30.除了减轻湿气和/或离子进入半导体晶片32的有源区域之外,电荷重新分配路径58也可提供其他操作益处。虽然图6所示的电荷重新分配路径58形成围绕半导体晶片32的周边的环,但电荷重新分配路径58可设置在电荷重新分布可能有益的(例如,以避免湿气和/或离子进入)的任何区域中,并因此可以任何形状设置在半导体晶片上的任何位置处(例如,在有源区域的一部分上方、将有源区域二等分,等等)。在一些实施例中,电荷重新分配路径58形成闭合路径,而在其他实施例中,电荷重新分配路径58可保持开放。此外,虽然电荷重新分配路径58被示出为基底34上的在基底34与第一钝化层36之间的金属层,但在不脱离本文描述的原理的前提下,电荷重新分配路径58可设置在基底34的相对侧(与第一钝化层36相对)、设置在第一钝化层36上、设置在第二钝化层38上、设置在第三钝化层40上,或者设置在任何其他层上。在各种实施例中,电荷重新分配路径58的位置在装置的不同区域中可以不同。例如,半导体晶片32的一个横向边缘可以被保留用于其有源区域46中的半导体装置的栅极触点并因此被称为“栅极侧”,而半导体晶片的相对横向边缘可以被保留用于其有源区域46中的半导体装置的漏极触点并因此被称为“漏极侧”。由于半导体晶片32的这些不同部分中的电场可以不同,所以电荷重新分配路径58可以以第一图案设置在基底34、第一钝化层36、第二钝化层38、第三钝化层40或半导体晶片32的栅极侧上的任何其他层中的一个上的第一位置,并且以第二图案设置在基底34、第一钝化层36、第二钝化层38、第三钝化层40或半导体晶片的漏极侧上的任何其他层中的一个上的第二位置。通常,电荷重新分配路径58的特定图案和位置对于半导体晶片32的不同区域可以是不同的,因为这些不同区域中的场可以是不同的,并因此可能需要以不同方式重新分布以提高半导体晶片32的性能。

31.图7示出了根据本公开的一个实施例的包括电荷重新分配路径58的半导体晶片32的俯视图。如图所示,电荷重新分配路径58从半导体晶片32的在第一钝化终止边缘52与第二钝化终止边缘54之间的周边内移。提供如图6和图7所示的电荷重新分配路径58减小了第一钝化终止边缘52和第二钝化终止边缘54处的电场,这进而减少了湿气和离子进入并且增加了半导体晶片32的强度。电荷重新分配路径58可以是金属层,该金属层包括铝,钛、硅、镍和铂的合金,钛、铝、镍和金的合金,钛镍和铝的合金,锗、镍和铝的合金,以及用于与附随有源装置形成电接触的任何其他金属系统。

32.图8示出了根据本公开的一个实施例的图4所示的半导体晶片32的一侧的放大图,其还包括电荷重新分配路径58。电荷重新分配路径58被设置为基底34上的在第一钝化终止边缘52与第二钝化终止边缘54之间的金属层。虽然未示出,但在一些实施例中,电荷重新分配路径58可设置在第一钝化终止边缘52内,可设置在第二钝化终止边缘54与第三钝化终止边缘56之间,或者可横穿第一钝化终止边缘52、第二钝化终止边缘54和第三钝化终止边缘56。电荷重新分配路径58可设置在半导体晶片32的周边周围并耦接到固定电位,诸如地面。

33.图9示出了根据本公开的一个实施例的半导体晶片32的俯视图,其包括电荷重新分配路径58。如图所示,电荷重新分配路径58从半导体晶片32的在第一钝化终止边缘52与

第二钝化终止边缘54之间的周边内移。提供如图8和图9所示的电荷重新分配路径58减小了第一钝化终止边缘52、第二钝化终止边缘54和第三钝化终止边缘56处的电场,这进而减少了湿气进入并且增加了半导体晶片32的强度。电荷重新分配路径58可以是金属层,该金属层包括铝,钛、硅、镍和铂的合金,钛、铝、镍和金的合金,钛镍和铝的合金,锗、镍和铝的合金,以及用于与附随有源装置形成电接触的任何其他金属系统。

34.图10示出了根据本公开的一个实施例的图2所示的半导体晶片32的一侧的放大图,其还包括电荷重新分配路径60。电荷重新分配路径60优选地被设置为基底34的在势垒区域48外部的导电(即,未注入或导电注入)区域。即,势垒区域48不是在势垒区域内边缘50与基底终止边缘44之间延伸,而是在势垒区域内边缘50与势垒区域外边缘62之间延伸,该势垒区域外边缘从基底终止边缘44内移第三距离d3。包括电荷重新分配路径60的区域也可部分地被注入有导电掺杂剂,以具有比有源区域的表面导电部分的导电性高的导电性。第三距离d3可小于第一钝化终止边缘52与基底终止边缘44之间的第一距离d1且大于第二钝化终止边缘54与基底终止边缘44之间的第二距离d2。形成电荷重新分配路径60的基底34的导电区域可通过基底34或通过直接接触顶侧接地的或非零偏置的接触焊盘而耦接到地面。例如,基底34的表面导电区域可通过基底34的背面上的接触焊盘(未示出)连接到地面。这可通过在注入势垒区域48时进行附加的掩模来实现,如下所述。在不脱离本文原理的情况下,电荷重新分配路径60可以任何数量的形状设置,并且可以设置为闭合或开放路径。

35.图11示出了根据本公开的一个实施例的半导体晶片32的俯视图,其包括电荷重新分配路径60。如图所示,电荷重新分配路径60在势垒区域48的外侧上作为导电区域或未注入区域。虽然未示出,但势垒区域外边缘62可设置在第一钝化终止边缘52内(即,第三距离d3可大于第一距离d1)或设置在第一钝化终止边缘52与第二钝化终止边缘54之间的任何其他点处。提供如图10和图11所示的电荷重新分配路径60减小了第一钝化终止边缘52和第二钝化终止边缘54处的电场,这进而减少了湿气进入并增加了半导体晶片32的强度。虽然电荷重新分配路径60可以是未注入的区域,但其也可作为导电区域而被注入,例如使用硅(si)、钙(ca)、氧(o)、锗(ge)或碳(c)。

36.图12示出了根据本公开的一个实施例的图4所示的半导体晶片32的一侧的放大图,其还包括电荷重新分配路径60。电荷重新分配路径60被设置为基底34的在势垒区域48外部的导电(即,未注入)区域。即,势垒区域48不是在势垒区域内边缘50与基底终止边缘44之间延伸,而是在势垒区域内边缘50与势垒区域外边缘62之间延伸,该势垒区域外边缘从基底终止边缘44内移第四距离d4。第四距离d4可小于第一钝化终止边缘52与基底终止边缘44之间的第一距离d1且大于第二钝化终止边缘54与基底终止边缘44之间的第二距离d2。形成电荷重新分配路径60的基底34的导电区域可通过基底34耦接到地面。例如,基底34的导电区域可通过基底34的背面上的接触焊盘(未示出)连接到地面。

37.图13示出了根据本公开的一个实施例的半导体晶片32的俯视图,其包括电荷重新分配路径60。如图所示,电荷分配路径60在势垒区域48的外侧上作为导电区域或未注入区域。虽然未示出,但势垒区域外边缘62可设置在第一钝化终止边缘52内部(即,第四距离d4可大于第一距离d1),可设置在第二钝化终止边缘54与第三钝化终止边缘56之间(即,第四距离d4可大于第三距离d3且小于第二距离d2),或者可设置在第一钝化终止边缘52与第二钝化终止边缘54之间的任何其他点处。提供如图12和图13所示的电荷重新分配路径60减小了

第一钝化终止边缘52、第二钝化终止边缘54和第三钝化终止边缘56处的电场,这进而减少了湿气进入并且增加了半导体晶片32的强度。虽然电荷重新分配路径60可以是未注入的区域,但其也可作为导电区域而被注入,例如使用硅(si)、钙(ca)、氧(o)、锗(ge)或碳(c)。

38.虽然上面关于半导体晶片讨论了电荷重新分配路径,但本文描述的原理也可应用于其他装置,例如单片微波集成电路。

39.图14是示出了根据本公开的一个实施例的用于制造半导体晶片的方法的流程图。首先,设置基底(步骤100)。然后在基底中的有源区域周围设置势垒区域(步骤102)。这可包括例如对基底的区域进行注入,使得其不再导电。这可通过用氮(n)、氢(h)、氦(he)、镁(mg)、锆(zr)、氪(kr)、氩(ar)和铁(fe)对基底进行注入来实现,但也可以是蚀刻台面或浅沟槽隔离(sti)。在电荷重新分配路径被设置为势垒区域外部的导电区域或未注入区域的实施例中,这可包括在对势垒区域进行注入时进行附加掩模,使得其终止于从基底终止边缘内移的势垒区域外边缘。在其他实施例中,这可包括在势垒区域外部提供附加注入以使此区域更具导电性。这可通过用硅(si)、钙(ca)、氧(o)、锗(ge)或碳(c)对基底进行注入来实现。然后在半导体晶片的有源区域中设置多个半导体装置(步骤104)。这可包括例如对有源区域内的各种区域进行注入、设置用于触点的金属层,以及本领域技术人员将理解的其他步骤。如果电荷重新分配路径不是设置为势垒区域外部的导电区域,而是设置为基底上的金属层,则设置电荷重新分配路径(步骤106)。这可包括如上所述的进行掩模并将金属层沉积在基底表面上。然后在基底上方设置第一钝化层(步骤108)。如上所述,第一钝化层可终止于第一钝化终止边缘。然后在第一钝化层和基底上方设置第二钝化层(步骤110)。如上所述,此第二钝化层可终止于第一钝化终止边缘与基底终止边缘之间的第二钝化终止边缘,使得第二钝化层与第一钝化层重叠。然后,可在第二钝化层上方设置第三钝化层(步骤112)。如上所述,第三钝化层可终止于第二钝化终止边缘,或者可终止于第二钝化终止边缘与基底终止边缘之间的第三钝化终止边缘。

40.本领域技术人员将认识到对本公开的优选实施例的改进和修改。所有这种改进和修改都被认为是在本文所公开的概念和所附权利要求的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1