外延结构及其制作方法、发光芯片以及显示面板与流程

本申请涉及显示,特别涉及一种外延结构、一种外延结构的制作方法、一种具有该外延结构的发光芯片以及一种具有该发光芯片的显示面板。

背景技术:

1、半导体发光二极管(light-emitting diode,led)主要是通过半导体材料中导带中的电子和价带中的空穴辐射复合产生光子,将电能直接转化为光能的电子元器件。与传统的光源相比,发光二极管具有高效、节能、环保和寿命长等优点,在节能减排和绿色发展中发挥了重要作用,同时也在显示屏领域得到了广泛的应用。

2、在半导体发光二极管中,由于电子的有效质量比空穴小,且电子的迁移率比空穴大,这就导致电子与空穴不仅仅在有源区发生复合,在有源区以外也存在电子与空穴的复合发光。这样就使得有源区内的载流子(电子和空穴)数量减少,降低了有源区内电子与空穴的复合几率,导致半导体发光二极管的内量子效率(internal quantum efficiency,iqe)较低。

3、鉴于此,如何在提高电子与空穴在有源区的复合几率,以提高发光二极管的内量子效率是本领域技术人员亟待解决的问题。

技术实现思路

1、鉴于上述现有技术的不足,本申请的目的在于提供一种外延结构、一种外延结构的制作方法、一种具有该外延结构的发光芯片以及一种具有该发光芯片的显示面板,其旨在提高电子与空穴在有源区的复合几率,以提高发光二极管的内量子效率。

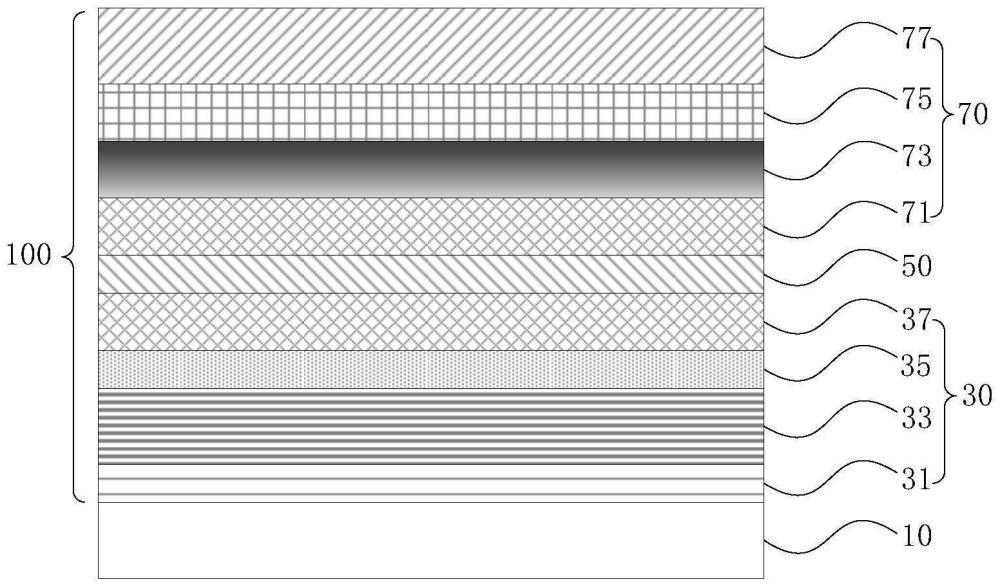

2、一种外延结构,包括依次层叠设置的第一半导体组件、有源层以及第二半导体组件。其中,所述第二半导体组件包括依次层叠于所述有源层上的第一波导层、第一限制层、过渡层以及电流扩展层,所述第一限制层的掺杂浓度由所述第一波导层指向所述过渡层的方向逐渐增加,所述第一限制层用于阻挡电子从所述有源层溢出。

3、上述的外延结构包括依次层叠设置的第一半导体组件、有源层以及第二半导体组件。其中,所述第一半导体组件向所述有源层提供电子,所述第二半导体组件包括依次层叠于所述有源层上的第一波导层、第一限制层、过渡层以及电流扩展层,所述第一限制层的掺杂浓度逐渐增加,所述第一限制层向所述有源层提供空穴,并用于阻挡电子从所述有源层溢出,提高了电子与空穴的复合几率,进而提高了发光效率。

4、可选地,所述第一限制层的掺杂浓度增加方式包括线性增加、非线性增加和阶梯式增加中的任意一种或多种组合。

5、可选地,所述有源层包括多组交替层叠设置的量子阱层和量子垒层,且多个所述量子阱层的厚度由所述第一半导体组件指向所述第二半导体组件的方向逐渐增大。

6、可选地,所述第一半导体组件包括依次层叠设置的缓冲层、反射层、第二限制层以及第二波导层。所述缓冲层为砷化镓层,所述反射层为交替设置的砷化铝层和砷化铝镓层,所述第二限制层为磷化铝铟,所述第二波导层为磷化铝镓铟层。

7、可选地,所述第一波导层的厚度为0.07um至0.1um,所述第一限制层的厚度为0.3um至1um,所述过渡层的厚度为0.01um至0.15um,所述电流扩展层的厚度为5um至6um,所述有源层的厚度为0.2um至0.3um,所述缓冲层的厚度为0.4um至0.6um,所述反射层的厚度为2um至4um,所述第二限制层的厚度为0.25um至0.45um,所述第二波导层的厚度为0.06um至0.1um。

8、可选地,所述第一限制层的掺杂浓度为3e17cm-3至9e17cm-3。

9、基于同样的发明构思,本申请还提供一种发光芯片,所述发光芯片包括第一电极、第二电极以及上述的外延结构,所述第一电极与所述外延结构的第一半导体组件电连接,所述第二电极与所述外延结构的第二半导体组件电连接。

10、上述的发光芯片包括第一电极、第二电极以及上述的外延结构,所述外延结构包括依次层叠设置的第一半导体组件、有源层以及第二半导体组件。其中,所述第一半导体组件向所述有源层提供电子,所述第二半导体组件包括依次层叠于所述有源层上的第一波导层、第一限制层、过渡层以及电流扩展层,所述第一限制层的掺杂浓度逐渐增加,所述第一限制层向所述有源层提供空穴,并用于阻挡电子从所述有源层溢出,提高了电子与空穴的复合几率,进而提高了发光效率。

11、基于同样的发明构思,本申请还提供一种显示面板,所述显示面板包括驱动基板以及上述的发光芯片,多个所述发光芯片设置在所述驱动基板上,并与所述驱动基板电连接,所述驱动基板用于向多个所述发光芯片传输电信号以控制多个所述发光芯片发光。

12、上述的显示面板包括驱动基板以及发光芯片,所述发光芯片包括第一电极、第二电极以及上述的外延结构,所述外延结构包括依次层叠设置第一半导体组件、有源层以及第二半导体组件。其中,所述第一半导体组件向所述有源层提供电子,所述第二半导体组件包括依次层叠于所述有源层上的第一波导层、第一限制层、过渡层以及电流扩展层,所述第一限制层的掺杂浓度逐渐增加,所述第一限制层向所述有源层提供空穴,并用于阻挡电子从所述有源层溢出,提高了电子与空穴的复合几率,进而提高了发光效率。

13、基于同样的发明构思,本申请还提供一种外延结构的制作方法,用于制作上述的外延结构,所述制作方法包括:

14、提供一衬底;

15、在所述衬底上生成第一半导体组件;

16、在所述第一半导体组件背对所述衬底的表面上形成有源层;

17、在所述有源层背对所述第一半导体组件的表面上生成第二半导体组件,其中,所述第二半导体组件包括依次层叠于所述有源层上的第一波导层、第一限制层、过渡层以及电流扩展层。

18、可选地,所述在所述有源层背对所述第一半导体组件的表面上生成第二半导体组件,包括:

19、通入所述第一波导层对应的ⅲ族源和ⅴ族源,以在所述有源层背对所述第一半导体组件的表面上生成所述第一波导层;

20、通入所述第一限制层对应的ⅲ族源、ⅴ族源以及掺杂源,以在所述第一波导层背对所述有源层的表面上生成所述第一限制层,其中,所述掺杂源的浓度随生长时间而增加;

21、通入所述过渡层对应的ⅲ族源、ⅴ族源以及掺杂源,以在所述第一限制层背对所述第一波导层的表面上生成所述过渡层;

22、通入所述电流扩展层对应的ⅲ族源、ⅴ族源以及掺杂源,以在所述过渡层背对所述第一限制层的表面上生成所述电流扩展层。

23、上述的制作方法包括:提供一衬底;在所述衬底上生成第一半导体组件;在所述第一半导体组件背对所述衬底的表面上形成有源层;在所述有源层背对所述第一半导体组件的表面上生成第二半导体组件,其中,所述第二半导体组件包括依次层叠于所述有源层上的第一波导层、第一限制层、过渡层以及电流扩展层。所述第一限制层的掺杂浓度逐渐增加,所述第一限制层向所述有源层提供空穴,并用于阻挡电子从所述有源层溢出,提高了电子与空穴的复合几率,进而提高了发光效率。

技术特征:

1.一种外延结构,其特征在于,包括依次层叠设置的第一半导体组件、有源层以及第二半导体组件,其中,所述第二半导体组件包括依次层叠于所述有源层上的第一波导层、第一限制层、过渡层以及电流扩展层,所述第一限制层的掺杂浓度由所述第一波导层指向所述过渡层的方向逐渐增加,所述第一限制层用于阻挡电子从所述有源层溢出。

2.如权利要求1所述的外延结构,其特征在于,所述第一限制层的掺杂浓度增加方式包括线性增加、非线性增加和阶梯式增加中的任意一种或多种组合。

3.如权利要求1所述的外延结构,其特征在于,所述有源层包括多组交替层叠设置的量子阱层和量子垒层,且多个所述量子阱层的厚度由所述第一半导体组件指向所述第二半导体组件的方向逐渐增大。

4.如权利要求3所述的外延结构,其特征在于,所述第一半导体组件包括依次层叠设置的缓冲层、反射层、第二限制层以及第二波导层,其中,所述缓冲层为砷化镓层,所述反射层为交替设置的砷化铝层和砷化铝镓层,所述第二限制层为磷化铝铟,所述第二波导层为磷化铝镓铟层。

5.如权利要求4所述的外延结构,其特征在于,所述第一波导层的厚度为0.07um至0.1um,所述第一限制层的厚度为0.3um至1um,所述过渡层的厚度为0.01um至0.15um,所述电流扩展层的厚度为5um至6um,所述有源层的厚度为0.2um至0.3um,所述缓冲层的厚度为0.4um至0.6um,所述反射层的厚度为2um至4um,所述第二限制层的厚度为0.25um至0.45um,所述第二波导层的厚度为0.06um至0.1um。

6.如权利要求1-5任一项所述的外延结构,其特征在于,所述第一限制层的掺杂浓度范围为3e17cm-3至9e17cm-3。

7.一种发光芯片,其特征在于,包括第一电极、第二电极以及如权利要求1-6任一项所述的外延结构,所述第一电极与所述外延结构的第一半导体组件电连接,所述第二电极与所述外延结构的第二半导体组件电连接。

8.一种显示面板,其特征在于,包括驱动基板以及多个如权利要求7所述的发光芯片,多个所述发光芯片设置在所述驱动基板上,并与所述驱动基板电连接,所述驱动基板用于向多个所述发光芯片传输电信号以控制多个所述发光芯片发光。

9.一种外延结构的制作方法,用于制作如权利要求1-6任一项所述的外延结构,其特征在于,所述制作方法包括:

10.如权利要求9所述的外延结构的制作方法,其特征在于,所述在所述有源层背对所述第一半导体组件的表面上生成第二半导体组件,包括:

技术总结

本申请涉及一种外延结构,包括依次层叠设置的第一半导体组件、有源层以及第二半导体组件。其中,所述第二半导体组件包括依次层叠于所述有源层上的第一波导层、第一限制层、过渡层以及电流扩展层,所述第一限制层的掺杂浓度由所述第一波导层指向所述过渡层的方向逐渐增加,所述第一限制层用于阻挡电子从所述有源层溢出,提高了电子与空穴的复合几率,进而提高了发光效率。本申请涉及一种发光芯片、一种显示装置以及一种外延结构的制作方法。

技术研发人员:谷鹏军

受保护的技术使用者:重庆康佳光电技术研究院有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!