芯片堆叠结构的制作方法

1.本发明涉及一种芯片堆叠结构,尤指一种可避免磁场干扰的芯片堆叠结构。

背景技术:

2.在现有的功率转换器中,通常需要使用电感、电容搭配开关元件的切换来 控制功率转换器的电力转换,且通常是使用金氧半场效电晶(mosfet)体来做 为开关元件使用。具体地,功率转换器中的开关元件大多使用金氧半场效电晶 芯片,搭配例如但不限于,用以驱动或控制金氧半场效电晶芯片的芯片封装而 成,以构成特定封装结构的开关元件。

3.以图1为例为现有的开关元件封装结构。传统的开关元件封装结构包括导 线架1、第一开关芯片2及控制芯片4。第一开关芯片2与控制芯片4贴合于导 线架1,且控制芯片4通过打线的方式电连接到第一开关芯片2的各极与导线 架1。由于各元件以平铺的方式构成开关元件封装结构,因此在功率转换器的 电路上所占的面积较大,无法有效地提升整体电路的功率密度。另外一方面, 由于第一开关芯片2运作而高频切换导通与关断时会产生高频噪声。但是,第 一开关芯片2与控制芯片4由于控制与侦测需求,连接彼此之间的打线又无法 相互隔离,因此无法有效地避免第一开关芯片2通电而运作时的噪声通过磁场 去干扰控制芯片4的作动。

4.所以,如何设计出一种可避免磁场干扰的芯片堆叠结构,以避免第一开关 芯片通电而运作时的噪声通过磁场去干扰控制芯片的作动,且降低开关元件封 装结构配置于电路板上的面积,乃为本案创作人所欲行研究的一大课题。

技术实现要素:

5.为了解决上述问题,本发明提供一种可避免磁场干扰的芯片堆叠结构,以 克服现有技术的问题。因此,本发明的芯片堆叠结构包括导线架、第一开关芯 片、导电夹片及控制芯片。导线架包括芯片基座与接地引脚,接地引脚传递接 地电位。第一开关芯片包括第一汲极,第一源极,以及第一闸极;第一源极与 第一闸极配置于第一开关芯片的第一面,且第一汲极配置于第一开关芯片的第 二面,第一汲极电连接该芯片基座。导电夹片包括导线架端与芯片端,且芯片 端包括第一面与反向于第一面的第二面,第一面电连接该第一源极,且导线架 端电连接接地引脚。控制芯片包括结合面与接点面,结合面耦接第二面,接点 面包括第一闸极接点,第一闸极接点电连接第一闸极。其中,结合面贴合第二 面。

6.于一实施例中,更包括第一导电层,第一导电层电连接第一汲极与芯片基 座,第一导电层选自焊锡、导电胶及金属胶带的至少其中之一。

7.于一实施例中,更包括第二导电层,第二导电层电连接第一源极与第一面, 第二导电层选自焊锡、导电胶及金属胶带的至少其中之一。

8.于一实施例中,控制芯片更包括电信号接点。电信号接点配置于接点面, 且电信号接点电连接导线架、第一开关芯片及导电夹片的其中之一。

9.于一实施例中,第一面完全覆盖第一源极,且第一闸极接点通过打线电连 接第一

闸极。

10.于一实施例中,结合面的第一表面积小于第二面的第二表面积。

11.于一实施例中,更包括第二开关芯片。第二开关芯片包括第二汲极,第二 源极,以及第二闸极,第二源极与第二闸极配置于第二开关芯片的第三面,且 第二汲极配置于第二开关芯片的第四面;第三面贴合第二面,且第一汲极电连 接第二源极。

12.为了解决上述问题,本发明提供一种可避免磁场干扰的芯片堆叠结构,以 克服现有技术的问题。因此,本发明的芯片堆叠结构包括导线架、第一开关芯 片、导电夹片及控制芯片。导线架包括芯片基座与接地引脚,接地引脚传递接 地电位。第一开关芯片包括第一汲极,第一源极,以及第一闸极;第一源极与 第一闸极配置于第一开关芯片的第一面,且第一汲极配置于第一开关芯片的第 二面,第一汲极电连接该芯片基座。导电夹片包括导线架端与芯片端,且芯片 端包括第一面与反向于第一面的第二面,第一面电连接该第一源极,且导线架 端电连接接地引脚,导电夹片覆盖部分第一源极,第一源极具有未被导电夹片 所覆盖的源极外露区。控制芯片包括结合面与接点面,结合面耦接第二面,接 点面包括第一闸极接点,第一闸极接点电连接第一闸极。其中,结合面贴合于 源极外露区。

13.于一实施例中,更包括第一导电层,第一导电层电连接第一汲极与该芯片 基座,第一导电层选自焊锡,导电胶及金属胶带的至少其中之一。

14.于一实施例中,更包括第二导电层黏合第一源极、控制芯片的结合面、与 导电夹片的第一面,第二导电层选自焊锡、导电胶及金属胶带的至少其中之一, 而可电连接该第一源极与该导电夹片。

15.于一实施例中,控制芯片更包括电信号接点。电信号接点配置于接点面, 且电信号接点电连接导线架、第一开关芯片及导电夹片的其中之一。

16.于一实施例中,第一面未完全覆盖第一源极,且第一闸极接点通过打线电 连接第一闸极。

17.于一实施例中,结合面的第一表面积小于第二面的第二表面积。

18.于一实施例中,更包括第二开关芯片。第二开关芯片包括第二汲极,第二 源极,以及第二闸极,第二源极与第二闸极配置于第二开关芯片的第三面,且 第二汲极配置于第二开关芯片的第四面;第三面贴合第二面,且第一汲极电连 接第二源极。

19.本发明的主要目的及功效在于,控制模块于换向期间观测并记录负载端电 压的磁通偏移量,且于闸流体成功关断后,调整直流交流转换电路所输出的第 三电压来对磁通进行补偿,以维持磁通平衡而达到抑制涌浪电流的功效。

20.为了能更进一步了解本发明为达成预定目的所采取的技术、手段及功效, 请参阅以下有关本发明的详细说明与附图,相信本发明的目的、特征与特点, 当可由此得一深入且具体的了解,然而所附图式仅提供参考与说明用,并非用 来对本发明加以限制者。

附图说明

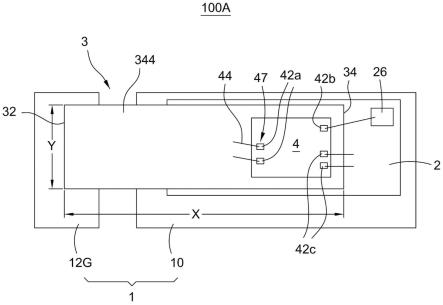

21.图1为现有的开关元件封装结构;

22.图2为本发明可避免磁场干扰的芯片堆叠结构第一实施例的侧视图;

23.图3为本发明可避免磁场干扰的芯片堆叠结构第一实施例的俯视图;

24.图4为本发明可避免磁场干扰的芯片堆叠结构第二实施例的侧视图;

25.图5为本发明可避免磁场干扰的芯片堆叠结构第三实施例的侧视图;

26.图6为本发明可避免磁场干扰的芯片堆叠结构第三实施例的俯视图;及

27.图7为本发明可避免磁场干扰的芯片堆叠结构第四实施例的侧视图。

28.其中,附图标记:

29.100a、100b、100c、100d

…

芯片封装件

[0030]1…

导线架

[0031]

10、10a

…

芯片基座

[0032]

12g

…

接地引脚

[0033]

12

…

引脚

[0034]2…

第一开关芯片

[0035]

22

…

第一汲极

[0036]

24

…

第一源极

[0037]

24a

…

源极外露区

[0038]

26

…

第一闸极

[0039]

2a

…

第一面

[0040]

2b

…

第二面

[0041]

3、3

’…

导电夹片

[0042]

32

…

导线架端

[0043]

34

…

芯片端

[0044]

342

…

第一面

[0045]

344

…

第二面

[0046]4…

控制芯片

[0047]

45

…

结合面

[0048]

47

…

接点面

[0049]

42

…

接点

[0050]

42a

…

接地接点

[0051]

42b

…

第一闸极接点

[0052]

42c

…

电信号接点

[0053]

42d

…

第二闸极接点

[0054]

44

…

打线

[0055]

52

…

第一导电层

[0056]

54

…

第二导电层

[0057]

56

…

第三导电层

[0058]

58

…

第四导电层

[0059]6…

第二开关芯片

[0060]

62

…

第二汲极

[0061]

64

…

第二源极

[0062]

66

…

第二闸极

[0063]

6a

…

第三面

[0064]

6b

…

第四面

[0065]

x

…

长度

[0066]y…

宽度

具体实施方式

[0067]

兹有关本发明的技术内容及详细说明,配合图式说明如下:

[0068]

请参阅图2为本发明可避免磁场干扰的芯片堆叠结构第一实施例的侧视 图,复配合参阅图1。芯片封装件100a主要是为开关元件封装结构,且芯片封 装件100包括导线架1(lead frame)、第一开关芯片2、导电夹片3(copper clip) 及控制芯片4。导线架1包括芯片基座10(die paddle)与多个引脚(lead finger), 多个引脚中包括了多种不同功能的引脚(例如但不限于i/o、侦测等),还包括 由一至多个引脚所组成的接地引脚12g,且接地引脚12g用以传递接地电位。 第一开关芯片2为第一晶体管开关(transistor switch),且包括第一汲极22、第 一源极24及第一闸极26。第一源极24与第一闸极26配置于第一开关芯片2 的第一面2a,且第一汲极22配置于第一开关芯片2的第二面2b,第一汲极 22电连接芯片基座10。值得一提,导线架1较佳的可以为合金材料,其主要是 可通过蚀刻、冲压等技术而形成特定结构。

[0069]

其中,第一开关芯片2为常规晶体管芯片。第一汲极22的电极面积大于第 一源极24与第一闸极26的电极面积,且第一源极24的电极面积大于第一闸极 26的电极面积。开关芯片制程要在晶圆表面形成源极、汲极、闸极的制程一般 会有离子布植(ion implantation)、沉积(deposition)、氧化(oxidation)、蚀刻(etch) 等,其为现有技术,在此不再加以赘述。由于本发明的第一开关芯片2使用常 规开关芯片(例如但不限于,汲极配置于开关芯片的第一面,且闸极与源极配置 于开关芯片的第二面),并非使用特规的开关架构(例如但不限于,源极配置于 开关芯片的第二面,且闸极与汲极配置于开关芯片的第一面,源极与汲极的位 置恰与本案相反),这二者的成本明显是常规开关芯片较为便宜。因此相较于使 用特规的开关架构,本发明使用常规开关芯片可以达到节省芯片成本的功效。

[0070]

导电夹片3包括导线架端32与芯片端34,且芯片端34包括第一面342与 反向于第一面342的第二面344。第一面342电连接第一源极24,且导线架端 32电连接接地引脚12g。控制芯片4包括结合面45与接点面47,结合面45 的一面贴合导电夹片3的第二面344,且接点面47配置有多个接点42。接点 42至少包括接地接点42a与第一闸极接点42b,且接地接点42a电连接导电夹 片3,以作为控制芯片4接地或侦测之用。第一闸极接点42b电连接第一闸极 26,以作为控制芯片4控制或侦测之用。较佳的,接地接点42a可通过打线 44(wire bond)电连接导电夹片3,且第一闸极接点42b也可通过打线44电连接 第一闸极26,以提供良好的讯号传输之用。其中,导电夹片3的材质较佳的可 以为铜,但也可以为具有良好导电性的金属材质。值得一提,于本发明的一实 施例中,芯片封装件100a主要是包括了单颗第一开关芯片2搭配控制芯片4 的架构,主要是可通过控制芯片4来控制第一开关芯片2的导通与关断。

[0071]

较佳地,第一汲极22的电极可直接地贴合芯片基座10,且在第一汲极22 与芯片基座10之间还可以包括第一导电层52,第一导电层52电连接该第一汲 极22与该芯片基座10。导电夹片3的第一面342可直接地贴合第一源极24的 电极,且具体的结构为第一面342完全

覆盖于第一源极24的另一面。同样地, 在第一面342与第一源极24的电极之间还可以包括第二导电层54,第二导电 层54电连接第一源极24与第一面342。第一导电层52与第二导电层54可以 选自焊锡、导电胶及金属胶带的至少其中之一,主要用以黏合第一汲极22的电 极与芯片基座10,以及第一面342与第一源极24的电极之用。相似地,导电 夹片3的导线架端32可直接地贴合接地引脚12g,且在导线架端32与接地引 脚12g之间也可以包括用以黏合的导电层。由于芯片封装件100a的堆叠结构 在高频大电力的路径(即由芯片基座10、第一汲极22、第一源极24、导电夹片 3与接地引脚12g所构成的路径),皆使用贴合且电连接的方式实施,在元件与 元件之间并不存在打线等线路,因此可以降低元件与元件连接的阻抗(即打线等 线路的等校阻抗)。

[0072]

进一步而言,当第一晶体管开关2因导通关断状态改变而产生电磁辐射时, 导电夹片3可屏蔽电磁辐射,以降低电磁辐射抵达控制芯片4的强度。具体的, 由于在第一开关芯片2通电而运作时(即被以特定频率控制导通/关断时),高频 大电力的噪声(noise)会通过磁场去干扰到控制芯片4的讯号侦测、回授补偿、 输出控制等弱电的讯号传递。由于控制芯片4的讯号传递非常敏感,稍有噪声 耦合时,会使得控制芯片4的讯号侦测、回授补偿、输出控制不准确而影响到 控制芯片4的特性,甚至会使得整个芯片封装件100a运作失效的风险。

[0073]

因此,高频大电力与弱电通常要相互隔离以避免发生上述的状况。然而, 由于本发明的控制芯片4与第一开关芯片2二者之间具有接地层(即导电夹片3 与第二导电层54所构成的接地层)的缘故,而相互隔开抑制电磁辐射干扰(即接 地层提供了较为稳定,且可抑制或缓冲噪声的电位),因此可以避免第一开关芯 片2通电而运作时的噪声通过磁场去干扰控制芯片4的作动。此外,由于本发 明的芯片封装件100a为各元件向上堆叠的结构,因此相较于现有的平面配置 结构,可以使得芯片封装件100a配置在电路板上所占的面积更小,有利于提 升整体电路的功率密度的优势。

[0074]

请参阅图3为本发明可避免磁场干扰的芯片堆叠结构第一实施例的俯视 图,复配合参阅图1~3。控制芯片更包括至少一电信号接点42c,电信号接点 42c配置于接点面47,且电信号接点42c电连接导线架1、第一开关芯片2及 导电夹片3的其中之一(图3以电连接第一开关芯片2为例),以作为控制芯片4 控制或侦测之用。其中,电信号接点42c也可通过打线44电连接导线架1、第 一开关芯片2及导电夹片3的其中之一,以分别提供良好的讯号传输或接地之 用。导电夹片3的第一面342完整的覆盖于第一源极24,且导电夹片3的长度 x与宽度y皆大于控制芯片4,使得控制芯片4的结合面45(同于接点面47)的 第一表面积小于导电夹片3的第二面344的第二表面积。在导电夹片3的导线 架端32的宽度y也较宽,因此可使用包括多个接地引脚12g的导线架1做兼 容性的贴合。

[0075]

由于导电夹片3具有较大的表面积,具有良好的散热效果,因此控制芯片 4可通过导电夹片3来进行散热,且第一开关芯片2除了可通过第一汲极22对 芯片基座10散热外,更可以通过第一源极24对导电夹片3进行散热。在第一 开关芯片2通电而运作时所产生大量的热,可以通过芯片基座10与导电夹片3 的大面积的接触而使第一开关芯片2通过这二面将热量迅速的传递出去。因此, 通过本发明导电夹片3具有较大的表面积的设计,可以大幅地提高芯片封装件 100a内部的散热效率。

[0076]

请参阅图4为本发明可避免磁场干扰的芯片堆叠结构第二实施例的侧视 图,复配

合参阅图1~3。本实施例的芯片封装件100b与图2的芯片封装件100a 差异在于,芯片封装件100b更包括第二开关芯片6。第二开关芯片6为第二晶 体管开关(transistor switch),且同于第一开关芯片2,也为常规晶体管芯片。第 二开关芯片6包括第二汲极62、第二源极64及第二闸极66,第二源极64与第 二闸极66配置于第二开关芯片6的第三面6a,且第二汲极62配置于第二开关 芯片6的第四面6b。第二汲极62电连接导线架1的芯片基座10a,且芯片基 座10a与芯片基座10彼此分离。

[0077]

第三面6a贴合第二面2b,且第一汲极22电连接第二源极64。其中,芯 片基座10、第二源极64及第一汲极22的电极彼此电连接,使这三者为共接点。 相似于图2,控制芯片4还包括第二闸极接点42d,第二闸极接点42d电连接第 二闸极66,以作为控制芯片4控制或侦测之用。值得一提,于本发明的一实施 例中,芯片封装件100b主要是包括了二颗开关芯片2、6搭配控制芯片4的架 构,主要是可通过控制芯片4来控制第一开关芯片2与第二开关芯片6的导通 与关断。尤其可用于例如但不限于,降压转换器,且芯片基座10a可用以接收 外部输入电压。

[0078]

较佳地,芯片基座10与第二源极64的电极分别部分覆盖第一汲极22的电 极,且在第二源极64与第一汲极22之间还可以包括第三导电层56。同样地, 第二汲极62的电极可直接地贴合芯片基座10a,且在第二汲极62与芯片基座 10a之间还可以包括第四导电层58。第三导电层56与第四导电层58可以选自 焊锡、导电胶及金属胶带的至少其中之一,主要做黏合之用。由于芯片封装件 100b的堆叠结构在高频大电力的路径,皆使用贴合且电连接的方式实施,在元 件与元件之间并不存在打线等线路,因此可以降低元件与元件连接的阻抗(即打 线等线路的等校阻抗)。同样地,第一晶体管开关与第二晶体管开关因导通关断 状态改变而产生电磁辐射时,导电夹片3可屏蔽电磁辐射,以降低电磁辐射抵 达控制芯片4的强度。

[0079]

请参阅图5为本发明可避免磁场干扰的芯片堆叠结构第三实施例的侧视 图,复配合参阅图1~4。本实施例的芯片封装件100c与图2的芯片封装件100a 差异在于控制芯片4的结合面45贴合第一源极24的电极,导电夹片3覆盖第 一源极24的部分,第一源极24具有未被导电夹片3所覆盖的源极外露区24a, 结合面45实质上贴合于源极外露区24a。由于在导电夹片3’的第一面342电 连接第一源极24的电极的情况下,第一源极24为接地电位。因此,可以如同 第一实施的芯片封装件100a,控制芯片4与第一开关芯片2通过这二者之间的 接地层(即导电夹片3’与第一源极24所构成的接地层)的缘故而相互隔开,同 样可以避免第一开关芯片2通电而运作时的噪声通过磁场去干扰控制芯片4的 作动。

[0080]

具体地,导电夹片3’的第一面342可直接地贴合第一源极24的另一面, 且第一面342并未完整的覆盖于第一源极24的电极(大致上仅覆盖第一源极24 的电极的一半面积),因此使得控制芯片4的结合面45可直接地贴合第一源极 24的部分电极。同样地,在第一面342、控制芯片4及第一源极24的电极之间 也可以包括第二导电层54,主要用以黏合第一面342、控制芯片4及第一源极 24的电极之用,第二导电层54并电连接第一源极24与导电夹片3。此外,由 于本发明的芯片封装件100c为各元件向上堆叠的结构,且省去了导电夹片3

’ꢀ

的向上堆叠空间,因此可以使得芯片封装件100c除了配置在电路板上所占的 面积更小外,且其高度可以略小于芯片封装件100c,可更加地有利于提升整体 电路的功率密度的优势。值得一提,于本发明的一实施例中,图5未提及的元 件及其结构皆相似于图2,在此不再加

以赘述。

[0081]

请参阅图6为本发明可避免磁场干扰的芯片堆叠结构第三实施例的俯视 图,复配合参阅图1~5。本实施例的芯片封装件100c与图2的芯片封装件100 差异在于导电夹片3’的第一面342大致上仅覆盖第一源极24的电极的一半面 积而未完整的覆盖于第一源极24的电极。然而,导电夹片3’的长度x与宽度 y仍然皆大于控制芯片4,使得控制芯片4的第一表面积仍小于导电夹片3’的 第二面344的第二表面积。控制芯片4可通过第一源极24至导电夹片3’的路 径来进行散热,且第一开关芯片2除了可通过第一汲极22对芯片基座10散热 外,更可以通过第一源极24对导电夹片3’进行散热。虽然以散热效率而言, 第一实施例较为优选,然而在第一开关芯片2通电而运作时所产生大量的热, 仍然可以通过芯片基座10与导电夹片3’的大面积的接触而使第一开关芯片2 通过这二面将热量迅速的传递出去。因此,同样可以达成提高芯片封装件100c 内部的散热效率的功效。值得一提,于本发明的一实施例中,图6未提及的元 件及其结构皆相似于图3,在此不再加以赘述。

[0082]

请参阅图7为本发明可避免磁场干扰的芯片堆叠结构第四实施例的侧视 图,复配合参阅图1~6。本实施例的芯片封装件100d与图4的芯片封装件100b 差异在于,芯片封装件100d的各个点位(例如但不限于第一开关芯片2、第二 开关芯片6等)可以通过打线的方式,相应地电连接引脚12。引脚12有别于接 地引脚12g,用于外部线路连接供i/o、侦测、控制等之用。以图7为例,第 二闸极66通过打线44电连接引脚12,以供外部线路连接使用。值得一提,于 本发明的一实施例中,图7未提及的元件及其结构皆相似于图4,在此不再加 以赘述。

[0083]

惟,以上所述,仅为本发明较佳具体实施例的详细说明与图式,惟本发明 的特征并不局限于此,并非用以限制本发明,本发明的所有范围应以下述的权 利要求范围为准,凡合于本发明权利要求范围的精神与其类似变化的实施例, 皆应包括于本发明的范畴中,任何熟悉该项技艺者在本发明的领域内,可轻易 思及的变化或修饰皆可涵盖在以下本案的专利范围。

[0084]

当然,本发明还可有其它多种实施例,在不背离本发明精神及其实质的情 况下,熟悉本领域的技术人员可根据本发明作出各种相应的改变和变形,但这 些相应的改变和变形都应属于本发明权利要求的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1