半导体结构和半导体结构的制备方法与流程

本技术涉及半导体制造,尤其涉及一种半导体结构和半导体结构的制备方法。

背景技术:

1、动态随机存储器(dynamic random access memory,简称dram)是常用的半导体存储器件,包括多个重复的存储单元。每个存储单元通常包括晶体管和电容器,晶体管的栅极与字线(word line,简称wl)相连、漏极与位线(bit line,简称bl)相连、源极与电容器相连。

2、dram存储器中设置有导电连接结构,导电连接结构可以是金属互连结构或接触插塞结构。其中,金属互连结构用于将不同存储单元的信号线连接,或者用于连接存储单元中不同的导电层。为适应dram存储器的尺寸不断微缩,相关技术中的导电连接结构的尺寸以及相邻导电连接结构之间的距离均相应地不断缩小。

3、然而,上述方案中的导电连接结构的寄生电容较大,导致其rc(电容电阻)延迟较为严重,影响dram存储器的存储性能。

技术实现思路

1、本技术提供一种半导体结构和半导体结构的制备方法,能够有效降低导电连接结构的寄生电容,缓解其rc延迟问题,优化存储器的存储性能。

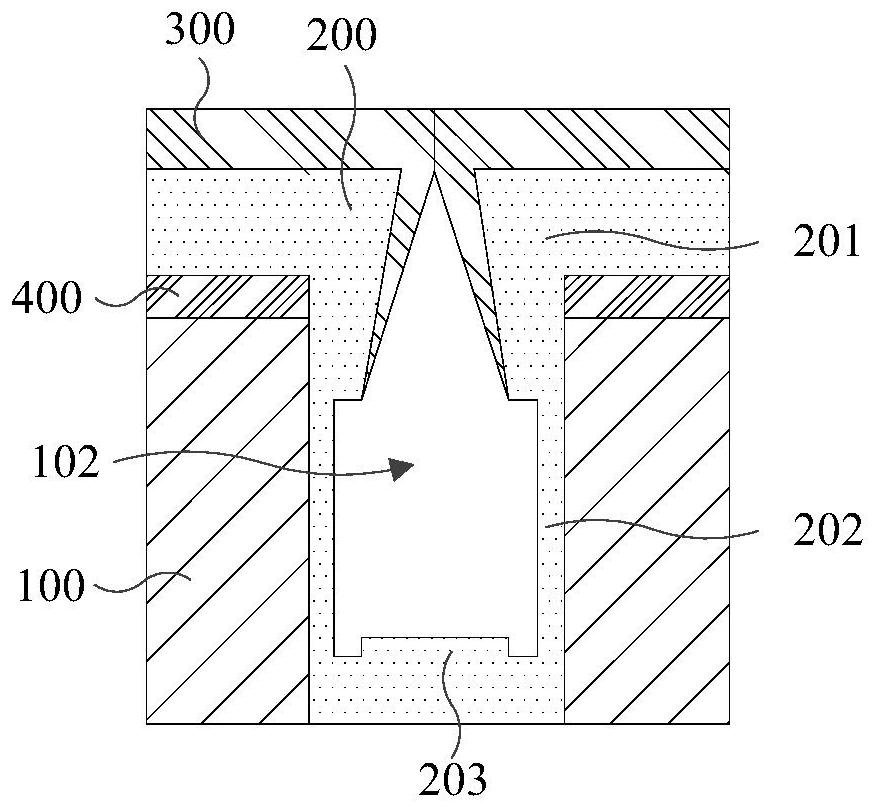

2、为了实现上述目的,第一方面,本技术提供一种半导体结构,包括导电层,导电层内具有孔道,孔道的内壁覆盖有第一介质层,靠近孔道的孔口一侧的第一介质层的厚度,大于远离孔口一侧的第一介质层的厚度;靠近孔口一侧的第一介质层上覆盖有第二介质层,第二介质层封堵孔口;

3、第一介质层和第二介质层内形成有气隙,远离孔口一侧的气隙的尺寸,大于靠近孔口一侧的气隙的尺寸。

4、在上述的半导体结构中,可选的是,位于孔道内的第一介质层包括第一部分和第二部分,第一部分靠近孔口,第二部分远离孔口;

5、第二介质层覆盖于第一部分上;

6、第一部分的厚度大于第二部分的厚度,位于第二部分内的气隙的尺寸大于位于第一部分内的气隙的尺寸。

7、在上述的半导体结构中,可选的是,靠近孔口一侧的第一部分的厚度,大于远离孔口一侧的第一部分的厚度;

8、且,第一部分的厚度沿远离孔口的方向逐渐减小。

9、在上述的半导体结构中,可选的是,靠近孔口一侧的第二介质层的厚度,大于远离孔口一侧的第二介质层的厚度;

10、且,第二介质层的厚度沿远离孔口的方向逐渐减小,位于第二介质层内的气隙的尺寸沿远离孔口的方向逐渐增大。

11、在上述的半导体结构中,可选的是,第二部分的厚度范围为5-10nm。

12、在上述的半导体结构中,可选的是,第一介质层包括第三部分,第三部分覆盖孔道的至少部分孔底,第三部分的厚度大于第二部分的厚度。

13、在上述的半导体结构中,可选的是,还包括第三介质层,第三介质层位于孔道的外部,第三介质层覆盖靠近孔口的导电层。

14、在上述的半导体结构中,可选的是,至少部分第一介质层位于孔道的外部,位于孔道外部的第一介质层覆盖第三介质层;

15、至少部分第二介质层位于孔道的外部,位于孔道外部的第二介质层覆盖第一介质层上。

16、第二方面,本技术提供一种半导体结构的制备方法,包括:

17、提供具有孔道的导电层;

18、形成第一介质层,第一介质层至少覆盖孔道的内壁,靠近孔道的孔口一侧的第一介质层的厚度,大于远离孔口一侧的第一介质层的厚度;

19、形成阻隔层,阻隔层至少覆盖靠近孔道的孔口一侧的第一介质层;

20、去除未被阻隔层覆盖的部分厚度的第一介质层;

21、去除阻隔层;

22、形成第二介质层,第二介质层至少覆盖靠近孔口一侧的第一介质层,并封堵孔道的孔口;

23、其中,第一介质层和第二介质层内形成有气隙,远离孔口一侧的气隙的尺寸,大于靠近孔口一侧的气隙的尺寸。

24、在上述的半导体结构的制备方法中,可选的是,形成阻隔层,包括:

25、通过物理气相沉积工艺形成阻隔层;

26、其中,靠近孔口一侧的阻隔层的厚度,大于远离孔口一侧的阻隔层的厚度,且,阻隔层的厚度沿远离孔口的方向逐渐减小。

27、在上述的半导体结构的制备方法中,可选的是,去除未被阻隔层覆盖的部分厚度的第一介质层,包括:

28、采用第一刻蚀液通过化学刻蚀工艺去除未被阻隔层覆盖的部分厚度的第一介质层,第一刻蚀液对阻隔层和第一介质层的选择刻蚀比为1:10;

29、去除阻隔层,包括:

30、采用第二刻蚀液通过化学刻蚀工艺去除阻隔层,第二刻蚀液对阻隔层和第一介质层的选择刻蚀比为12:1。

31、在上述的半导体结构的制备方法中,可选的是,第一刻蚀液为氢氟酸溶液;氢氟酸溶液中,氢氟酸与水的比例范围为200:1-300:1,第一刻蚀液的刻蚀制程时间为100-140s;

32、和/或,第二刻蚀液为氨水、双氧水和水的混合物,其中,氨水、双氧水和水的比例为1:4:130,第二刻蚀液的刻蚀制程时间为40-80s。

33、在上述的半导体结构的制备方法中,可选的是,形成第一介质层之前,还包括:

34、形成第三介质层,第三介质层位于孔道的外部,且覆盖靠近孔口的导电层;

35、其中,至少部分第一介质层位于孔道的外部,位于孔道外部的第一介质层覆盖第三介质层;

36、形成阻隔层,包括:

37、至少部分阻隔层位于孔道的外部,位于孔道外部的阻隔层覆盖第一介质层;

38、其中,至少部分第二介质层位于孔道的外部,位于孔道外部的第二介质层覆盖第一介质层。

39、在上述的半导体结构的制备方法中,可选的是,第一介质层包括靠近孔口的第一部分和位于孔道的孔底的第三部分;

40、形成阻隔层,包括:阻隔层覆盖第一部分和第三部分;

41、去除未被阻隔层覆盖的部分厚度的第一介质层,包括:去除第一介质层中除第一部分和第三部分之外的部分厚度的第一介质层,并形成第一介质层的第二部分;

42、其中,第一部分和第三部分的厚度,均大于第二部分的厚度。

43、在上述的半导体结构的制备方法中,可选的是,形成第一介质层,包括:

44、通过化学气相沉积工艺形成第一介质层;

45、其中,靠近孔口一侧的第一部分的厚度,大于远离孔口一侧的第一部分的厚度,且第一部分的厚度沿远离孔口的方向逐渐减小。

46、本技术提供的半导体结构和半导体结构的制备方法,在半导体结构中,通过提供具有孔道的导电层,该导电层可以传递信号,以实现该半导体结构的导电连接功能,导电层中的孔道能够用于形成后续的气隙。通过在孔道的内壁设置第一介质层和第二介质层,第二介质层封堵孔口,以在第一介质层和第二介质层内形成气隙。通过将靠近孔道的孔口一侧的第一介质层的厚度,大于远离孔口一侧的第一介质层的厚度,以使远离孔口一侧的气隙的尺寸,大于靠近孔口一侧的气隙的尺寸。并且在半导体的制备方法中,利用阻隔层进行掩膜刻蚀,去除部分厚度的第一介质层,以使远离孔口一侧的至少部分第二介质层的厚度较小。这样,可以有效增加半导体结构中的气隙尺寸,从而缓解半导体结构的寄生电容以及rc延迟的问题,当该半导体结构应用于存储器中时,也可以相应地优化存储器的存储性能。

47、本技术的构造以及它的其他发明目的及有益效果将会通过结合附图而对优选实施例的描述而更加明显易懂。

- 还没有人留言评论。精彩留言会获得点赞!