用于高压操作的GAALDMOS结构的制作方法

本公开涉及半导体领域,尤其涉及用于高压操作的gaa ldmos结构。

背景技术:

1、在过去的几十年中,集成电路(ic)制造工业经历了指数级增长。随着ic的发展,功能密度(即,每单位芯片面积的互连器件的数量)普遍增加,而几何尺寸(即,可以创建的最小组件)普遍减小。另一项发展是bcd技术,它结合了双极结型晶体管(bjt)技术、互补金属氧化物半导体(cmos)技术和双扩散金属氧化物半导体(dmos)技术。bcd技术允许在单个半导体芯片上形成逻辑器件、模拟器件和功率器件。由于bcd技术需要工艺兼容性且需要限制工艺步骤激增,因此带来了挑战。

技术实现思路

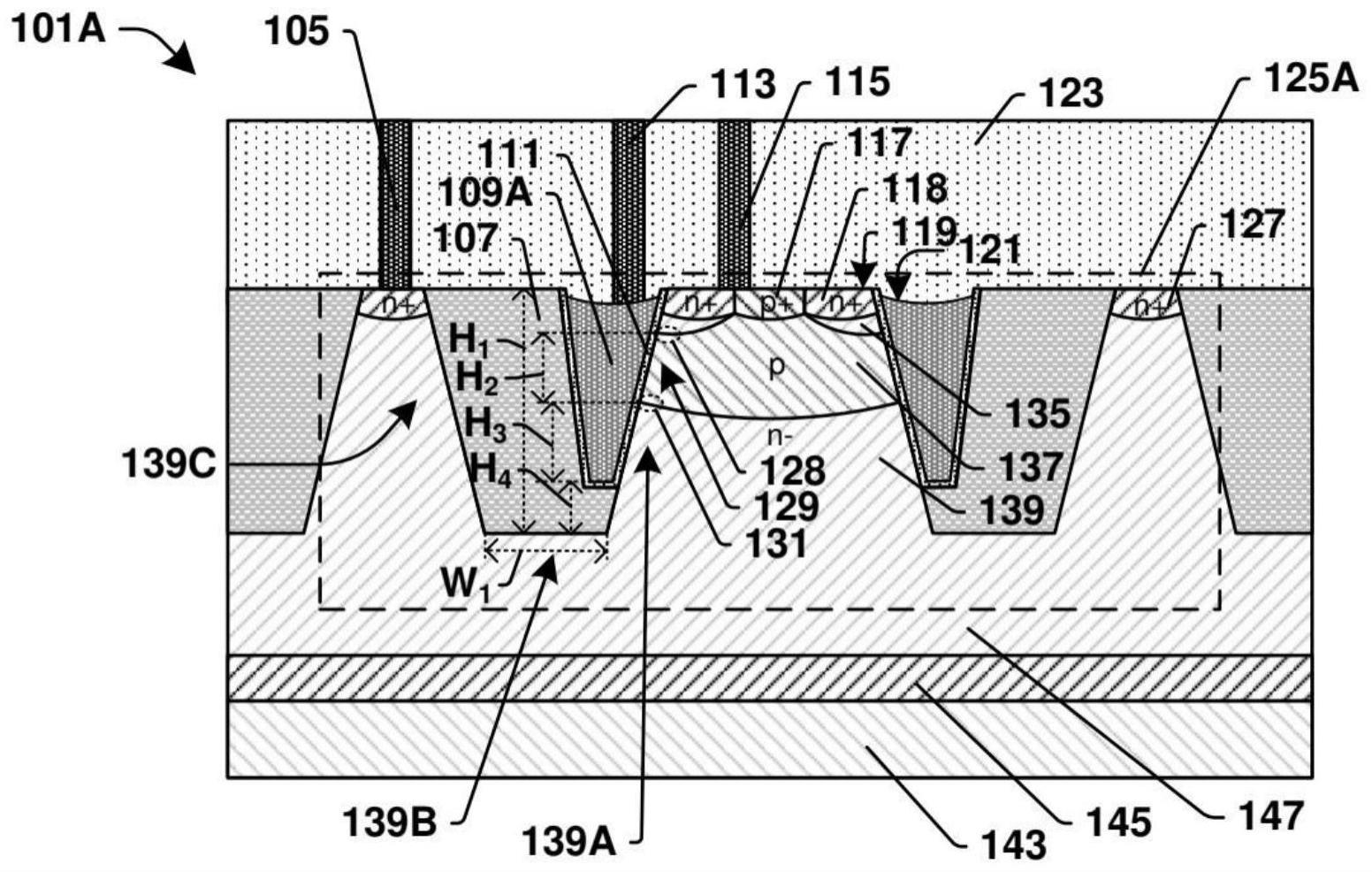

1、本公开的第一方面涉及一种集成电路(ic)器件,包括:半导体衬底,具有上表面;以及晶体管,包括环形栅极电极、栅极电介质层、第一源极/漏极区域、第二源极/漏极区域、以及沟道;其中,所述第一源极/漏极区域、所述第二源极/漏极区域和所述沟道是所述半导体衬底的掺杂区域;所述环形栅极电极与所述沟道相隔所述栅极电介质层的宽度;所述环形栅极电极低于所述上表面;所述沟道被所述环形栅极电极围绕;并且所述第二源极/漏极区域在所述环形栅极电极的外侧。

2、本公开的第二方面涉及一种集成电路(ic)器件,包括:浅沟槽隔离(sti)区域;以及晶体管,具有内侧端子区域、沟道、外侧端子区域、栅极电极和漂移区域;其中,所述内侧端子区域高于所述沟道;所述栅极电极围绕所述沟道;所述sti区域围绕所述栅极电极;所述外侧端子区域在所述sti区域的外侧;所述漂移区域开始于所述沟道的下方,在所述sti区域的下方行进,并且延伸到所述外侧端子区域;所述内侧端子区域和所述外侧端子区域中的一者用作源极;所述内侧端子区域和所述外侧端子区域中的另一者用作漏极;所述内侧端子区域、所述外侧端子区域和所述漂移区域是具有第一掺杂类型的半导体区域;并且所述沟道是具有第二掺杂类型的半导体区域,所述第二掺杂类型与所述第一掺杂类型相反。

3、本公开的第三方面涉及一种用于形成半导体器件的方法,包括:在半导体衬底内形成环形浅沟槽隔离(sti)区域;蚀刻掉所述环形sti区域的一部分以形成环形沟槽,所述环形沟槽包括由所述环形sti区域提供的外侧壁和由所述半导体衬底提供的内侧壁;在所述内侧壁上形成栅极氧化物;用导电材料来填充所述环形沟槽;对所述半导体衬底的具有第一掺杂类型并设置在所述环形sti区域内的部分进行掺杂,以形成具有第二掺杂类型的阱,其中,所述第二掺杂类型与所述第一掺杂类型相反,并且所述阱的深度小于所述环形sti区域的深度;以及对所述半导体衬底的在所述阱正上方的部分进行掺杂,以形成具有所述第一掺杂类型的重掺杂区域。

技术特征:

1.一种集成电路(ic)器件,包括:

2.根据权利要求1所述的ic器件,还包括:

3.根据权利要求2所述的ic器件,其中,所述环形栅极电极的底部比所述环形sti区域的底部高一段距离,该距离大于所述栅极电介质层的宽度。

4.根据权利要求2所述的ic器件,其中,所述环形栅极电极的底部的深度和所述环形sti区域的底部的深度相差一个量,该量小于或等于所述栅极电介质层的宽度。

5.根据权利要求2所述的ic器件,其中,所述环形sti区域的外侧壁以一个角度倾斜,该角度是所述环形栅极电极的内侧壁的倾斜角度的镜像。

6.根据权利要求2所述的ic器件,其中:

7.根据权利要求1所述的ic器件,其中,所述环形栅极电极的顶部低于所述上表面。

8.根据权利要求1所述的ic器件,还包括:

9.一种集成电路(ic)器件,包括:

10.一种用于形成半导体器件的方法,包括:

技术总结

本公开涉及用于高压操作的GAA LDMOS结构。横向双扩散金属氧化物半导体(LDMOS)型的栅极全环绕(GAA)高压晶体管具有设置为低于半导体衬底的表面的环形栅极电极。该环形栅极电极围绕由第一源极/漏极区域、主体区域和扩散区域形成的竖直沟道。第一源极/漏极区域在最上面,主体区域在中间,扩散区域在下方。环形浅沟槽隔离(STI)区域围绕环形栅极电极。扩散区域从环形栅极电极的内侧开始,在环形栅极电极和环形STI区域下方延伸,并且上升到环形STI区的外侧以与第二源极/漏极区域相连。与以其他方式提供等效功能的非对称NMOS晶体管相比,这种结构允许间距缩小40%或者线性驱动电流翻倍。

技术研发人员:吴宏祥,吴国铭

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!