抓取对象引脚的方法、测试芯片及其设计方法、系统与流程

1.本发明属于半导体设计和生产技术领域,尤其涉及一种基于模板抓取对象引脚的方法及相应的测试芯片设计方法、设计系统、测试芯片。

背景技术:

2.目前在半导体设计和生产中用户一般通过对测试芯片中的测试结构进行测试,来推断产品芯片中相应器件的状态。测试芯片的设计中一个重要步骤是抓取关键器件的引脚,以进行后续绕线连接形成测试通路。目前的自动抓取引脚的做法较为简单,一般只针对mosfet或其串、并联后的测试对象,而对于没有直接连接关系或其它连接关系的多个mosfet则不能识别,对于diode、bjt、varactor等较为复杂的器件或不属于器件的测试对象,则更是无法自动识别。

3.为了解产品芯片中特定器件的失效与否以及电学特性是否符合要求,需要设计能在真实物理环境下测试关键器件电性参数的测试芯片,这类测试芯片一般是通过在保证产品芯片前道、中道工艺层不变的情况下,将连接层与后道工艺层改造成测试芯片,以提供测试器件的真实物理测试环境。在这类测试芯片的设计过程中,为了将更多类型的器件或更复杂的测试结构引入测试芯片,目前通用的自动识别器件引脚的方法已无法实现。

4.因此目前十分需要研究一种对待测对象的类型以及引脚个数没有限制的抓取目标器件引脚方法及相应的测试芯片设计方法、设计系统、测试芯片,能够适用于关键器件引脚的抓取,进而设计测试芯片,能够在真实物理测试环境进行测试,测试效果更好,以此进一步推动半导体设计和生产技术的深入发展及广泛应用。

技术实现要素:

5.本发明是为解决上述现有技术的全部或部分问题,本发明一方面提供了一种基于模板抓取对象引脚的方法,适用于对待测对象的类型以及引脚个数没有限制的抓取目标器件引脚。本发明的另外一个方面提供了一种测试芯片设计方法,结合本发明的抓取对象引脚的方法进行测试芯片的设计。本发明还提供了测试芯片设计系统及测试芯片。

6.本发明一方面提供的一种基于模板抓取对象引脚的方法,包括:获取版图文件,确定版图中待抓取引脚的对象,将其记为目标对象,获取目标对象的对象模板;所述对象模板包括匹配层和绕线层,所述匹配层是用于进行图形匹配的图层,所述绕线层是用于将对象的端子引出的连接线图层;基于目标对象的对象模板在版图中抓取目标对象的引脚,包括:利用所述对象模板的匹配层在版图中进行匹配查找,查找到与所述匹配层的图形相匹配的图形后,将所述对象模板的绕线层进行复制后添加至所述版图中的对应位置,用于将目标对象的端子引出,实现对目标对象引脚的抓取。通过获取目标对象的对象模板,能够使用所述对象模板来识别并抓取目标对象的引脚,步骤简洁,能够根据测试要求进行连接并定义引脚,突破了现有技术中通用的自动识别器件引脚的方法对所述目标对象的类型以及引脚个数的限制,实现了芯片设计中对没有直接连接关系或其它连接关系的多个mosfet进行识

别抓取,以及对diode、bjt、varactor等较为复杂的器件或不属于常规器件的对象进行有效的自动识别抓取。

7.确定目标对象后,还获取目标对象在版图中的定位点,利用所述对象模板的匹配层在版图中进行匹配查找时,是在版图中以所述定位点为中心的预设匹配范围内进行匹配查找。

8.获取目标对象在版图中的定位点的方法包括:预设用于匹配识别所述目标对象的图层记为标记层或图形记为特征图形;其中,所述标记层是指:用于匹配识别所述目标对象的特征图层,或者收集有所述目标对象定位点坐标信息的标识层;利用目标对象的标记层或者特征图形在版图中匹配识别所述目标对象,并获取所述目标对象的定位点坐标信息。

9.所述对象模板中还包括图层:引脚标记层(pin label layer),用于标记引脚的电极。通过包括引脚标记层能够标记引脚的电极,在后续抓取引脚的结果中可以明确引脚的电极是源极、漏极、栅极或体极,更利于有效开展后续相关工艺。

10.所述获取对象模板的方式包括:制作对象模板;制作方法包括:在版图中定位对象,并截取所述对象的版图作为模板的原型版图;对所述原型版图进行简化处理得到所述对象模板。通过先行定位所述对象,从所述版图中截取所述对象的版图作为模板的原型版图进行处理后制作得到所述对象模板,进一步简化了版图处理,利于提高设计效率。获取对象模板也可以直接导入之前已制作好的对象模板重复使用,并不是通过重新制作获得,在此并不限定。

11.所述截取所述对象的版图作为模板的原型版图,包括:判断所述对象是否为所述版图中的图元:若是,则将所述图元的版图截取作为所述原型版图;若不是,则将所述对象及其预设范围内的图形一起截取作为所述原型版图。版图中的图元是通过引用基本图元或图元的方式,以及阵列基本图元或图元的方式创建;所述基本图元是指图层中的多边形结构图形。

12.对所述原型版图进行简化处理,包括:删除所述原型版图中的后段绕线图层,再添加若干连接线,即获得若干新增绕线层,以将所述对象的端子引出作为引脚;所述新增绕线层中的连接线包括与所述原型版图中连接线相同路径的连接线和/或新创建的连接线(尽量沿用所述原型版图中绕线);利用所述引脚标记层(pin label layer)标记所述引脚的电极;在所述原型版图中确定若干(图形特征有辨识度的)图层作为匹配层,并删除所述匹配层中不完整的图形后,获得所述对象模板;其中,所述不完整的图形是指存在从所述版图中截取所述原型版图时被截断的基本图元。通过对所述原型版图进行简化处理,进一步简化版图处理,优化设计效率。

13.还有的情况中,对所述原型版图进行简化处理,还包括:获得所述对象模板之后,删除所述对象模板中除了所述匹配层、所述新增绕线层和所述引脚标记层之外的其余图层。

14.将所述对象模板中的绕线层进行复制后添加至所述版图中的对应位置后,还利用所述引脚标记层定义所述目标对象引脚的电极。

15.与所述匹配层的图形相匹配的图形,是指与所述匹配层的图形完全一致的图形或者所述匹配层的图形在相互正交的两个方向中任一方向上镜像后的图形。所述匹配层的图形在相互正交的两个方向中任一方向上镜像后的图形可以是直角坐标系中,所述匹配层的

图形x轴方向上镜像后的图形,或者所述匹配层的图形在y轴方向上镜像后的图形。

16.利用所述对象模板的匹配层,在版图中以所述定位点为中心的匹配范围(template match search range)内进行图形匹配查找;具体步骤包括:步骤a):设置匹配参数:在所述对象模板的匹配层中设置匹配点的坐标(坐标(devicex,devicey)),以及预设匹配范围(template match search range)和匹配坐标误差容许范围(template match coordinate tolerance);步骤b):将所述匹配点对齐版图中的所述定位点,利用所述对象模板的匹配层进行图形匹配:若匹配成功,则完成匹配查找;若匹配失败,则继续后续步骤;步骤c):将所述匹配点在以所述定位点为中心的匹配坐标误差容许范围内移动,使所述匹配层在以所述定位点为中心的匹配范围内进行图形匹配:若匹配成功,则完成匹配查找;若匹配失败,则继续后续步骤;步骤d):判断是否调整匹配参数:若调整匹配参数(比如扩大匹配范围和匹配坐标误差容许范围),则至步骤b)继续执行;若不调整匹配参数,则结束本次匹配查找。

17.基于所述对象模板抓取目标对象引脚之后(通过将所述对象模板的绕线层进行复制后添加至所述版图中的对应位置,用于将所述目标对象的端子引出,以抓取所述目标对象的引脚后),还自动抓取所述目标对象的剩余引脚(比如晶体管只通过所述对象模板抓取源极、漏极和栅极引脚,体极引脚则采用自动抓取的做法),以完成对所述目标对象所有引脚的抓取。在抓取所述目标对象的引脚后,还能根据实际应用的具体需要,能够灵活的判断是否已经抓取了全部所需的引脚,如果不是则能进一步抓取其他引脚,比如晶体管通过所述对象模板抓取了源极、漏极和栅极引脚,根据实际情况选择是否同时抓取对应的体极(body)引脚,如果需要,则采用一般的自动抓取的做法继续抓取对应的体极(body)引脚,以抓取全部的引脚。将通过所述对象模板抓取引脚与自动抓取引脚相结合,更能灵活的适用于生产实际,能够更好地符合具体应用的需要。

18.本发明另一方面提供的一种测试芯片设计方法,包括:步骤s1.输入产品芯片版图,基于图形化解读获取所述产品芯片版图中的对象及其对象信息;其中,所述产品芯片版图包括前段图层和后段图层;步骤s2.创建测试芯片的后段图层,包括:在产品芯片上排布若干焊盘;筛选出若干对象作为目标对象;抓取目标对象的引脚;为所述目标对象的引脚分配焊盘,并绕线实现目标对象的引脚到所分配焊盘的连接;其中,所述抓取目标对象的引脚,包括利用本发明一方面提供的基于模板抓取引脚的方法进行获取;步骤s3.将所述产品芯片的前段图层和所述步骤s2创建的测试芯片的后段图层进行合并连接,获得所述测试芯片的版图。

19.如此设计的测试芯片适用于对产品芯片关键器件或热点图形在真实物理环境下的测试,通过利用本发明的基于模板抓取引脚的方法抓取目标对象的引脚,能实现各种不同类型的对象引脚的自动抓取,既能完成关键器件引脚的抓取从而设计测试芯片的版图用于制造测试芯片,又能得到测试芯片用于在真实物理测试环境进行测试,测试结果更可靠,且测试芯片的制造工艺得到进一步的优化,利于测试芯片的制造水平和良率的完善,对芯片产品成品率的大幅提升具有积极的推动作用。

20.所述步骤s1中,所述图形化解读包括:利用预设的特征图形,根据特征图形匹配识别对应的对象,并采用量化表征对象信息;所述对象包括器件(device)和热点图形(hot spot),热点图形(hot spot)是易产生工艺缺陷(比如光刻工艺缺陷)的结构图形。通过图形

化解读产品芯片的版图能够根据不同测试需求通过匹配预设的特征图形自动快速识别对象并提取所述目标对象。

21.所述步骤s1中,所述对象信息是指能影响对象性能的特征信息,包括对象特征图形的信息、对象特征图形与其周围图形之间的环境信息。所述环境信息例如相对距离信息等。

22.所述测试芯片设计方法还建立有对象数据库,用于存储所述步骤s1中获取的对象及对象信息;所述对象信息包括:对象的名称、位置坐标,以及量化表征的特征信息。

23.所述步骤s2中,在所述产品芯片上排布若干焊盘包括:在测试芯片上,以两个焊盘组在第一方向上间隔交错摆放焊盘的方式摆放多个焊盘组,形成若干个沿着第一方向的焊盘序列;在所述焊盘序列的两侧区域,分别确定所述焊盘序列中焊盘的可选区域,用于焊盘连接其可选区域内的测试对象引脚以形成测试通路;其中,所述焊盘组为焊盘阵列;所述第一方向是指焊盘组中焊盘阵列的行方向或列方向。

24.所述筛选出若干对象作为目标对象包括:仅在所述可选区域内的对象中进行筛选。

25.所述测试芯片设计方法预设有若干项筛选规则;所述步骤s2中,筛选出若干对象作为目标对象还包括为不同的对象选择适用的筛选规则进行筛选得到目标对象。

26.根据所述测试芯片的测试需求设置选择的筛选规则的优先级顺序,并按所述优先级顺序应用所述筛选规则以筛选出符合的对象作为目标对象。

27.所述目标对象的引脚包括:所述目标对象的端子、以及将所述端子引出的若干连接线;所述将所述端子引出的若干连接线包括与所述产品芯片版图中连接线相同路径的连接线和/或新创建的连接线。

28.所述步骤s2中,为所述引脚分配所述焊盘包括:在符合可绕线性原则的若干焊盘中选择距离引脚最近的焊盘进行分配。可绕线性原则包括所述焊盘对于所述引脚可绕线,以及所有引脚的整体可绕线。

29.所述步骤s2中,为所述引脚分配所述焊盘包括:将构成所述焊盘序列的间隔交错摆放的两个焊盘组分别记为第一焊盘组和第二焊盘组,将所述焊盘序列一侧的可选区域记为奇数区域,另一侧的可选区域记为偶数区域,所述奇数区域为所述第一焊盘组的可选区域,所述偶数区域为所述第二焊盘组的可选区域;将位于所述焊盘序列的奇数区域中的目标对象的引脚分配给所述焊盘序列中第一焊盘组的焊盘,将位于所述焊盘序列的偶数区域中的目标对象的引脚分配给所述焊盘序列中第二焊盘组的焊盘。

30.所述测试芯片设计方法预设有若干绕线规则;所述步骤s2中,绕线是根据不同的引脚选择对应的绕线规则进行绕线。不同的所述引脚例如一般引脚、对电流引起压降敏感的引脚等不同的引脚。步骤s2中将所述目标对象的引脚直连焊盘,有利于测试芯片覆盖更多的测试项和测试条件。

31.所述步骤s2中还包括:删除所述产品芯片的后段图层。

32.所述步骤s3之后,还对步骤s3获得的所述测试芯片的版图进行验证,验证合格则完成对所述测试芯片的设计。

33.所述验证包括drc验证和lvs验证;所述验证全部合格则完成对所述测试芯片的设计。通过drc验证是否符合设计规则,通过lvs验证确保后段绕线的连接符合要求,验证全部

合格则设计的所述测试芯片能够更好地满足监测产品芯片良率和性能的高级定制需求。

34.本发明还提供的测试芯片设计系统,包括存储设备;所述存储设备中存储有多条指令,所述指令适于由处理器加载并执行本发明的所述的测试芯片设计方法。

35.本发明还提供的测试芯片,采用本发明的测试芯片设计方法进行设计得到。在保证产品芯片前道、中道工艺层(即产品芯片的前段图层feol)不变的情况下,通过改造产品芯片的连接层与后道工艺层(即创建新的后段图层beol),可以获得测试芯片的版图,如此设计的测试芯片适用于对产品芯片在真实物理环境下的测试,设计得到的测试芯片具有与产品芯片中器件或热点图形面临的物理环境相同的测试结构的测试芯片能够大幅优化测试准确性。

36.与现有技术相比,本发明的主要有益效果:1、本发明的基于模板抓取对象引脚的方法,使用模板来识别并抓取目标对象的引脚,设计灵活,可以灵活地根据具体测试要求进行连接并定义引脚,对目标对象的类型以及引脚个数也没有限制;不但能对没有直接连接关系或其它连接关系的多个mosfet进行识别抓取,还能对diode、bjt、varactor等较为复杂的器件或不属于器件的各种类型的测试对象进行自动识别抓取。为将更多类型的器件或更复杂的测试结构引入测试芯片提供了可行有效的解决方案2、本发明的一种测试芯片设计方法,因采用本发明的基于模板抓取对象引脚的方法抓取目标对象的引脚,能够设计传统的通用的自动识别器件引脚的方法所无法实现的引入了更多类型的器件及更复杂的测试结构的测试芯片,步骤简洁,测试结果可靠,极大推动了测试芯片的制造工艺的进一步优化,以及芯片产品成品率的大幅提升。

37.3、本发明提供的测试芯片设计系统、测试芯片具有相应的优势,为推动实际测试工艺水平的进一步发展、产品生产质量的持续优化提供了积极有效的解决方案。

附图说明

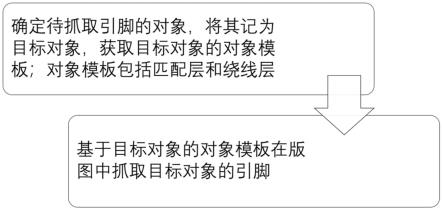

38.图1为本发明实施例一的抓取引脚的方法过程示意图。

39.图2为本发明实施例一的模板的原型版图示意图。

40.图3为本发明实施例一中对原型版图进行删除后段绕线层后的版图示意图。

41.图4为本发明实施例一中对图3所示意的版图进行重新绕线并接出引脚的版图示意图。

42.图5为本发明实施例一的最终的对象模板示意图。

43.图6为本发明实施例三的测试芯片设计方法过程示意图。

44.图7为本发明实施例三中在原始产品芯片上排布焊盘后的示意图。

45.图8为本发明实施例三的对象数据库中存储的mosfet的对象信息表示意图。

46.图9为本发明实施例三的mosfet的对象参数示意图。

47.图10为本发明实施例四中两个焊盘组交错摆放过程示意图。

48.图11为本发明实施例四中焊盘组与可选区域关系示意图。

49.图12为本发明实施例四中筛选中的目标mosfet信息表示意图。

50.图13为本发明实施例四中的目标mosfet获取引脚过程的示意图。

51.图14为本发明实施例四中为引脚分配焊盘的过程示意图。

具体实施方式

52.本发明的上述和/或附加的方面和优点从结合下面附图对实施例的描述中将变得明显和容易理解。在下述实施例中采用特定次序描绘了实施例的操作,这些次序的具体描述是为了更好的理解实施例中的细节以全面了解本发明,附图中的流程图和框图,图示出按照本发明实施例的方法可能实现的操作过程,不能以此限定本发明的范围。

53.实施例一本发明实施例一中,如图1所示,基于模板抓取对象引脚的方法,具体包括:获取版图文件,确定版图中待抓取引脚的对象,将其记为目标对象,获取目标对象的对象模板;对象模板包括匹配层和绕线层,匹配层是用于进行图形匹配的图层,绕线层是用于将对象的端子引出的连接线图层;基于目标对象的对象模板在版图中抓取目标对象的引脚,包括:利用对象模板的匹配层在版图中进行匹配查找,查找到与匹配层的图形相匹配的图形后,将对象模板的绕线层进行复制后添加至版图中的对应位置,用于将目标对象的端子引出,实现对目标对象引脚的抓取。在本实施例中,确定目标对象后,还获取目标对象在版图中的定位点,利用对象模板的匹配层在版图中进行匹配查找时,是在版图中以定位点为中心的预设匹配范围内进行匹配查找。获取目标对象在版图中的定位点的方法包括:预设用于匹配识别所述目标对象的图层记为标记层或图形记为特征图形;利用目标对象的标记层或者特征图形在版图中匹配识别目标对象,并获取目标对象的定位点坐标信息。其中,标记层是指:用于匹配识别目标对象的特征图层,或者收集有目标对象定位点坐标信息的标识层。

54.下面提供对象模板制作过程的一些可行的做法示例,以方便本领域的专业技术人员理解对象模板,但不以任何方式限制对象模板。在本实施例中,对象模板中还利用引脚标记层标记引脚的电极。示例的获取对象模板是通过下述方式制作对象模板得到:在版图中定位对象,并截取对象的版图作为模板的原型版图;对原型版图进行简化处理后制作得到对象模板。具体的示例过程包括:(ⅰ)在版图中定位对象,判断对象是否为版图中的图元:若是,则将图元的版图截取作为模板的原型版图;若不是,则将对象及其预设范围内的图形一起截取作为模板的原型版图。本实施例中截取如图2所示的原型版图。示例的做法中版图的图元是通过引用基本图元或特定图元的方式,以及阵列基本图元或特定图元的方式预先创建的。(ⅱ)对原型版图进行简化处理,包括:先删除原型版图中的后段绕线图层,得到如图3所示的版图。根据测试要求,添加若干连接线(尽量沿用原型版图中绕线)即获得若干新增绕线层,以将对象的端子引出作为引脚;利用引脚标记层标记引脚的电极:源极s,两个漏极d1、d2,以及两个栅极g1、g2,具体可参考图4。若干新增绕线层的具体数量可根据实际的版图设计情况相应设定,并不限制。确定若干图形特征有辨识度的图层作为匹配层,并删除所述匹配层中的不完整图形后,并删除所述对象模板中除匹配层、新增绕线层和引脚标记层外的其余图层,得到如图5所示简化后的最终版图,作为对象模板。示例的不完整图形是存在从版图中截取原型版图时被截断的基本图元。需要说明的是,本实施例中,获取对象模板可以通过上述过程进行制作获取,在实际应用中基于对象模板抓取对象引脚也可以调用已经制作好的对象模板重复使用,无须重新制作。在一些具体的实施例中,通过设置匹配参数中的模板地址(layout),来提供对象模板的存储地址。

55.实施例二使本领域的专业技术人员更全面地理解实施例一的基于模板抓取对象引脚的方

法,通过本实施例对实施例一中步骤三的一些具体做法进行展开示例,但不以任何方式限制本发明。

56.在本实施例中,利用对象模板的匹配层,在版图中以定位点为中心的匹配范围template match search range内进行图形匹配查找;具体步骤包括:步骤a):设置匹配参数:在对象模板的匹配层中设置匹配点的坐标(devicex,devicey),以及预设匹配范围template match search range和匹配坐标误差容许范围template match coordinate tolerance。步骤b):将匹配点对齐版图中的定位点,利用对象模板的匹配层进行图形匹配:若匹配成功,则完成匹配查找;若匹配失败,则继续后续步骤。步骤c):将匹配点在以所述定位点为中心的匹配坐标误差容许范围内移动,使所述匹配层在以定位点为中心的匹配范围内进行图形匹配:若匹配成功,则完成匹配查找;若匹配失败,则继续后续步骤。步骤d):判断是否调整匹配参数:若调整匹配参数(比如扩大匹配范围和匹配坐标误差容许范围),则至步骤b)继续执行;若不调整匹配参数,则结束本次匹配查找。

57.利用对象模板的匹配层,在版图中以定位点为中心的匹配范围内,无法查找到与匹配层的图形相匹配的图形时,则可以扩大匹配范围后再进行匹配查找。在具体的实施例中,可以在匹配开始时,通过设置匹配参数中的匹配点坐标(devicex,devicey)、匹配范围template match search range和匹配坐标误差容许范围template match coordinate tolerance来进行限定。其中的匹配点是在对象模板中选定的匹配起始点,用于在匹配开始时对齐版图的定位点。匹配范围作为起始的匹配范围。匹配点坐标是指:匹配点在对象模板中的坐标,示例的匹配点以坐标(devicex,devicey)表征。匹配坐标误差容许范围用于在匹配过程中保证匹配范围不扩大至超出预设的匹配坐标误差容许范围。

58.示例的与匹配层的图形相匹配的图形,是指与匹配层的图形完全一致的图形或者匹配层的图形在相互正交的两个方向中任一方向上镜像后的图形。为了便于理解相互正交的两个方向以直角坐标示例即x方向和y方向,与匹配层的图形相匹配的图形可以是匹配层的图形在x方向上镜像后的图形,或者所述匹配层的图形在y方向上镜像后的图形。在具体的做法中,可以在匹配开始时,通过设置匹配参数中的镜像信息(mirror-check)来进行选择,控制进行对象模板匹配时是否进行对象模板在x或y方向上的镜像。

59.需要说明的是本实施例的基于模板抓取对象引脚的方法中,还提供自动抓取对象的剩余引脚的选择。在具体的做法中,可以通过设置匹配参数中的自动连井(auto-welltie)来选择。比如晶体管只通过对象模板抓取源极、漏极和栅极引脚,通过设置该参数来选择是否同时抓取对应的体极(body)引脚。根据实际应用情况判断是否还有剩余引脚需要抓取并相应实施,如有则在基于对象模板抓取目标对象的引脚后,还自动抓取目标对象剩余的引脚,基于对象模板抓取与自动抓取的做法相结合抓取目标对象的全部引脚,在此并不限定。

60.实施例三本实施例提供一种测试芯片设计方法,如图6所示,具体包括下述步骤:步骤s1:输入产品芯片版图,基于图形化解读获取产品芯片版图中的对象及其对象信息;其中,产品芯片版图包括前段图层和后段图层;步骤s2:创建测试芯片的后段图层,包括:在产品芯片上排布若干焊盘;筛选出若干对象作为目标对象;抓取目标对象的引脚;为目标对象的引脚分配焊盘,并绕线实现目标对象的引脚到所分配焊盘的连接;其中,抓取目标对象的引脚,通

过上述实施例一、二所示例的基于模板抓取引脚的方法实现;步骤s3:将产品芯片的前段图层和步骤s2创建的测试芯片的后段图层进行合并连接,获得测试芯片的版图。

61.本实施例在步骤s1中,图形化解读包括:利用预设的特征图形,根据特征图形匹配识别对应的对象,并采用量化表征相应的对象信息;对象包括器件和热点图形。其中热点图形就是易产生工艺缺陷(比如光刻工艺缺陷)的结构图形,示例的情况中包括连接线结构、有源区(aa)、单扩散中断(sdb,single diffusion break)。示例的器件可以包括mosfet(金属氧化物半导体场效应晶体管)、二极管、bjt(双极结型晶体管)、电阻、电容、电感、sram(静态随机存取存储器)。在本实施例中,在原始产品芯片上排布焊盘后的情况如图7所示。

62.示例的步骤s1中,对象信息是指能影响对象性能的特征信息,包括对象特征图形的信息、对象特征图形与其周围图形之间的环境信息。环境信息例如相对距离信息等。在本实施例中,还建立有对象数据库,用于存储步骤s1中获取的对象及对象信息。如图8所示意的对象信息包括:对象的名称、位置坐标,以及各项量化表征的特征信息。

63.下面以mosfet为例,说明对象的识别及对象信息获取的具体做法。根据mosfet的类型,预设两种特征图形用于识别mosfet。分别为:n型mosfet:n型栅极(ngate)两边分别边缘接触n型源极和漏极(nsd),且在非nwell区域能有p型体极(ptap)。p型mosfet:p型栅极(pgate)两边分别边缘接触p型源极和漏极(psd),且在nwell区域能有n型体极(ntap)。其中,上述特征图形中涉及的mosfet器件相关图形定义示例如下。n型有源区:ndiff=((aa and nimp) not pimp) not nwell;p型有源区:pdiff=((aa and pimp) not nimp) and nwell;n型栅极:ngate=(poly not eg)and ndiff;p型栅极:pgate=(poly not eg) and pdiff;n型源、漏极:nsd=ndiff not poly;p型源、漏极:psd=pdiff not poly;n型体极:ntap=((aa and nimp) not pimp) and nwell;p型体极:ptap=((aa and pimp) not nimp) not nwell。上述特征图形中涉及的基本图形定义相应示例如下:poly—多晶硅层;polycut—多晶硅删除层;eg—边缘栅极标识层;aa—有源层;nimp—n型注入层;pimp—p型注入层;nwell—n阱层;psub—p衬底;iomk—thick device标识层。

64.在本实施例中,定义的mosfet的本身特征参数和周围环境参数可参考图9,示例包括l、w、dpl11、dpl12、sa、sb、peeu等,在这里并不限定具体情况。

65.实施例四通过本实施例对步骤s2中的一些具体的做法进行展开示例。本实施例中,在产品芯片上排布若干焊盘包括:在测试芯片上,以两个焊盘组在第一方向上间隔交错摆放焊盘的方式摆放多个焊盘组,形成若干个沿着第一方向的焊盘序列;在焊盘序列的两侧区域,分别确定焊盘序列中焊盘的可选区域,用于焊盘连接其可选区域内的测试对象引脚以形成测试通路。其中,焊盘组为焊盘阵列;第一方向是指焊盘组中焊盘阵列的行方向或列方向。将焊盘的设计尺寸在行方向、列方向上的预设值相应的分别记为sizex、sizey,相邻焊盘在行方向、列方向上预设的间隔值分别记为pitchx、pitchy。具体如图10所示,设置的焊盘组为焊盘数为48

×

2的焊盘阵列,每两个焊盘组的焊盘在y方向上进行间隔交错排布interleaved。该产品芯片的面积(约9mm

×

9mm)内可以摆放约232个焊盘组,焊盘排放的总数为22272个,在y方向上焊盘组的重复行数为四,在x方向上焊盘组的重复列数为五十八。行方向和列方向可以分别为x和y方向或者y和x方向,图10仅是示意,并不因此限定行与列的特定排布。

66.本实施例在步骤s2中,筛选出若干对象作为目标对象包括仅在可选区域内的对象中进行筛选。可选区域是相邻两个焊盘组的焊盘间隔交错的排布的焊盘序列两侧的区域,即示例的每列沿着y方向排布的焊盘序列两侧的区域,可选区域可参考图11中的device area,图11中pad group代表焊盘组。

67.示例的筛选具体利用预设的筛选规则来实现。筛选出若干对象作为目标对象,还包括为不同的对象选择适用的筛选规则进行筛选。根据不同的对象选择若干筛选规则进行筛选得到目标对象。示例的做法中根据测试芯片的实际应用需求设置选择的筛选规则的优先级顺序,进而按优先级顺序应用筛选规则以筛选出符合的若干对象作为目标对象。示例的预设有30多种不同的筛选规则,覆盖mosfet、bjt、diode、电阻、电容、sram、hotspot等。下面以mosfet的一项筛选规则来进行示例性说明:devicetype中各种不同类型的mosfet,按照基本参数w和l的最小值、最大值,分别选出满足要求的目标器件。示例的筛选规则中对这部分筛选出来的目标器件感兴趣,覆盖到产品芯片中各种mosfet的w、l范围两端的极限值,即最小值和最大值,用于监测工艺窗口(process window)。选中的目标器件参数可参考下表1。

68.表1.选中的目标器件参数表在本实施例的一般操作中,在满足筛选规则且数量足够的待选器件中,随机选取三个样本器件,若满足筛选规则的待选器件数量不足三个,则优先全部选取,该筛选规则一共选取了如图12所示的二十个目标器件。

69.在本实施例步骤s2中,目标对象的引脚包括:目标对象的端子、以及将端子引出的若干连接线。如图13所示,示例的做法中通过自动识别并且抓取mosfet的栅极、源极、漏极、体极四端子,并且创建四个端子的金属引线,做符合设计规则(design rule)的处理和引脚出线方向的优化设置,即让四个引脚尽量从四个不同方向出线,让后续步骤中的绕线更加便捷。因体极的实际位置较远,故在图13中仅示出栅极、源极、漏极的自动识别和抓取结果,仅保留后段图层。在也有的情况中,将端子引出的若干连接线包括与原始产品芯片版图中连接线相同路径的连接线和/或新创建的连接线,一般会尽量沿用与原始产品芯片版图中

连接线相同路径的连接线,在此并不限定。

70.在本实施例中为目标对象的引脚分配焊盘包括:将构成焊盘序列的间隔交错摆放的两个焊盘组分别记为第一焊盘组和第二焊盘组。将焊盘序列一侧的可选区域记为奇数区域,另一侧的可选区域记为偶数区域。奇数区域为第一焊盘组的可选区域,偶数区域为第二焊盘组的可选区域;将位于该焊盘序列的奇数区域中的目标对象的引脚分配给该焊盘序列中第一焊盘组的焊盘,将位于该焊盘序列的偶数区域中的目标对象的引脚分配给该焊盘序列中第二焊盘组的焊盘。对于可选区域可参考图10和图11,图10中设两个在y方向上间隔交错摆放的焊盘组分别为第一焊盘组pad groupⅰ和第二焊盘组pad groupⅱ,并将沿着y方向排布的焊盘序列左侧的可选区域设为左侧可选区域device area of pad groupⅰ,将沿着y方向排布的焊盘序列右侧的可选区域设为右侧可选区域device area of pad groupⅱ;分配焊盘时,将属于第一焊盘组pad groupⅰ中的焊盘与该焊盘所在焊盘序列的左侧可选区域device area of pad groupⅰ内的目标对象的引脚相配,将第二焊盘组pad groupⅱ中的焊盘与该焊盘所在焊盘序列的右侧可选区域device area of pad groupⅱ内的目标对象的引脚相配。

71.本实施例在步骤s2中,为引脚分配焊盘包括在符合可绕线性原则的若干焊盘中选择距离引脚最近的焊盘进行分配。即在为目标对象的引脚分配焊盘时,遵循:1)就近且可绕线性原则分配,这里的可绕线性原则包括焊盘对于该引脚可绕线,以及所有引脚的整体可绕线;2)只为焊盘分配其可选区域内的目标对象的引脚。

72.在本实施例中预设有若干绕线规则。步骤s2中,绕线是根据不同的引脚选择对应的绕线规则进行绕线。在对目标对象的引脚到所分配焊盘进行绕线时,自动根据不同的引脚(比如一般引脚、对电流引起压降敏感的引脚等),选择对应的绕线规则进行自动绕线。

73.本实施例中,对图13抓取的目标器件mosfet的四个引脚,即栅极、源极、漏极和体极进行自动绕线。其中体极将和其他同类型的器件共享最底部的焊盘,而其余三个引脚将会按照可绕性和就近原则分配焊盘。如图14所示的焊盘分配情况如下:栅极g配pad_92;漏极d配pad_94;源极s配pad_96;体极b配pad_2(底部共享焊盘);其中该mosfet在pad_92、pad_94、pad_96所属焊盘组对应的可选区域内。而在绕线时,栅极g和体极b采用single绕线,漏极d和源极s采用大面积mesh绕线用于降低ir drop(ir压降)。

74.在本实施例中,步骤s2中还包括:删除产品芯片的后段图层(导电互连层)。步骤s3之后还对测试芯片进行验证,示例的包括通过drc验证是否符合设计规则,通过lvs验证确保后段绕线的连接符合要求,验证合格则完成对该测试芯片的设计,得到用于监测产品芯片良率和性能的高定内置测试芯片。本实施例中提供的测试芯片,在本实施例的产品芯片面积下一共选出约6200个目标对象,并且将目标对象的测量引脚直接连接到临近的焊盘上,在提高面积利用率的同时,通过引脚直连焊盘,可以覆盖更多的测试项和测试条件。

75.在本实施例中还提供测试芯片设计系统,包括存储设备。该存储设备中存储有多条指令,指令适于由处理器加载并执行本实施例的测试芯片设计方法。

76.在本实施例中还提供了测试芯片,采用本实施例的测试芯片设计方法设计得到。

77.本发明为了便于叙述清楚而采用的一些常用的英文名词或字母只是用于示例性指代而非限定性解释或特定用法,不应以其可能的中文翻译或具体字母来限定本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1