一种半导体封装结构及其制备方法与流程

本公开涉及三维制程,尤其涉及一种半导体封装结构及其制备方法。

背景技术:

1、hbm存储器(high bandwidth memory)是一种基于3d堆栈工艺的高性能dram内存,与传统内存技术相比,hbm存储器具有更高带宽、更多i/o数量、更低功耗、更小尺寸,可应用于高性能计算、超级计算机、大型数据中心、人工智能/深度学习、云计算等领域。

2、hbm存储器技术主要是基于对处理器计算规模需求发展而来,在早期时候,人们对计算机数据处理要求不高,处理器架构模型层数较少,计算规模较小,算力也较低;后随着ai等技术的发展,对处理器要求越来越高,模型加深对算力需求相应增加,导致了带宽瓶颈,即i/o问题,此时通过增大片内缓存、优化调度模型来增加数据复用率等方式解决;但后期随着ai等技术普及,用户量增多,云端ai处理需求多用户、高吞吐、低延迟、高密度部署,计算单元剧增使i/o瓶颈愈加严重,此时,片上hbm存储器出现使ai/深度学习完全放到片上成为可能,集成度提升的同时,使带宽不再受制于芯片引脚的互联数量,从而在一定程度上解决了带宽和计算能力瓶颈。

3、但是随着hbm存储器的集成度要求增高,芯片堆叠层数越来越多,技术难点也越来越多。

技术实现思路

1、有鉴于此,本公开实施例提供一种半导体封装结构及其制备方法。

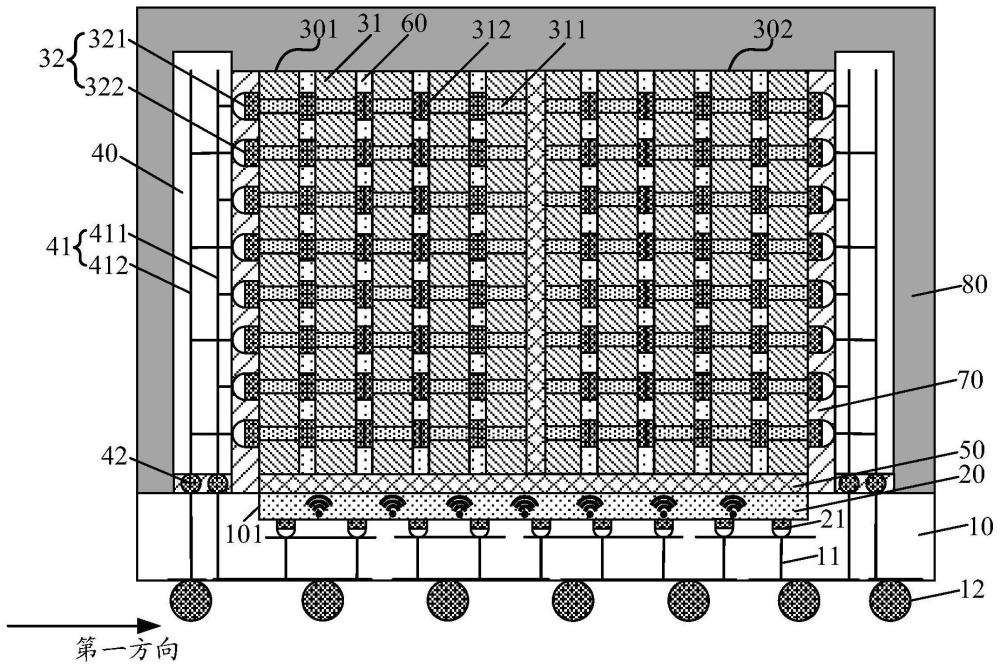

2、根据本公开实施例的第一方面,提供了一种半导体封装结构,包括:

3、第一基板;

4、第一半导体芯片,与所述第一基板连接;

5、第二半导体芯片堆叠结构,包括至少一个第一芯片堆叠结构和至少一个第二芯片堆叠结构,所述第一芯片堆叠结构和所述第二芯片堆叠结构沿第一方向并列排布于所述第一半导体芯片上;所述第一芯片堆叠结构和所述第二芯片堆叠结构包括多个沿第一方向依次堆叠的第二半导体芯片;所述第一芯片堆叠结构和所述第二芯片堆叠结构分别在沿第一方向远离对方的一侧形成有多个第二导电凸块;其中,所述第一方向为平行于所述第一基板的平面的方向;

6、多个第二基板,所述第二基板内的信号线与所述第二导电凸块连接;沿垂直于所述第一基板的平面的方向,所述第二基板与所述第一基板连接。

7、在一些实施例中,所述第一半导体芯片包括逻辑芯片,所述第二半导体芯片堆叠结构包括dram芯片。

8、在一些实施例中,还包括:

9、粘附膜,位于所述第一半导体芯片与所述第二半导体芯片堆叠结构之间,以及位于所述第一芯片堆叠结构和所述第二芯片堆叠结构之间。

10、在一些实施例中,所述粘附膜包括第一粘附膜和位于所述第一粘附膜上的第二粘附膜,所述第二粘附膜的弹性模量大于所述第一粘附膜的弹性模量。

11、在一些实施例中,所述第一半导体芯片与所述第二半导体芯片堆叠结构之间通过无线进行通讯。

12、在一些实施例中,所述第一基板内形成有凹槽,所述第一半导体芯片位于所述凹槽内,所述第一半导体芯片与所述第一基板通过第一导电凸块连接,所述第二基板与所述第一基板通过第三导电凸块连接。

13、在一些实施例中,所述第一半导体芯片位于所述第一基板上,,所述第一半导体芯片与所述第一基板通过第一导电凸块连接,所述第二基板与所述第一基板通过第三导电凸块连接。

14、在一些实施例中,还包括:

15、多个硅通孔,所述硅通孔沿第一方向贯穿所述第二半导体芯片;

16、多个第四导电凸块,位于相邻两个所述第二半导体芯片之间,且与所述硅通孔对应连接;

17、所述第二导电凸块与所述硅通孔以及所述第四导电凸块对应连接。

18、在一些实施例中,所述信号线包括接地线和电源线,所述第二导电凸块包括第一子导电凸块和第二子导电凸块;

19、所述接地线与所述第一子导电凸块电连接,所述电源线与所述第二子导电凸块电连接。

20、在一些实施例中,相邻两个第二子导电凸块之间至少间隔一个第一子导电凸块,所述第一子导电凸块包围所述第二子导电凸块。

21、在一些实施例中,还包括:

22、填充层,位于所述第二半导体芯片堆叠结构与所述第二基板之间,和/或,所述第一半导体芯片和所述第一基板之间。

23、在一些实施例中,还包括:

24、封装化合物结构,位于所述第一基板上;所述封装化合物结构至少包裹所述第二半导体芯片堆叠结构和所述第二基板;

25、所述填充层的杨氏模量大于所述封装化合物结构的杨氏模量。

26、根据本公开实施例的第二方面,提供了一种如上述实施例中任一项所述的半导体封装结构的制备方法,包括:

27、形成第二半导体芯片堆叠结构,第二半导体芯片堆叠结构包括至少一个第一芯片堆叠结构和至少一个第二芯片堆叠结构,所述第一芯片堆叠结构和所述第二芯片堆叠结构包括多个依次堆叠的第二半导体芯片;在所述第一芯片堆叠结构和所述第二芯片堆叠结构的沿堆叠方向的一侧形成多个第二导电凸块;

28、形成第一半导体芯片;

29、将所述第一芯片堆叠结构和所述第二芯片堆叠结构沿堆叠方向的远离所述第二导电凸块的表面相对设置,并将所述第一芯片堆叠结构和所述第二芯片堆叠结构的垂直于所述堆叠方向的表面与所述第一半导体芯片表面连接;

30、提供多个第二基板;所述第二基板沿堆叠方向位于所述第一芯片堆叠结构和所述第二芯片堆叠结构形成有第二导电凸块的一侧,所述第二基板内的信号线与所述第二导电凸块连接;

31、提供第一基板;将所述第一半导体芯片与所述第一基板连接,以及将所述第二基板与所述第一基板连接。

32、在一些实施例中,所述形成第二半导体芯片堆叠结构,包括:

33、沿堆叠方向,形成贯穿所述第二半导体芯片的硅通孔;

34、在相邻两个所述第二半导体芯片之间形成第四导电凸块,所述第四导电凸块与所述硅通孔对应连接;

35、将多个所述第二半导体芯片通过所述硅通孔和所述第四导电凸块进行混合键合连接,形成第二半导体芯片堆叠体;

36、将所述第二半导体芯片堆叠体形成为多个第二半导体芯片堆叠结构。

37、在一些实施例中,所述提供第二基板,包括:

38、对所述第二基板进行切割,在所述第二基板上形成第三导电凸块,使所述第二基板形成有第三导电凸块的表面与所述第二半导体芯片堆叠结构的靠近所述第一半导体芯片的表面齐平。

39、在一些实施例中,在所述第一基板内形成凹槽;

40、将所述第一半导体芯片放置于所述凹槽内。

41、在一些实施例中,还包括:

42、形成粘附膜,通过所述粘附膜将所述第二半导体芯片堆叠结构和所述第一半导体芯片进行连接,以及将所述第一芯片堆叠结构和所述第二芯片堆叠结构进行连接。

43、在一些实施例中,所述第一半导体芯片与所述第二半导体芯片堆叠结构之间通过无线进行通讯。

44、在一些实施例中,还包括:

45、形成填充层,所述填充层位于所述第二半导体芯片堆叠结构与所述第二基板之间,和/或,所述第一半导体芯片和所述第一基板之间。

46、本公开实施例中,第一芯片堆叠结构和第二芯片堆叠结构分别与一个第二基板连接,并通过第二基板与第一基板连接,如此,第一基板可以分别为第一芯片堆叠结构和第二芯片堆叠结构进行供电,通过两级基板的方式为第二半导体芯片堆叠结构供电,可有效减短供电链路,降低链路上的压降;同时第一基板可以通过有线的方式为第一半导体芯片进行供电,并和第一半导体芯片之间进行信号交换,具有高可靠性。

- 还没有人留言评论。精彩留言会获得点赞!