记忆体元件及其形成方法与流程

1.本揭露是关于一种记忆体元件及其形成方法。

背景技术:

2.集成电路包括一次性可编程(one-time-programmable;otp)记忆体元件,以提供非挥发性记忆体(non-volatile memory;nvm)元件使用,使得数据可在集成电路关闭后不会流失。非挥发性记忆体的一种形式为安装在集成电路内的反熔丝(anti-fuse)单元,其使用连接于其他电路元件的一层介电材料(例如,氧化物)。为编程反熔丝单元,跨越介电材料提供一编程电场,藉以实质上转换(例如,使崩溃)介电材料,使得介电材料的电阻降低。一般来说,为确认反熔丝单元的状态,跨越介电材料提供一读取电场并读取最终电流。

技术实现要素:

3.一种一次性编程记忆体元件,包含基板、第一晶体管、第二晶体管、第一字元线、第二字元线,和位元线。第一晶体管位于基板上,第一晶体管包含第一栅极结构,以及第一源/漏极区和第二源/漏极区,位于第一栅极结构的相对两侧。第二晶体管位于基板上,其中第二晶体管操作于反转模式,第二晶体管包含第二栅极结构,具有比第一栅极结构更多的功函数金属层,以及第三源/漏极区和第四源/漏极区,位于第二栅极结构的相对两侧。第一字元线位于第一晶体管的第一栅极结构上方并与其电性连接。第二字元线位于第二晶体管的第二栅极结构上方并与其电性连接。位元线位于第一晶体管的第一源/漏极区上方并与其电性连接。

4.一种一次性编程记忆体元件,包含基板、第一栅极结构、第二栅极结构、第三栅极结构、第一源/漏极区、第二源/漏极区、第三源/漏极区,及第四源/漏极区、第一字元线、第二字元线、第三字元线,以及位元线。第一栅极结构、第二栅极结构、第三栅极结构位于基板上方,其中第二栅极结构的功函数值不同于第一栅极结构的功函数值和第三栅极结构的功函数值,且第一栅极结构的功函数值实质上相同于第三栅极结构的功函数值。第一源/漏极区、第二源/漏极区、第三源/漏极区,及第四源/漏极区位于基板内,其中第一源/漏极区及第二源/漏极区位于第一栅极结构的相对两侧,第二源/漏极区及第三源/漏极区位于第二栅极结构的相对两侧,而第三源/漏极区及第四源/漏极区位于第三栅极结构的相对两侧。第一字元线位于第一栅极结构上方并与其电性连接。第二字元线位于第二栅极结构上方并与其电性连接。第三字元线位于第三栅极结构上方并与其电性连接。位元线位于第一源/漏极区和第四源/漏极区上方并与其电性连接。

5.一种形成一次性编程记忆体元件的方法,包含在一基板上形成第一虚设栅极结构和第二虚设栅极结构;在第一虚设栅极结构和第二虚设栅极结构的相对侧壁上形成多个栅极间隔物;移除第一虚设栅极结构和第二虚设栅极结构以形成第一栅极沟槽和第二栅极沟槽;在第一栅极沟槽内形成一第一金属栅极结构,在第二栅极结构内形成第二金属栅极结构,形成第一金属栅极结构和第二金属栅极结构包含:在第一栅极沟槽和第二栅极沟槽内

形成多个第一功函数金属层;蚀刻第一功函数金属层;在第一栅极沟槽和第二栅极沟槽内形成多个第二功函数金属层;蚀刻第二功函数金属层;以及在第二栅极沟槽内形成一第三功函数金属层,其中第三功函数金属层并不形成于第一栅极沟槽内;以及形成一第一字元线电性耦接至第一金属栅极结构和一第二字元线电性耦接至第二金属栅极结构。

附图说明

6.当通过附图阅读时,自以下详细描述,最佳地理解本揭露内容的态样。注意,根据该行业中的标准实务,各种特征未按比例绘制。事实上,为了论述的清晰起见,可任意地增大或减小各种特征的尺寸。

7.图1为本揭露的部分实施例的记忆体元件的示意图;

8.图2a为本揭露的部分实施例的对记忆体元件执行编程操作的示意图;

9.图2b为本揭露的部分实施例的对记忆体元件执行读取操作的示意图;

10.图3为本揭露的部分实施例的记忆体元件的示意图;

11.图4a为本揭露的部分实施例的对记忆体元件执行编程操作的示意图;

12.图4b为本揭露的部分实施例的对记忆体元件执行读取操作的示意图;

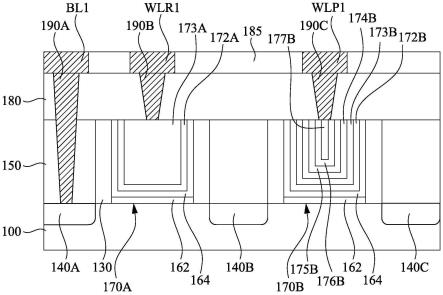

13.图5a及图5b为本揭露的部分实施例的记忆体元件的剖面图;

14.图6a及图6b为本揭露的部分实施例的记忆体元件的c-v图;

15.图6c为本揭露的部分实施例的记忆体元件的v

bd-v

th

图;

16.图7至图25为本揭露的部分实施例的制造记忆体元件的方法在不同阶段的示意图;

17.图26为本揭露的部分实施例的制造记忆体元件的方法;

18.图27至图39为本揭露的部分实施例的制造记忆体元件的方法在不同阶段的示意图;

19.图40a至图40e为本揭露的部分实施例的制造记忆体元件的栅极结构。

20.【符号说明】

21.100:基板

22.120a,120b,120c:虚设栅极

23.122:栅极介电层

24.124:虚设栅电极

25.130:栅极间隔物

26.140a,140b,140c,140d:源/漏极区

27.150:层间介电层(ild层)

28.162:界面层

29.164:栅极介电层

30.170a,170b,170c:栅极结构

31.172a,172b,172c,173a,173b,173c,174b,175b,176b,177b:功函数金属层

32.180:层间介电层(ild层)

33.185:层间介电层(ild层)

34.190a,190b,190c,190d,190e:导电柱

35.272a,272b,272c,273a,273b,273c,274b,275b,276b,277b:功函数金属层

36.370,470,570,670,770:栅极结构

37.372,472,473,573,573,672,673,773:功函数金属层

38.a,b:电阻节点

39.bl1,bl2,bl3:位元线

40.c1,c2,c3,c4,c5,c6:记忆体单元

41.md1,md2:记忆体元件

42.ma1,ma2,ma3,ma4,ma5:图案化遮罩

43.o1,o2,o3,o4,o5:开口

44.t1,t0,t1_a,t1_b:晶体管

45.tra,trb,trc:沟槽

46.wlp0,wlr0,wlr0_a,wlr0_b,wlp1,wlr1,wlr1_a,wlr1_b:字元线

47.w1,w2,w3,w4,w5:宽度

48.v1,v2,v3,v3’,v4,v5,v6:电压

[0049]vbl1

,v

bl2

,v

bl3

,v

wlr0

,v

wlp0

,v

wlr1

,v

wlp1

:通孔

[0050]

rf:电阻

[0051]

s101-s108:方块

具体实施方式

[0052]

以下揭露内容提供许多不同实施例或实例,用于实施提供的标的的不同特征。以下描述组件及配置的具体实例以简化本揭露内容。当然,这些仅为实例,且并不意欲为限制性。举例而言,在接下来的描述中,第一特征在第二特征上方或上的形成可包括第一与第二特征直接接触地形成的实施例,且亦可包括额外特征可形成于第一与第二特征之间使得第一与第二特征可不直接接触的实施例。此外,在各种实例中,本揭露内容可重复参考数字及/或字母。此重复是为了简单且清晰的目的,且自身并不规定论述的各种实施例及/或组态之间的关系。

[0053]

另外,为了易于描述,诸如“在

……

之下(beneath)”、“在

……

下方(below)”、“下部(lower)”、“在

……

上方(above)”及“上部(upper)”及类似者的空间相对术语可在本文中用以描述如在图中图示的一个元件或特征与另一元件或特征的关系。除了图中描绘的定向之外,该些空间相对术语意欲亦涵盖在使用或操作中的元件的不同定向。可将设备以其他方式定向(旋转90度或以其他定向),且同样地可将本文中使用的空间相对描述词相应地作出解释。

[0054]

本揭露的部分实施例包括一次性编程(one-time programmable;otp)记忆体单元。此处,一次性编程记忆体单元仅可通过数据电性化编程一次,且即便电源已不再提供,一次性编程记忆体单元内的编程数据仍然会保存。例如,例如,一次性编程记忆体单元提供了一种反熔丝元件(anti-fuse device),包括基板和形成在基板中的源极区和漏极区,源极区和漏极区横向隔开并在其间形成通道(channel)。反熔丝元件还包括形成在通道上的栅极氧化物和形成在栅极氧化物上的栅极。通过向栅极以及源极区和漏极区中的至少一个施加电源以击穿栅极氧化物来执行反熔丝的编程,用以最小化栅极与通道之间的电阻。

[0055]

图1为本揭露的部分实施例的记忆体元件的示意图。如图1所示,记忆体元件包括多个一次性编程记忆体单元c1、c2、c3、c4、c5、c6,多个字元线(word line)wlp0、wlr0、wlr1、wlp1,以及多个位元线(bit line)bl1、bl2、bl3。字元线wlp0、wlr0、wlr1、wlp1沿着x方向排列,而每一条字元线wlp0、wlr0、wlr1、wlp1则沿着y方向延伸。位元线bl1、bl2、bl3沿着y方向排列,而每一条位元线bl1、bl2、bl3则沿着x方向延伸。

[0056]

在部分实施例中,每一个一次性编程记忆体单元c1至c6包括第一晶体管t0和第二晶体管t1。请参看一次性编程记忆体单元c1,第一晶体管t0的栅极端电性连接至字元线wlp0,而第二晶体管t1的栅极端电性连接至字元线wlr0。第一晶体管t0的一个源/漏极端子为浮接(floated),而第一晶体管t0的另一个源/漏极端子电性连接至电阻节点a。此处,由于第一晶体管t0的一个源/漏极端子为对于储存或读取一次性编程记忆体单元c1内的数据并不造成影响,因此这个源/漏极端子为浮接。而第二晶体管t1的一个源/漏极端子也电性连接至电阻节点a,而第二晶体管t1的另一个源/漏极端子则耦接至位元线bl1。在部分实施例中,第一晶体管t0的源/漏极端子电性耦接至第二晶体管t1的源/漏极端子。

[0057]

请参看一次性编程记忆体单元c2,第一晶体管t0的栅极端电性连接至字元线wlp1,而第二晶体管t1的栅极端电性连接至字元线wlr1。第一晶体管t0的一个源/漏极端子为浮接,而第一晶体管t0的另一个源/漏极端子电性连接至电阻节点a。此处,由于第一晶体管t0的一个源/漏极端子为对于储存或读取一次性编程记忆体单元c1内的数据并不造成影响,因此这个源/漏极端子为浮接。而第二晶体管t1的一个源/漏极端子也电性连接至电阻节点a,而第二晶体管t1的另一个源/漏极端子则耦接至位元线bl1。在部分实施例中,第一晶体管t0的源/漏极端子电性耦接至第二晶体管t1的源/漏极端子。在部分实施例中,一次性编程记忆体单元c1和c2共用相同的一条位元线bl1。

[0058]

一次性编程记忆体单元c3至c6类似于上述讨论的一次性编程记忆体单元c1和c2,因此相关的细节将不再赘述。一般来说,晶体管的栅极是通过在绝缘层上方层层堆叠导电层。在编程操作中,第一晶体管t0的栅极的绝缘层可被破坏。而第二晶体管t1则作为开关元件以选择一次性编程记忆体单元。

[0059]

图2a为本揭露的部分实施例的对记忆体元件执行编程操作的示意图。图2b为本揭露的部分实施例的对记忆体元件执行读取操作的示意图。应了解,在图2a和图2b中,为了方便描述,仅绘制一次性编程记忆体单元c2。在编程操作中,第一晶体管t0和第二晶体管t1的基极(body)耦接至接地电压,其中第一晶体管t0和第二晶体管t1为金属氧化物半导体(metal-oxide-semiconductor)晶体管。

[0060]

参照图2a,其中图2a绘制了编程操作中的两种不同状况。在图2a的状况1中,对字元线wlp1供给一高电位电压v1,而对字元线wlr1提供具有比高电位电压v1还要低电位的一电压v2。位元线bl1耦接至接地电压v3。此处,电压v2具有足够高的电位以打开第二晶体管t1,而高电位电压v1则具有足够高的电位以破坏第一晶体管t0内的栅极结构(例如,图5a的栅极结构170b)内的绝缘层(例如,图5a的界面层162和栅极介电层164)。在部分实施例中,电压v2的范围约在1.8v至约2.4v,其足够大以打开第二晶体管t1,而高电位电压v1可为例如4.8v。在部分实施例中,接地电压v3可视为具有0v的电位。

[0061]

由于供给第二晶体管t1的栅极的电压v2足够高以打开第二晶体管t1,第二晶体管t1的栅极被打开,因此电阻节点a便电性耦接至接地电压v3。第一晶体管t0的栅极耦接至高

电位电压v1。提供至第一晶体管t0的栅极的电压(例如,电压v1)和提供至第一晶体管t0的源/漏极端的电压(例如,电压v3)之间的压差足以破坏(例如,使崩溃)第一晶体管t0内的绝缘层。当绝缘层被破坏,字元线wlp1和电阻节点a之间将形成电流路径。最终电路可以视为在电流路径中具有一电阻rf。因此,在状况1中,一次性编程记忆体单元c2在编程操作之后可被视为“已编程”,因为第一晶体管t0的栅极的绝缘层在电性上已被破坏。

[0062]

另一方面,在图2a的状况2中,对字元线wlp1供给一高电位电压v1,而对字元线wlr1提供具有比高电位电压v1还要低电位的一电压v2。位元线bl1耦接至电压v3’。此处,电压v3’具有比图2a的状况1的接地电压v3还要高的电位。例如,电压v3’可为约1.2v,其高于接地电压v3(例如,约0v)。在部分实施例中,电压v3’与电压v2实质上等值,使得第二晶体管t2的栅极端子和源极端子之间的电压差可约为0,因此第二晶体管t2为关闭,故第二晶体管t1连接至第一晶体管t0的源/漏极端子为浮接。即便高电位电压v1通过字元线wlp1施加至第一晶体管t0上,电场将不会施加至第二晶体管t2的绝缘层上,因为第一晶体管t0连接至第二晶体管t1的源/漏极端子为浮接。因此,在编程操作中,第二晶体管t1的绝缘层将不会崩溃,使得第二晶体管t1在编程操作之后仍然维持其原本的功能。因此,在状况2中,一次性编程记忆体单元c2在编程操作之后可被视为“未编程”,因为第一晶体管t0的栅极的绝缘层在电性上未被破坏。

[0063]

参照图2b,其中图2b绘制了编程操作中的两种不同状况。应了解图2b中的状况1为延续第图2a中的状况1,而图2b中的状况2为延续第图2a中的状况2。

[0064]

在读取操作中,对字元线wlp1施加一电源电压v4,而对字元线wlr1施加一电源电压v5。位元线bl1以接地电压v6进行预充电。电源电压v5足够高以打开第二晶体管。

[0065]

在图2b的状况1中,由于第一晶体管t0的栅极结构内的绝缘层被破坏,位元线bl1的电压会增高,因此第一晶体管t0的栅极和位元线bl1之间的电流亦会增加。另一方面,在状况2中,由于第一晶体管t0的栅极结构内的绝缘层未被破坏,位元线bl1的电位将不会提升,并维持着预充电的电压(例如,接地电压v6),因此在第一晶体管t0的栅极和位元线bl1之间将没有电流产生。可通过确认位元线bl1是否具有电流来读取数据。例如,在状况1中,若因为第一晶体管t0的绝缘层的崩溃而导致位元线bl1的电压或是电流增加,则可确认数据为“1”。另一方面,若位元线bl1的电压或是电流并未增加,则可确认数据为“0”。也就是说,若绝缘层崩溃,位元线bl1具有逻辑位准“1”,若绝缘层并未崩溃,位元线bl1具有逻辑位准“0”。

[0066]

图3为本揭露的部分实施例的记忆体元件md2的示意图。图3的记忆体元件md2的部分元件类似于图1的md1的部分元件,因此相关细节将不再赘述。图3的记忆体元件md2不同于图1的md1,其中记忆体元件md2的一次性编程记忆体单元c1-c6的每一者包括第一晶体管t0、第二晶体管t1_a以及第三晶体管t1_b。此外,记忆体元件md2包括多条字元线wlp0、wlr0_a、wlr0_b、wlp1、wlr1_a、wlr1_b。

[0067]

请参看一次性编程记忆体单元c1,第一晶体管t0的栅极端电性连接至字元线wlp0,第二晶体管t1_a的栅极端电性连接至字元线wlr0_a,第二晶体管t1_b的栅极端电性连接至字元线wlr0_b。第一晶体管t0的一个源/漏极端子连接至电阻节点a,而第一晶体管t0的另一个源/漏极端子电性连接至电阻节点b。而第二晶体管t1_a的一个源/漏极端子也电性连接至电阻节点a,而第二晶体管t1_a的另一个源/漏极端子则耦接至位元线bl1。类似

地,第三晶体管t1_b的一个源/漏极端子也电性连接至电阻节点b,而第三晶体管t1_b的另一个源/漏极端子则耦接至位元线bl1。在部分实施例中,第一晶体管t0的源/漏极端子电性耦接至第二晶体管t1_a的源/漏极端子,而第一晶体管t0的另一源/漏极端子电性耦接至第三晶体管t1_b的源/漏极端子。

[0068]

请参看一次性编程记忆体单元c2,第一晶体管t0的栅极端电性连接至字元线wlp1,第二晶体管t1_a的栅极端电性连接至字元线wlr1_a,第二晶体管t1_b的栅极端电性连接至字元线wlr1_b。第一晶体管t0的一个源/漏极端子连接至电阻节点a,而第一晶体管t0的另一个源/漏极端子电性连接至电阻节点b。而第二晶体管t1_a的一个源/漏极端子也电性连接至电阻节点a,而第二晶体管t1_a的另一个源/漏极端子则耦接至位元线bl1。类似地,第三晶体管t1_b的一个源/漏极端子也电性连接至电阻节点b,而第三晶体管t1_b的另一个源/漏极端子则耦接至位元线bl1。在部分实施例中,第一晶体管t0的源/漏极端子电性耦接至第二晶体管t1_a的源/漏极端子,而第一晶体管t0的另一源/漏极端子电性耦接至第三晶体管t1_b的源/漏极端子。在部分实施例中,一次性编程记忆体单元c1和c2共用相同的一条位元线bl1。

[0069]

一次性编程记忆体单元c3至c6类似于上述讨论的记忆体元件md2的一次性编程记忆体单元c1和c2,因此相关的细节将不再赘述。一般来说,晶体管的栅极是通过在绝缘层上方层层堆叠导电层。在编程操作中,第一晶体管t0的栅极的绝缘层可被破坏。而第二晶体管t1_a和第三晶体管t1_b则作为开关元件以选择一次性编程记忆体单元。

[0070]

图4a为本揭露的部分实施例的对图3的记忆体元件md2执行编程操作的示意图。图4b为本揭露的部分实施例的对图3的记忆体元件md2执行读取操作的示意图。图4a的编程操作和图4b的读取操作类似于图2a和图2b所讨论的内容,因此相关细节将不再赘述。

[0071]

参照图4a,其中图4a绘制了编程操作中的两种不同状况。在图4a的状况1中,对字元线wlp1供给一高电位电压v1,而对字元线wlr1_a和wlr1_b提供电压v2。也就是说,在编程操作其间,字元线wlr1_a和wlr1_b是耦接至相同电压位准。位元线bl1耦接至接地电压v3。此处,电压v2具有足够高的电位以打开第二晶体管t1_a和第三晶体管t1_b,而高电位电压v1则具有足够高的电位以破坏第一晶体管t0内的栅极结构(例如,图5a的栅极结构170b)内的绝缘层(例如,图5a的界面层162和栅极介电层164)。在部分实施例中,电压v2的范围约在1.8v至约2.4v,其足够大以打开第二晶体管t1,而高电位电压v1可为例如4.8v。在部分实施例中,接地电压v3可视为具有0v的电位。

[0072]

由于供给第二晶体管t1_a的栅极和第三晶体管t1_b的栅极的电压v2足够高以打开第二晶体管t1,第二晶体管t1的栅极和第三晶体管t1_b的栅极被打开,因此电阻节点a和b便电性耦接至接地电压v3。第一晶体管t0的栅极耦接至高电位电压v1。提供至第一晶体管t0的栅极的电压(例如,电压v1)和提供至第一晶体管t0的源/漏极端的电压(例如,电压v3)之间的压差足以破坏(例如,使崩溃)第一晶体管t0内的绝缘层。当绝缘层被破坏,字元线wlp1和电阻节点a、b之间将形成电流路径。最终电路可以视为在电流路径中具有一电阻rf。因此,在状况1中,一次性编程记忆体单元c2在编程操作之后可被视为“已编程”,因为第一晶体管t0的栅极的绝缘层在电性上已被破坏。

[0073]

另一方面,在图4a的状况2中,对字元线wlp1供给一高电位电压v1,而对字元线wlr1_a、wlr1_b提供电压v2。位元线bl1耦接至电压v3’。此处,电压v3’具有比图2a的状况1

的接地电压v3还要高的电位。例如,电压v3’可为约1.2v,其高于接地电压v3(例如,约0v)。在部分实施例中,电压v3’与电压v2实质上等值,使得第二晶体管t1_a的栅极端子和源极端子之间的电压差可约为0,且第三晶体管t1_b的栅极端子和源极端子之间的电压差可约为0,因此第二晶体管t1_a和第三晶体管t1_b为关闭,故第二晶体管t1_a和第三晶体管t1_b连接至第一晶体管t0的源/漏极端子为浮接。即便高电位电压v1通过字元线wlp1施加至第一晶体管t0上,电场将不会施加至第二晶体管t1_a和第三晶体管t1_b的绝缘层上,因为第一晶体管t0连接至第二晶体管t1_a和第三晶体管t1_b的源/漏极端子为浮接。因此,在编程操作中,第一晶体管t0的绝缘层将不会崩溃,使得第一晶体管t0在编程操作之后仍然维持其原本的功能。因此,在状况2中,一次性编程记忆体单元c2在编程操作之后可被视为“未编程”,因为第一晶体管t0的栅极的绝缘层在电性上未被破坏。

[0074]

参照图4b,其中图4b绘制了编程操作中的两种不同状况。应了解图4b中的状况1为延续第图4a中的状况1,而图4b中的状况2为延续第图4a中的状况2。

[0075]

在读取操作中,对字元线wlp1施加一电源电压v4,而对字元线wlr1_a和wlr1_b施加一电源电压v5。位元线bl1以接地电压v6进行预充电。电源电压v5足够高以打开第二晶体管t1_a和第三晶体管t1_b。

[0076]

在图4b的状况1中,由于第一晶体管t0的栅极结构内的绝缘层被破坏,位元线bl1的电压会增高,因此第一晶体管t0的栅极和位元线bl1之间的电流亦会增加。另一方面,在状况2中,由于第一晶体管t0的栅极结构内的绝缘层未被破坏,位元线bl1的电位将不会提升,并维持着预充电的电压(例如,接地电压v6),因此在第一晶体管t0的栅极和位元线bl1之间将没有电流产生。可通过确认位元线bl1是否具有电流来读取数据。例如,在状况1中,若因为第一晶体管t0的绝缘层的崩溃而导致位元线bl1的电压或是电流增加,则可确认数据为“1”。另一方面,若位元线bl1的电压或是电流并未增加,则可确认数据为“0”。也就是说,若绝缘层崩溃,位元线bl1具有逻辑位准“1”,若绝缘层并未崩溃,位元线bl1具有逻辑位准“0”。

[0077]

图5a及图5b为本揭露的部分实施例的记忆体元件的剖面图。在部分实施例中,图5a的的剖面图对应至图1至图2b所讨论的记忆体元件md1的一次性编程记忆体单元c2,而图5b的的剖面图对应至图3至图4b所讨论的记忆体元件md2的一次性编程记忆体单元c2。

[0078]

参照图5a。图示一基板100。在一些实施例中,基板100可以包括半导体材料且可包括例如渐变层或掩埋氧化物等已知结构。在一些实施例中,基板100包括可以未掺杂或经掺杂(例如,p型、n型或其组合)的块体硅。可以使用适合形成半导体元件的其他材料,例如锗、石英、蓝宝石和玻璃,皆可以替代地用于基板100。或者,硅基板100可以是绝缘体上半导体(soi)基板的主动层或多层结构例如在块体硅层上形成的硅锗层。

[0079]

金属栅极结构170a和金属栅极结构170b设置在基板100上方。在一些实施例中,金属栅极结构170a包括界面层162、栅极介电层164、第一功函数金属层172a、以及第二功函数金属层173a。金属栅极结构170b包括界面层162、栅极介电层164、第一功函数金属层172b、第二功函数金属层173b、第三功函数金属层174b、第四功函数金属层175b、第五功函数金属层176b和第六功函数金属层177b。在一些实施例中,金属栅极结构170b具有比金属栅极结构170a更多的功函数金属层。

[0080]

在一些实施例中,界面层162可以由氧化物制成,例如sio2。在一些实施例中,栅极

介电层164可以由高k介电材料制成,例如金属氧化物、过渡金属氧化物等。高k介电材料的实例包括但不限于氧化铪(hfo2)、氧化铪硅(hfsio)、氧化铪钽(hftao)、氧化铪钛(hftio)、氧化铪锆(hfzro)、氧化锆、氧化钛、氧化铝、二氧化铪-氧化铝(hfo

2-al2o3)合金或其他适用的介电材料。

[0081]

在一些实施例中,功函数金属层172a至173a和172b至177b可以是n型或p型功函数层。示例性p型功函数金属包括tin、tan、ru、mo、al、wn、zrsi2、mosi2、tasi2、nisi2、wn、其他合适的p型功函数材料,或它们的组合。示例性的n型功函数金属包括ti、ag、taal、taalc、tialn、tac、tacn、tasin、mn、zr、其他合适的n型功函数材料或它们的组合。栅极间隔物130分别设置在金属栅极结构170a和170b的相对侧壁上。在一些实施例中,栅极间隔物130可由sio2、si3n4、sio

x

ny、sic、sicn、sioc、siocn膜和/或它们的组合制成。

[0082]

举例来说,功函数金属层172a和173a可以分别是taal和taal。另一方面,功函数金属层172b、173b、174b、175b、176b和177b可以分别是taal、tialn、tialn、taal、taal和taal。

[0083]

源/漏极区140a、140b和140c设置在基板100中。在一些实施例中,源/漏极区140a和140b设置在金属栅极结构170a的相对侧,源/漏极区140b和140c设置在金属栅极结构170b的相对侧。源/漏极区140b设置在金属栅极结构170a和170b之间。也就是说,金属栅极结构170a和170b共用相同的源/漏极区140b。

[0084]

在一些实施例中,金属栅极结构170a、源/漏极区140a和140b以及在金属栅极结构170a下方的基板100的部分形成如图1至图2b中讨论的一次性编程记忆体单元c2的晶体管tl。类似地,金属栅极结构170b、源/漏极区140b和140c以及金属栅极结构170b下方的基板100的部分形成如如图1至图2b中讨论的一次性编程记忆体单元c2的晶体管t0。

[0085]

在一些实施例中,源/漏极区140a、140b和140c包括用于形成p型fet的p型掺杂剂,诸如硼。在其他实施例中,源/漏极区140a、140b和140c包括用于形成n型fet的n型掺杂剂,诸如磷。在一些实施例中,源/漏极区140a、140b和140c可以是磊晶成长区。因此,源/漏极区140a、140b和140c也可称为磊晶源/漏极结构。在一些实施例中,如果源/漏极区140a、140b和140c是磊晶生长的,则源/漏极区140a、140b和140c可以包括ge、si、gaas、algaas、sige、gaasp、sip或其他合适的材料。

[0086]

层间电介(ild)层150设置在源/漏极区140a、140b和140c上方,并且横向围绕金属栅极结构170a和170b。在一些实施例中,ild层150可以包括氧化硅、氮化硅、氮氧化硅、四乙氧基硅烷(teos)、磷硅玻璃(psg)、硼磷硅玻璃(bpsg)、低k介电材料和/或其他合适的介电材料。低k介电材料的示例包括但不限于氟化石英玻璃(fsg)、碳掺杂氧化硅、无定形氟化碳、聚对二甲苯、双苯并环丁烯(bcb)或聚酰亚胺。在一些实施例中,可以在ild层150与源/漏极磊晶结构140a、140b和140c之间选择性地形成接触蚀刻停止层(未图示)。接触蚀刻停止层可以包括与ild层150不同的材料,使接触蚀刻停止层和ild层150之间的蚀刻选择性不同。在一些实施例中,接触蚀刻停止层包括氮化硅、氮氧化硅或其他合适的材料。

[0087]

层间介电(ild)层180设置在ild层150上方并且覆盖金属栅极结构170a和170b。在一些实施例中,ild层180的材料可以类似于ild层150。

[0088]

导电柱190a、190b和190c设置在ild层150和180中。更详细地,导电柱190a延伸穿过ild层150和180并与源/漏极140a接触、导电柱190b延伸穿过ild层180并与金属栅极结构170a接触,而导电柱190c延伸穿过ild层180并与金属栅极结构170b接触。在一些实施例中,

region),以及反转区(inversion region)。

[0097]

参照图6a,其中图6a为图1、图2a、图2b、图5a所讨论的晶体管t1和图3、图4a、图4b、图5b所讨论的晶体管t1_a、t1_b的c-v图。此处,晶体管t1、t1_a、t1_b为n型元件,例如nmos元件。下方将以晶体管t1作为范例讨论,应了解晶体管t1_a、t1_b亦具有类似于晶体管t1的特性。

[0098]

当v

gs

为负值时,空穴被吸引到硅的表面(例如,基板100),形成积累层,这种状况可以被称为“累积模式(accumulation mode)”。

[0099]

随着v

gs

增加至超过晶体管t1的平能带电压(flat-band voltage)v

fb_1

,在半导体-氧化物的交界面(例如:基板100和界面层162/栅极介电层164的交界面)的主要载子会被替换。在这个状态的半导体称为空乏,因为半导体的表面将不具有主要在载子,这种状况可以被称为“空乏模式(depletion mode)”。半导体的这个区域作为介电质,因为其不包含可传导的载子。等效来说,其可做为半绝缘体。

[0100]

随着v

gs

增加至超过晶体管t1的阈值电压(threshold voltage)v

th_1

,动态载子的产生以及再结合,使得净载子产生。正的栅极电压产生电子-空穴对并吸引电子至栅极端子。再一次,由于栅极介电质为绝缘体,这些少数载子累积在基板至氧化物的交界面。累积的少数载子层可称为反转层,由于载子的极性反转,这种状况可以被称为“反转模式(inversion mode)”。在一定程度的正栅极电压后,大部分可用的少数载子位于反转层内,而更多的栅极电压已不会进一步的空乏半导体。也就是说,空乏区已达到其最大深度。一但空乏区达到最大深度,其电容可透过高频率电容仪量测,此电容为氧化物电容与最大空乏电容的串联。此电容亦可称为最小电容。c-v取线的斜率也几乎平缓。

[0101]

在图6a的部分实施例中,当正栅极电压v

gs

施加时,晶体管(例如:晶体管t1、t1_a、t1_b)操作为“累积模式”。因此,晶体管t1(或晶体管t1_a、t1_b)可称为“累积模式晶体管”或是“累积操作模式晶体管”。

[0102]

参照图6b,其中图6b为图5a和图5b所讨论的晶体管t0的c-v图。此处,晶体管t0为n型晶体管,例如nmos元件。

[0103]

图6b的晶体管t0和图6a所讨论的晶体管t1实质上具有相同的c-v特性,因此相关细节将不再赘述。图6b不同于图6a之处在于,晶体管t0的平能带电压v

fb_0

和阈值电压v

th_0

分别低于晶体管t1(或晶体管t1_a、t1_b)的平能带电压v

fb_1

和阈值电压v

th_1

。

[0104]

在部分实施例中,晶体管t0的平能带电压v

fb_0

低于0(例如:负值)。在部分实施例中,晶体管t0的阈值电压v

th_0

实质上等于0。例如,晶体管t0的阈值电压v

th_0

的范围约在0v至约0.4v。在部分实施例中,晶体管t0的阈值电压v

th_0

小于0(例如:负值)。例如,晶体管t0的阈值电压v

th_0

的范围约在-0.4v至约0v。

[0105]

在部分实施例中,若晶体管t0的阈值电压v

th_0

小于0,当正栅极电压v

gs

施加时,晶体管t0操作在“反转模式”。因此,晶体管t0亦可称为“反转模式晶体管”或“反转操作模式晶体管”。

[0106]

在部分实施例中,若晶体管t0的阈值电压v

th_0

略大于0,当正栅极电压v

gs

施加时,晶体管t0操作为“空乏模式”。因此,晶体管t0亦可称为“空乏模式晶体管”或“空乏操作模式晶体管”。然而,随着正栅极电压v

gs

变大晶体管t0会快速地转换为“反转模式”,因为晶体管t0的阈值电压v

th_0

略大于0。

[0107]

如图1至图4b所讨论,晶体管t0作为反熔丝单元,而非开关。因此,在本揭露的部分实施例中,当正栅极电压v

gs

施加时,若晶体管t0操作为“反转模式”,则正栅极电压v

gs

可以快速地到达晶体管t0的崩溃电压(breakdown voltage)v

bd

,而不会经过“累积模式”和“空乏模式”。因此,当正栅极电压v

gs

施加时,若晶体管t0操作为“累积模式”,则需要更多的电压让晶体管t0自“累积模式”转换为“反转模式”。因此,根据此配置,记忆体的功率可被降低。此外,晶体管可以通过低电压进行编程,亦可以提升记忆体元件的稳定性。

[0108]

图6c为本揭露的部分实施例的记忆体元件的v

bd-v

th

图。晶体管t0的阈值电压v

th_0

低于晶体管t1(或晶体管t1_a、t1_b)的阈值电压v

th_1

。此外,晶体管t0的崩溃电压v

bd_0

低于晶体管t1(或晶体管t1_a、t1_b)的崩溃电压v

bd_1

。

[0109]

在部分实施例中,晶体管t0的阈值电压v

th_0

的范围约0v至约0.4v,而晶体管t1(或晶体管t1_a、t1_b)的阈值电压v

th_1

的范围约0.3v至约0.8v。在部分实施例中,晶体管t0的崩溃电压v

th_0

的范围约2v至约4v,而晶体管t1(或晶体管t1_a、t1_b)的崩溃电压v

th_1

的范围约3.6v至约5.5v。

[0110]

应注意,因为晶体管tl和晶体管tl(或晶体管tl_a和tl_b)具有不同的阈值电压。晶体管t1的栅极结构和晶体管t1(或晶体管t1_a和t1_b)的栅极结构可以包括不同的功函数值。例如,在一些实施例中,图5a的栅极结构170a和图5a的栅极结构170b可以包括不同的功函数值。在一些实施例中,图5a的栅极结构170a可以包括比图5a的栅极结构170b更高的功函数值。类似地,图5b的栅极结构170a和170c以及图5b的栅极结构170b可以包括不同的功函数值。在一些实施例中,图5b的栅极结构170a和170c可以包括比图5b的栅极结构170b更高的功函数值。在一些实施例中,图5b的栅极结构170a和170c可具有基本相同的功函数值。

[0111]

图7至图25为制造图5b的结构的方法在不同阶段的示意图。应了解,图5a所讨论的结构可以通过省略形成图5b的栅极结构170c和字元线wlr_b达成。

[0112]

参考图7,在基板100上方形成多个虚设栅极结构120a、120b和120c。虚设栅极结构120a、120b和120c中的每一者包括栅极介电层122和虚设栅电极124。在一些实施例中,虚设栅极结构120a、120b和120c可以通过例如在基板100上方沉积栅极介电质材料和虚设栅电极材料,然后对栅极介电材料和虚设栅电极材料进行图案化工艺形成以形成虚设栅极结构120a、120b和120c。

[0113]

栅极介电层122可以是例如氧化硅、氮化硅、它们的组合等,并且可以通过适合的的技术沉积或热生长。栅极介电层122可以通过合适的工艺形成,例如化学气相沉积(cvd)、物理气相沉积(pvd)、原子层沉积(ald)或任何合适的工艺。虚设栅电极124可以包括多晶硅(poly-si)或多晶硅锗(poly-sige)。此外,虚设栅电极124可以是具有均匀或非均匀掺杂的掺杂多晶硅。虚设栅电极124可以通过合适的工艺形成,例如化学气相沉积(cvd)、物理气相沉积(pvd)、原子层沉积(ald)或任何合适的工艺。

[0114]

参考图8,在虚设栅极结构120a、120b和120c的相对侧壁上形成多个栅极间隔物130。栅极间隔物130可以据由例如在虚设栅极结构120a、120b和120c之上毯覆地沉积间隔层来形成,并执行蚀刻工艺以去除间隔层的水平部分,使得间隔层的垂直部分遗留在虚设栅极结构120a、120b和120c的侧壁上,其中间隔层的剩余垂直部分称为栅极间隔物130。

[0115]

参考图9,源/漏极区140a、140b、140c和140d形成在基板100的被虚设栅极结构

120a、120b、120c和栅极间隔物130暴露的部分中。在源/漏极区140a至140d是基板100中的掺杂半导体区的实施例中,源/漏极区140a至140d可以通过植入工艺以将n型掺杂剂(例如,磷)或p型掺杂剂(例如,硼)植入至基板100的暴露部分中。在源/漏极区140a到140d是磊晶结构的一些实施例中,源/漏极区140a到140d可以通过如蚀刻形成基板100的暴露部分以形成凹槽,然后通过选择性磊晶生长(seg)工艺在凹槽中沉积晶体半导体材料,其可以填充基板100中的凹槽并且可以进一步延伸超出基板100的原始表面以形成凸起的源/漏极磊晶结构。晶体半导体材料可以是元素的(例如si或ge等)或合金(例如si

1-xcx

或si

1-x

ge

x

等)。seg工艺可以使用任何合适的外延生长方法,例如气相/固相/液相外延(vpe、spe、lpe)或金属有机cvd(mocvd)或分子束外延(mbe)等。

[0116]

在形成源/漏极区140a、140b、140c和140d之后,在源/漏极区140a至140d上方形成层间介电(ild)层150。在一些实施例中,ild层150可以通过例如在基板100上方沉积介电材料毯,然后执行cmp工艺以去除多余的介电材料直到虚设栅极结构120a、120b和120c的顶面暴露。

[0117]

参考图10,移除虚设栅极结构120a、120b和120c以分别形成栅极沟槽tra、trb和trc。在一些实施例中,虚设栅极结构120a、120b和120c可以通过合适的蚀刻工艺去除,例如湿蚀刻、干蚀刻或其组合。

[0118]

参考图11。界面层162形成在被栅极沟槽tra、trb和trc暴露的基板100的表面之上,而栅极介电层164分别形成在界面层162之上。根据一些实施例,界面层162可以由氧化硅或氮氧化硅制成,并且可以通过热处理或通过化学氧化物形成来形成。栅极介电层164可以通过原子层沉积(ald)、化学气相沉积(cvd)、物理气相沉积(pvd)、电镀和/或其他合适的方法形成。

[0119]

参考图12,第一功函数金属层172a、172b和172c分别形成在栅极沟槽tra、trb和trc中。在一些实施例中,第一功函数金属层172a、172b和172c可以通过例如在基板100上方沉积功函数金属材料并填充栅极沟槽tra、trb和trc,然后执行cmp工艺移除多余的功函数金属材料,直到暴露出ild层150的顶面。栅极沟槽tra、trb和trc中功函数金属材料的剩余部分分别称为第一功函数金属层172a、172b和172c。

[0120]

参考图13,在基板100上方形成图案化遮罩ma1。在一些实施例中,图案化遮罩ma1具有多个开口o1,其中开口o1分别暴露部分第一功函数金属层172a、172b和172c。接着,蚀刻第一功函数金属层172a、172b和172c的暴露部分。在一些实施例中,开口o1具有宽度w1,其中宽度w1小于每一第一功函数金属层172a、172b与172c的最大宽度,使得开口o1暴露每一第一功函数金属层的中间部分。第一功函数金属层172a、172b和172c的开口o1暴露第一功函数金属层172a、172b和172c中的每一个的中间部分,但覆盖第一功函数金属层172a、172b和172c中每一者的中间部分的相对两侧的边缘部分。在一些实施例中,蚀刻工艺经控制,使得蚀刻工艺通过开口o1移除第一功函数金属层172a、172b和172c的中间部分,但不蚀刻穿过第一功函数金属层172a、172b和172c。使得第一功函数金属层172a、172b和172c的剩余部分仍然覆盖栅极介电层164。在一些实施例中,蚀刻工艺实质上将第一功函数金属层172a、172b和172c中的每一者的截面从矩形改变为u形截面。在一些实施例中,图案化遮罩ma1可以是硬遮罩,或者可以是光阻层。

[0121]

参考图14。移除图案化遮罩ma1。接着,分别在栅极沟槽tra、trb和trc中形成第二

功函数金属层173a、173b和173c。在一些实施例中,第二功函数金属层173a、173b和173c可以通过例如在基板100上方沉积功函数金属材料并填充栅极沟槽tra、trb和trc,然后执行cmp工艺以移除多余的功函数金属材料,直到暴露出ild层150的顶面。栅极沟槽tra、trb和trc中功函数金属材料的剩余部分分别称为第二功函数金属层173a、173b和173c。

[0122]

参考图15,在基板100上方形成图案化遮罩ma2。在一些实施例中,图案化遮罩ma2具有开口o2,其中开口o2暴露部分第二功函数金属层173b.在一些实施例中,图案化遮罩ma2完全覆盖栅极沟槽tra中的功函数金属层172a和173a,并且完全覆盖栅极沟槽trc中的功函数金属层172c和173c。即,栅极沟槽tra中的功函数金属层172a和173a以及栅极沟槽trc中的功函数金属层172c和173c没有被图案化遮罩ma2暴露。接着,蚀刻第二功函数金属层173b的暴露部分。在一些实施例中,开口o2具有宽度w2,其中宽度w2小于第二功函数金属层173b的最大宽度,使得开口o2暴露第二功函数金属层173b的中间部分,而图案化遮罩ma2覆盖在第二功函数金属层173b的中间部分的相对两侧的外围部分。在一些实施例中,蚀刻工艺经控制使得蚀刻工艺通过开口o2去除第二功函数金属层173b的中间部分,但不蚀刻穿过第二功函数金属层173b,使得剩余部分的第二功函数金属层172b仍然覆盖第一功函数金属层172b。在一些实施例中,蚀刻工艺实质上将第二功函数金属层172b从矩形截面改变为u形截面。在一些实施例中,图案化遮罩ma2的开口o2的宽度w2小于图13中讨论的图案化遮罩ma1的开口o1的宽度w1。在一些实施例中,图案化遮罩ma2可以是硬遮罩,或者可以是光阻层。

[0123]

参考图16。去除图案化遮罩ma2。接着,在栅极沟槽trb中形成第三功函数金属层174b并覆盖第二功函数金属层173b。在一些实施例中,第三功函数金属层174b可以通过例如在基板100上方沉积功函数金属材料并填充栅极沟槽trb,然后执行cmp工艺以去除多余的功函数金属材料直到暴露出ild层150的顶面而形成。栅极沟槽trb中功函数金属材料的剩余部分被称为第三功函数金属层174b。值得注意的是,因为栅极沟槽tra和trc分别被功函数金属层172a/173a和172c/173c完全填充,所以在栅极沟槽tra和trc中没有形成第三功函数金属层174b。

[0124]

参考图17,在基板100上方形成图案化遮罩ma3。在一些实施例中,图案化遮罩ma3具有开口o3,其中开口o3暴露部分第三功函数金属层174b.在一些实施例中,图案化遮罩ma3完全覆盖栅极沟槽tra中的功函数金属层172a和173a,并且完全覆盖栅极沟槽trc中的功函数金属层172c和173c。即,栅极沟槽tra中的功函数金属层172a和173a以及栅极沟槽trc中的功函数金属层172c和173c没有被图案化遮罩ma3暴露。接着,蚀刻第三功函数金属层174b的暴露部分。在一些实施例中,开口o4具有宽度w4,其中宽度w4小于第三功函数金属层174b的最大宽度,使得开口o3暴露第三功函数金属层174b的中间部分,而图案化遮罩ma3覆盖第三功函数金属层174b的中间部分的相对两侧的外围部分。在一些实施例中,蚀刻工艺经控制为使得蚀刻工艺经由开口o3移除第三功函数金属层174b的中间部分,但不蚀刻穿过第三功函数金属层174b,使得剩余部分的第三功函数金属层174b仍覆盖第二功函数金属层173b。在一些实施例中,蚀刻工艺实质上将第三功函数金属层174b从矩形截面改变为u形截面。在一些实施例中,图案化遮罩ma3的开口o3的宽度w3小于图15中讨论的图案化遮罩ma2的开口o2的宽度w2。在一些实施例中,图案化遮罩ma3可以是硬遮罩,或者可以是光阻层。

[0125]

参考图18。移除图案化遮罩ma3。接着,在栅极沟槽trb中形成第四功函数金属层175b并覆盖第三功函数金属层174b。在一些实施例中,第四功函数金属层175b可以通过例如在基板100上方沉积功函数金属材料毯并填充栅极沟槽trb,然后执行cmp工艺以移除多余的功函数金属材料直到暴露出ild层150的顶面而形成。栅极沟槽trb中功函数金属材料的剩余部分被称为第四功函数金属层175b。值得注意的是,因为栅极沟槽tra和trc分别被功函数金属层172a/173a和172c/173c完全填充,所以第四功函数金属层175b没有形成在栅极沟槽tra和trc中。

[0126]

参考图19,在基板100上方形成图案化遮罩ma4。在一些实施例中,图案化遮罩ma4具有开口o4,其中开口o4暴露部分第四功函数金属层175b。在一些实施例中,图案化遮罩ma4完全覆盖栅极沟槽tra中的功函数金属层172a和173a,并且完全覆盖栅极沟槽trc中的功函数金属层172c和173c。即,栅极沟槽tra中的功函数金属层172a和173a以及栅极沟槽trc中的功函数金属层172c和173c没有被图案化遮罩ma4暴露。接着,蚀刻第四功函数金属层174b的暴露部分。在一些实施例中,开口o4具有宽度w4,其中宽度w4小于第四功函数金属层175b的最大宽度,使得开口o4暴露第四功函数金属层175b的中间部分,而图案化遮罩ma4覆盖第四功函数金属层175b的中间部分的相对两的外围部分。在一些实施例中,蚀刻工艺经控制使得蚀刻工艺通过开口o4移除第四功函数金属层175b的中间部分,但不蚀刻穿过第四功函数金属层175b,使得剩余部分的第四功函数金属层175b仍然覆盖第三功函数金属层174b。在一些实施例中,蚀刻工艺实质上将第四功函数金属层175b从矩形截面改变为u形截面。在一些实施例中,图案化遮罩ma4的开口o4的宽度w4小于图17中讨论的图案化遮罩ma3的开口o3的宽度w3。在一些实施例中,图案化遮罩ma4可以是硬遮罩,或者可以是光阻层。

[0127]

参考图20。移除图案化遮罩ma4。接着,在栅极沟槽trb中形成第五功函数金属层176b并覆盖第四功函数金属层175b。在一些实施例中,第五功函数金属层176b可以通过例如在基板100上方沉积功函数金属材料毯并填充栅极沟槽trb,然后执行cmp工艺以移除多余的功函数金属材料直到暴露出ild层150的顶面而形成。栅极沟槽trb中功函数金属材料的剩余部分被称为第五功函数金属层176b。值得注意的是,因为栅极沟槽tra和trc分别被功函数金属层172a/173a和172c/173c完全填充,所以第五功函数金属层176b没有形成在栅极沟槽tra和trc中。

[0128]

参考图21,在基板100上方形成图案化遮罩ma5。在一些实施例中,图案化遮罩ma5具有开口o5,其中开口o5暴露部分第五功函数金属层176b.在一些实施例中,图案化遮罩ma4完全覆盖栅极沟槽tra中的功函数金属层172a和173a,并且完全覆盖栅极沟槽trc中的功函数金属层172c和173c。即,栅极沟槽tra中的功函数金属层172a和173a以及栅极沟槽trc中的功函数金属层172c和173c没有被图案化遮罩ma5暴露。接着,蚀刻第五功函数金属层176b的暴露部分。在一些实施例中,开口o5具有宽度w5,其中宽度w5小于第五功函数金属层176b的最宽宽度,使得开口o5暴露第五功函数金属层176b的中间部分,而图案化遮罩ma4覆盖第五功函数金属层176b的中间部分的相对两侧的外围部分。在一些实施例中,蚀刻工艺经控制使得蚀刻工艺经由开口o5移除第五功函数金属层176b的中间部分,但不蚀刻穿过第五功函数金属层176b,使得剩余部分第五功函数金属层176b仍然覆盖第四功函数金属层175b。在一些实施例中,蚀刻工艺实质上将第五功函数金属层176b从矩形截面改变为u形截面。在一些实施例中,图案化遮罩ma5的开口o5的宽度w5比图19中讨论的图案化遮罩ma4的

开口o4的宽度w4窄。在一些实施例中,图案化遮罩ma5可以是硬遮罩,或者可以是光阻层。

[0129]

参考图22。移除图案化遮罩ma5。接着,在栅极沟槽trb中形成第六功函数金属层177b并覆盖第六功函数金属层177b。在一些实施例中,第六功函数金属层177b可以通过例如在基板100上方沉积功函数金属材料并填充栅极沟槽trb,然后执行cmp工艺以移除多余的功函数金属材料直到暴露出ild层150的顶面而形成。栅极沟槽trb中功函数金属材料的剩余部分被称为第六功函数金属层177b。值得注意的是,因为栅极沟槽tra和trc分别被功函数金属层172a/173a和172c/173c完全填充,所以第六功函数金属层177b没有形成在栅极沟槽tra和trc中。

[0130]

参考图23。层间介电(ild)层180形成在ild层150上方并覆盖栅极结构170a、170b和170c。在一些实施例中,ild层180可以通过例如在基板100上方沉积介电材料,并且可选择性地执行cmp工艺平坦化ild层180的顶面来形成。

[0131]

参考图24。形成导电柱190a、190b、190c、190d和190e。在一些实施例中,导电柱190a和190e形成为延伸穿过ild层150和180并且分别接触源/漏极区140a和140d。另一方面,导电柱190b、190c和190d形成为延伸穿过ild层180并分别接触金属栅极结构170a、170b和170c。在一些实施例中,导电柱190a、190b、190c、190d和190e可以通过下述方法形成,例如,图案化ild层150和180以形成暴露源/汲区140a、140d和金属栅极结构170a、170b、170的开口,在开口中填充导电材料,然后进行cmp工艺以去除多余的导电材料直到暴露出ild层180的顶面。

[0132]

参考图25,在ild层180上方形成层间介电(ild)层185,并且在ild层185中形成字元线wlrl_a、wlpl、wlrl_b和位元线bll。在一些实施例中,字元线wlr1_a、wlp1、wlr1_b分别与导电柱190b、190c和190d接触。位元线与导电柱190a和190e接触。在一些实施例中,ild层185可以通过例如在基板100上方沉积介电材料,并且可选择性地执行cmp工艺以平坦化ild层185的顶面来形成。在一些实施例中,字元线wlr1_a、wlp1、wlr1_b和位元线bl1可以通过下述方法形成,例如,图案化ild层185以形成暴露导电柱190a、190b、190c、190d和190e的开口,在开口中填充导电材料,以及然后进行cmp工艺以去除多余的导电材料直到暴露出ild层185的顶面。

[0133]

图26为本揭露的部分实施例的制造记忆体元件的方法1000。虽然方法1000是由一系列操作或步骤来描述,然应了解此方法并没有限制操作或其顺序。因此,在部分实施例中,这些操作或步骤可以不同的顺序被执行,及/或同时地执行。此外,在部分实施例中,描述的操作或步骤可被切割为多个操作或步骤,其可在不同时间点或是相同时间点与其他操作或是子操作一起进行。在部分实施例中,描述的操作或步骤可被省略,或包括其他没有被描述的操作或步骤。

[0134]

在方块s101中,在基板上形成第一、第二、第三虚设栅极。图7为对应至方块s101的部分实施例的剖面图。

[0135]

在方块s102中,在第一、第二、第三虚设栅极的相对侧壁上形成栅极间隔物。图8为对应至方块s102的部分实施例的剖面图。

[0136]

在方块s103中,在基板经由第一、第二、第三虚设栅极和栅极间隔物所暴露的部分中形成源/漏极区,且在源/漏极区上方形成第一ild层。图9为对应至方块s103的部分实施例的剖面图。

[0137]

在方块s104中,移除第一、第二、第三虚设栅极以形成第一、第二、第三栅极沟槽。图10为对应至方块s104的部分实施例的剖面图。

[0138]

在方块s105中,在基板经由第一、第二、第三栅极沟槽所暴露的表面上形成界面层,并在界面层上方形成栅极介电层。图11为对应至方块s105的部分实施例的剖面图。

[0139]

在方块s106中,在第一、第二、第三栅极沟槽中形成第一功函数金属层。图12为对应至方块s106的部分实施例的剖面图。

[0140]

在方块s107中,在基板上方形成第一图案化遮罩,且蚀刻经由第一图案化遮罩所暴露的第一功函数金属层。图13为对应至方块s107的部分实施例的剖面图。

[0141]

在方块s108中,在第一、第二、第三栅极沟槽中形成第二功函数金属层。图14为对应至方块s108的部分实施例的剖面图。

[0142]

在方块s109中,在基板上方形成第二图案化遮罩,且蚀刻经由第二图案化遮罩所暴露的第二栅极沟槽内的第二功函数金属层。图15为对应至方块s109的部分实施例的剖面图。

[0143]

在方块s110中,在第二栅极沟槽中形成第三功函数金属层。图16为对应至方块s110的部分实施例的剖面图。

[0144]

在方块s111中,在基板上方形成第三图案化遮罩,且蚀刻经由第三图案化遮罩所暴露的第二栅极沟槽内的第三功函数金属层。图17为对应至方块s111的部分实施例的剖面图。

[0145]

在方块s112中,在第二栅极沟槽中形成第四功函数金属层。图18为对应至方块s112的部分实施例的剖面图。

[0146]

在方块s113中,在基板上方形成第四图案化遮罩,且蚀刻经由第四图案化遮罩所暴露的第二栅极沟槽内的第四功函数金属层。图19为对应至方块s113的部分实施例的剖面图。

[0147]

在方块s114中,在第二栅极沟槽中形成第五功函数金属层。图20为对应至方块s114的部分实施例的剖面图。

[0148]

在方块s115中,在基板上方形成第五图案化遮罩,且蚀刻经由第五图案化遮罩所暴露的第二栅极沟槽内的第五功函数金属层。图21为对应至方块s115的部分实施例的剖面图。

[0149]

在方块s116中,在第二栅极沟槽中形成第六功函数金属层。图22为对应至方块s116的部分实施例的剖面图。

[0150]

在方块s117中,在第一ild层上方形成第二ild层。图23为对应至方块s117的部分实施例的剖面图。

[0151]

在方块s118中,在第一ild层和第二ild层中形成导电柱。图24为对应至方块s118的部分实施例的剖面图。

[0152]

在方块s119中,在第二ild层上方形成第三ild层,并在第三ild层中形成字元线和位元线。图25为对应至方块s119的部分实施例的剖面图。

[0153]

图27至图39为本揭露的部分实施例的制造记忆体元件的方法在不同阶段的示意图。应注意图27至图39的部分元件和图7至图25所讨论的类似,因此相关细节将不再赘述。图27和图28分别类似于图11和图12。

[0154]

参照图29。在基板100上方形成图案化遮罩ma1。在一些实施例中,图案化遮罩ma1具有多个开口o1,其中开口o1分别暴露部分第一功函数金属层272a、272b和272c。接下来,通过使用以比蚀刻其他材料更快的蚀刻速率蚀刻第一功函数金属的蚀刻剂,选择性地回蚀刻第一功函数金属层272a、272b和272c的暴露部分。在一些实施例中,开口o1比第一功函数金属层272a、272b和272c中的每一个的最宽宽度宽,使得第一功函数金属层272a、272b和272c的最上表面降低至低于栅极介电层164的最顶端(或栅极侧墙130的顶面)的水平。在一些实施例中,蚀刻的第一功函数金属层272a、272b和272c具有基本相同的厚度。在一些实施例中,在回蚀第一功函数金属层272a、272b和272c之后,暴露栅极介电层164的侧壁。在一些实施例中,图案化遮罩ma1可以覆盖ild层150和栅极侧墙130,同时暴露整个栅极沟槽tra、trb和trc。在其他一些实施例中,可以省略图案化遮罩ma1,并且可以使用ild层150和栅极侧墙130作为蚀刻遮罩回蚀刻第一功函数金属层272a、272b和272c。

[0155]

参考图30。去除图案化遮罩ma1。接着,分别在栅极沟槽tra、trb和trc中形成第二功函数金属层273a、273b和273c。在一些实施例中,第二功函数金属层273a、273b和273c分别与栅极介电层164接触。

[0156]

参考图31,在基板100上方形成图案化遮罩ma2。在一些实施例中,图案化遮罩ma2具有开口o2,其中开口o2暴露第二功函数金属层273b。接下来,通过使用以比蚀刻其他材料更快的蚀刻速率蚀刻第二功函数金属的蚀刻剂选择性地回蚀刻第二功函数金属层273b。在一些实施例中,开口o2比第二功函数金属层273b的最宽宽度宽,使得第二功函数金属层273b的最上表面降低到低于栅极介电层164(或栅极间隔物130的顶面)。因此,栅极沟槽trb中的第二功函数金属层273b比栅极沟槽tra和trc中的第二功函数金属层273a和273c薄。在一些实施例中,在回蚀第二功函数金属层273b之后,暴露栅极介电层164的侧壁。在一些实施例中,图案化遮罩ma2可以覆盖ild层150和栅极间隔物130,同时暴露整个栅极沟槽trb。

[0157]

参考图32,移除图案化遮罩ma2。接着,在栅极沟槽trb中形成第三功函数金属层274b。在一些实施例中,第三功函数金属层274b与栅极介电层164接触。

[0158]

参考图33,在基板100上方形成图案化遮罩ma3。在一些实施例中,图案化遮罩ma3具有开口o3,其中开口o3暴露第三功函数金属层274b。接下来,通过使用以比蚀刻其他材料更快的蚀刻速率蚀刻第三功函数金属的蚀刻剂选择性地回蚀刻第三功函数金属层274b。在一些实施例中,图33的流程与图31的流程类似,为简化起见,不再赘述。

[0159]

参考图34。移除图案化遮罩ma3。接着,在栅极沟槽trb中形成第四功函数金属层275b。在一些实施例中,第四功函数金属层275b与栅极介电层164接触。

[0160]

参考图35,在基板100上方形成图案化遮罩ma4。在一些实施例中,图案化遮罩ma4具有开口o4,其中开口o4暴露第四功函数金属层275b。接下来,通过使用以比蚀刻其他材料更快的蚀刻速率蚀刻第四功函数金属的蚀刻剂选择性地回蚀刻第四功函数金属层275b。在一些实施例中,图35的流程与图31的流程类似,为简化起见,不再赘述。

[0161]

参考图36。移除图案化遮罩ma4。接着,在栅极沟槽trb中形成第五功函数金属层276b。在一些实施例中,第五功函数金属层276b与栅极介电层164接触。

[0162]

参考图37,在基板100上方形成图案化遮罩ma5。在一些实施例中,图案化遮罩ma4具有开口o5,其中开口o5暴露第五功函数金属层276b。接下来,通过使用以比蚀刻其他材料更快的蚀刻速率蚀刻第五功函数金属的蚀刻剂选择性地回蚀刻第五功函数金属层276b。在

一些实施例中,图37的流程与图31的流程类似,为简单起见,不再赘述。

[0163]

参考图38。移除图案化遮罩ma5。接着,在栅极沟槽trb中形成第六功函数金属层277b。在一些实施例中,第六功函数金属层277b与栅极介电层164接触。

[0164]

参考图39。注意,图39中形成的元件与图23至图25中讨论的相似,这些元件具有相同标记且为简化起见将不再重复细节。图39与图25的不同之处在于,图39的栅极结构270a、270b和270c的功函数金属层与栅极结构170a、170b和170c的功函数金属层具有不同的形状例如,栅极结构270b的功函数金属层272b至277b中的每一个具有矩形形状,且与栅极介电层164接触。栅极结构270a的功函数金属层272a和273a以及栅极结构270c的功函数金属层272c和273c具有与栅极结构270b的功函数金属层272b至277b相似的特性。

[0165]

图40a至图40e为本揭露的部分实施例的制造记忆体元件的栅极结构。应了解图40a至图40e的部分结构已于上述讨论,因此相关细节将不再赘述。

[0166]

金属栅极结构370、470、570、670和770分别示于图40a、图40b、图40c、图40d、图40e。在一些实施例中,金属栅极结构370、470、570、670、770中的每一个包括界面层162和栅极介电层164。金属栅极结构370包括功函数金属层372。金属栅极结构470包括功函数金属层472和功函数金属层472上方的功函数金属层473。金属栅极结构570包括功函数金属层572和功函数金属层572上方的功函数金属层573。金属栅极结构670包括功函数金属层672和功函数金属层672上方的功函数金属层673。金属栅极结构770包括功函数金属层773。在一些实施例中,金属栅极结构370、470、570、670和770彼此具有不同的功函数值。

[0167]

在一些实施例中,功函数金属层372、472、572和672由相同的材料制成。类似地,功函数金属层473、573、673和773由相同的材料制成。另一方面,功函数金属层372、472、572和672由与功函数金属层473、573、673和773不同的材料制成。

[0168]

在一些实施例中,功函数金属层372比功函数金属层472厚,功函数金属层472比功函数金属层572厚,并且功函数金属层572比功函数金属层672厚。类似的,功函数金属层773比功函数金属层673厚,功函数金属层673比功函数金属层573厚,功函数金属层573比功函数金属层473厚。

[0169]

在一些实施例中,如果若图1至图2b中讨论的记忆体元件mdl的晶体管tl包含栅极结构370,则图1至图2b中讨论的记忆体元件md1的晶体管t0可以包括栅极结构470、570、670和770其中一者,反之亦然。如果晶体管t1包括栅极结构470,则晶体管t0可以包括栅极结构370、570、670和770其中一者,反之亦然。如果晶体管t1包括栅极结构570,则晶体管t0可以包括栅极结构370、470、670和770其中一者,反之亦然。如果晶体管t1包括栅极结构670,则晶体管t0可以包括栅极结构370、470、570和770其中一者,反之亦然。如果晶体管t1包括栅极结构770,则晶体管t0可以包括栅极结构370、470、570和670其中一者,反之亦然。

[0170]

另一方面,如果图3至图4b中讨论的记忆体元件md2的晶体管t1_a和t1_b包括栅极结构370,则图3至图4b中讨论的记忆体元件md2的晶体管t0可以包括栅极结构470、570、670和770其中一者,反之亦然。如果晶体管t1_a和t1_b包括栅极结构470,则晶体管t0可以包括栅极结构370、570、670和770其中一者,反之亦然。如果晶体管t1_a和t1_b包括栅极结构570,则晶体管t0可以包括栅极结构370、470、670和770其中一者,反之亦然。如果晶体管t1_a和t1_b包括栅极结构670,则晶体管t0可以包括栅极结构370、470、570和770其中一者,反之亦然。如果晶体管t1_a和t1_b包括栅极结构770,则晶体管t0可以包括栅极结构370、470、

570和670其中一者,反之亦然。

[0171]

基于以上讨论,可以看出本揭露提供了优点。然而,应当理解,其他实施例可以提供额外的优点,并且并非所有优点都必须在本文中揭露,并且所有实施例都不需要特别的优点。一个优点是,当施加正栅极电压v

gs

时,otp存储器件的反熔丝晶体管可操作于“反转模式”,栅栅极电压v

gs

可以轻松达到反熔丝晶体管的崩溃电压v

bd

,而无需通过“积累模式”和“空乏模式”。因此,透过这种配置,可以降低记忆体元件的功率。此外,记忆体元件可以用较低的电压“编程”,这也将提高记忆体元件的可靠性。

[0172]

根据本揭露的部分实施例,一种一次性编程记忆体元件,包含基板、第一晶体管、第二晶体管、第一字元线、第二字元线,和位元线。第一晶体管位于基板上,第一晶体管包含第一栅极结构,以及第一源/漏极区和第二源/漏极区,位于第一栅极结构的相对两侧。第二晶体管位于基板上,其中第二晶体管操作于反转模式,第二晶体管包含第二栅极结构,具有比第一栅极结构更多的功函数金属层,以及第三源/漏极区和第四源/漏极区,位于第二栅极结构的相对两侧。第一字元线位于第一晶体管的第一栅极结构上方并与其电性连接。第二字元线位于第二晶体管的第二栅极结构上方并与其电性连接。位元线位于第一晶体管的第一源/漏极区上方并与其电性连接。

[0173]

在部分实施例中,其中第一晶体管操作于一累积模式。

[0174]

在部分实施例中,其中第一晶体管的第一栅极结构的一第一功函数值小于第二晶体管的第二栅极结构的一第二功函数值。

[0175]

在部分实施例中,其中第二晶体管的一崩溃电压小于第一晶体管的一崩溃电压。

[0176]

在部分实施例中,其中第二栅极结构内的功函数金属层的一数量是第一栅极结构内的功函数金属层的一数量的至少三倍。

[0177]

在部分实施例中,其中第二晶体管的一阈值电压小于0,而第一晶体管的一阈值电压大于0。

[0178]

在部分实施例中,其中第二晶体管的第二栅极结构包含接触第二栅极结构的功函数金属层的一第二栅极介电层。

[0179]

在部分实施例中,其中第一晶体管的第一栅极结构包含接触第一栅极结构的些功函数金属层的一第一栅极介电层。

[0180]

根据本揭露的部分实施例,一种一次性编程记忆体元件,包含基板、第一、第二、第三栅极结构、第一、第二、第三,及第四源/漏极区、第一字元线、第二字元线、第三字元线,以及位元线。第一、第二、第三栅极结构位于基板上方,其中第二栅极结构的功函数值不同于第一栅极结构的功函数值和第三栅极结构的功函数值,且第一栅极结构的功函数值实质上相同于第三栅极结构的功函数值。第一、第二、第三,及第四源/漏极区位于基板内,其中第一及第二源/漏极区位于第一栅极结构的相对两侧,第二及第三源/漏极区位于第二栅极结构的相对两侧,而第三及第四源/漏极区位于第三栅极结构的相对两侧。第一字元线位于第一栅极结构上方并与其电性连接。第二字元线位于第二栅极结构上方并与其电性连接。第三字元线位于第三栅极结构上方并与其电性连接。位元线位于第一和第四源/漏极区上方并与其电性连接。

[0181]

在部分实施例中,其中第二栅极结构的功函数值低于第一栅极结构的功函数和第三栅极结构的功函数值。

[0182]

在部分实施例中,其中第一和第三栅极结构具有比第二栅极结构更少的功函数金属层。

[0183]

在部分实施例中,其中第一和第三栅极结构具有相同数目的功函数金属层。

[0184]

在部分实施例中,其中第一栅极结构具有一第一栅极介电层和位于第一栅极介电层上方的一第一功函数金属层,第二栅极结构具有一第二栅极介电层和位于第二栅极介电层上方的一第二功函数金属层,其中第一第一功函数金属层和第二功函数金属层具有不同厚度。

[0185]

在部分实施例中,其中第一栅极结构和第一及第二源/漏极区形成一第一晶体管,其中第二栅极结构和第二及第三源/漏极区形成一第二晶体管,且第三栅极结构和第三及第四源/漏极区形成一第三晶体管,且其中第二晶体管的一阈值电压小于第一及第三晶体管的阈值电压。

[0186]

在部分实施例中,其中第一及第三晶体管的阈值电压实质上相等。

[0187]

在部分实施例中,一次性编程记忆体元件,还包含一层间介电层,位于基板上方并围绕第一、第二,及第三栅极结构,其中第二及第三源/漏极区的上表面完全被层间介电层覆盖。

[0188]

根据本揭露的部分实施例,一种形成一次性编程记忆体元件的方法,包含在一基板上形成第一和第二虚设栅极结构;在第一和第二虚设栅极结构的相对侧壁上形成多个栅极间隔物;移除第一和第二虚设栅极结构以形成第一和第二栅极沟槽;在第一栅极沟槽内形成一第一金属栅极结构,在第二栅极结构内形成第二金属栅极结构,形成第一和第二金属栅极结构包含:在第一和第二栅极沟槽内形成多个第一功函数金属层;蚀刻第一功函数金属层;在第一和第二栅极沟槽内形成多个第二功函数金属层;蚀刻第二功函数金属层;以及在第二栅极沟槽内形成一第三功函数金属层,其中第三功函数金属层并不形成于第一栅极沟槽内;以及形成一第一字元线电性耦接至第一金属栅极结构和一第二字元线电性耦接至第二金属栅极结构。

[0189]

在部分实施例中,其中在第一和第二栅极沟槽内形成第一功函数金属层使得第一功函数金属层完全填补第一和第二栅极沟槽。

[0190]

在部分实施例中,其中蚀刻第一功函数金属层使得第一功函数金属从矩形截面变为u型截面。

[0191]

在部分实施例中,方法,还包含在蚀刻第一功函数金属层之前在第一功函数金属层上方形成具有多个第一开口的一第一图案化遮罩;以及在蚀刻第二功函数金属层之前在第二功函数金属层上方形成具有多个第二开口的一第二图案化遮罩,其中第二开口窄于第一开口。

[0192]

前文概括了若干实施例的特征,使得熟悉此项技术者可更好地理解本揭露内容的态样。熟悉此项技术者应了解,其可易于将本揭露内容用作用于设计或修改其他处理程序及结构以用于实行相同目的及/或达成本文中介绍的实施例的相同优势的基础。熟悉此项技术者亦应认识到,这些等效构造不脱离本揭露内容的精神及范畴,且在不脱离本揭露内容的精神及范畴的情况下,其可进行各种改变、取代及更改。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1