寄生电容的测试结构及测试方法与流程

本申请涉及半导体测试领域,尤其涉及一种寄生电容的测试结构及测试方法。

背景技术:

1、随着器件的尺寸越来越小,当器件的尺寸缩小至90nm节点以下时,器件中的寄生电容效应不容忽视,特别是栅极结构和接触孔间的寄生电容(cgt-ct),栅极结构和有源区衬底间的寄生电容(cgt-aa)以及栅极结构和源漏结构间的寄生电容(cgt-sd)会影响器件的性能。

2、传统的测试结构和测试方法可以测试出上述三种寄生电容的总和,但是无法测试单个寄生电容,进而无法分析单个寄生电容对器件性能的影响,因此需要设计新的测试结构和测试方法以获得单个寄生电容。

技术实现思路

1、本申请要解决的技术问题是提供一种寄生电容的测试结构和测试方法,能够测试出单个寄生电容。

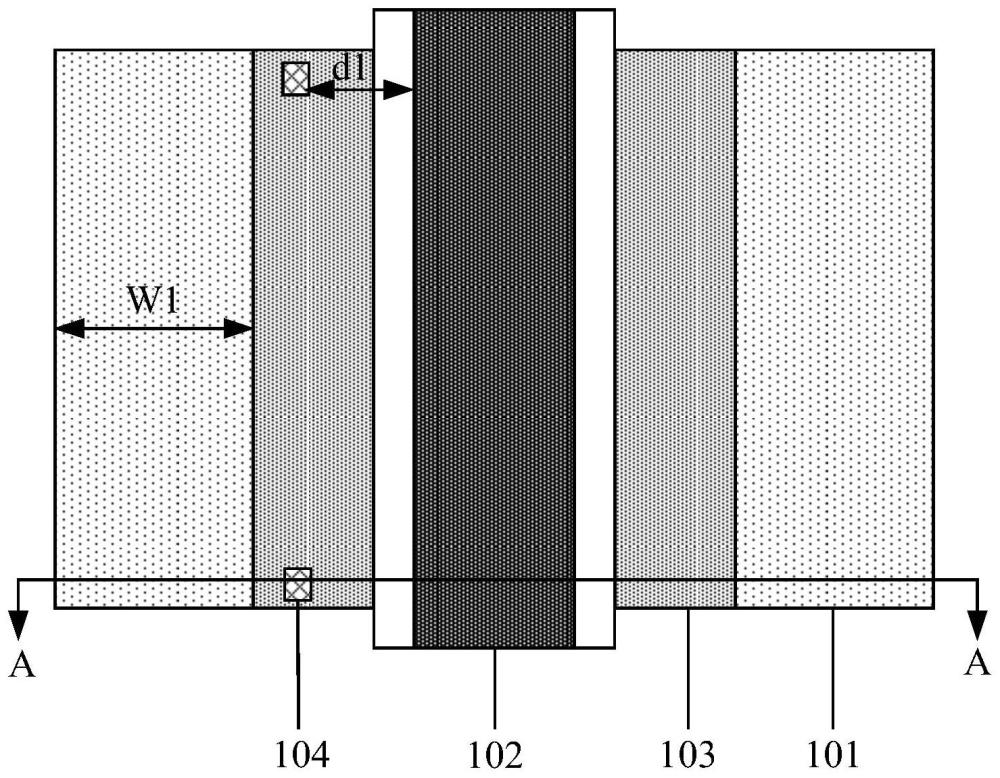

2、为解决上述技术问题,本申请提供了一种寄生电容的测试结构,包括第一测试结构、第二测试结构及第三测试结构;所述第一测试结构、第二测试结构及第三测试结构均包括位于衬底上的栅极结构、位于所述衬底中的源漏结构以及接触孔结构,其中所述栅极结构电连接至第一测试衬垫,并与所述衬底间形成第一寄生电容,所述源漏结构与所述栅极结构间形成第二寄生电容,所述接触孔结构电连接至第二测试衬垫,并与所述栅极结构间形成第三寄生电容;所述第一测试结构用于测试所述第一寄生电容和所述第二寄生电容之和,在所述第一测试结构中,所述接触孔结构位于部分所述源漏结构上且数量不超过两个,所述接触孔结构与所述栅极结构间具有第一水平间距,且所述接触孔结构远离所述栅极结构一侧的衬底具有第一宽度;所述第二测试结构用于测试所述第二寄生电容,在所述第二测试结构中,所述接触孔结构位于部分所述源漏结构上且数量不超过两个,所述接触孔结构与所述栅极结构间具有第一水平间距,所述接触孔结构远离所述栅极结构一侧的衬底具有第二宽度,且所述第二宽度小于所述第一宽度;所述第三测试结构用于测试所述第二寄生电容,在所述第三测试结构中,所述接触孔结构位于部分所述衬底上且数量超过两个,所述接触孔结构与所述栅极结构间具有第二水平间距,且所述第二水平间距大于所述第一水平间距,所述接触孔结构远离所述栅极结构一侧的衬底具有所述第二宽度。

3、在本申请的一些实施例中,所述第一水平间距为28nm~0.5μm。

4、在本申请的一些实施例中,所述第一宽度为0.01μm~5μm。

5、在本申请的一些实施例中,所述第二宽度为0.01μm~0.05μm。

6、在本申请的一些实施例中,所述第二水平间距不小于5μm。

7、在本申请的一些实施例中,所述测试结构还包括第四测试结构,用于测试所述第一寄生电容、所述第二寄生电容和所述第三寄生电容之和,其中所述第四测试结构与所述第一测试结构间仅所述接触孔结构的数量不同,且所述第四测试结构和所述第三测试结构的接触孔结构数量相同。

8、本申请还提供一种寄生电容的测试方法,对前述任一项所述的测试结构进行测试,所述测试方法包括:对所述第一测试结构进行测试,获得所述第一寄生电容和所述第二寄生电容之和,对所述第二测试结构进行测试,获得所述第二寄生电容,进而获得所述第一寄生电容;对所述第三测试结构进行测试,获得所述第二寄生电容;获得所述第一寄生电容、第二寄生电容和第三寄生电容之和;结合所述第一寄生电容、第二寄生电容和第三寄生电容之和以及所述第一寄生电容、所述第二寄生电容,获得所述第三寄生电容。

9、在本申请的一些实施例中,进行电容测试时,使所述第一测试衬垫接地,并在所述第二测试衬垫上施加偏置电压。

10、在本申请的一些实施例中,所述偏置电压为被测结构的工作电压。

11、在本申请的一些实施例中,对第四测试结构进行测试,获得所述第一寄生电容、第二寄生电容和第三寄生电容之和,且所述第四测试结构与所述第一测试结构间仅所述接触孔结构的数量不同,所述第四测试结构和所述第三测试结构的接触孔结构数量相同。

12、与现有技术相比,本申请技术方案的寄生电容的测试结构及测试方法具有如下有益效果:

13、所述寄生电容的测试结构包括第一测试结构和第二测试结构,其中第一测试结构用于测试所述第一寄生电容和所述第二寄生电容之和,第二测试结构用于测试第二寄生电容,因此结合第一测试结构和第二测试结构的测试结果可以获得第一寄生电容。

14、所述寄生电容的测试结构包括第三测试结构,可以测试出第二寄生电容。

15、同时,第一寄生电容、第二寄生电容和第三寄生电容的总和可以通过传统测试结构和测试方法获得,结合前述测出的第一寄生电容、第二寄生电容,可以获得第三寄生电容。

16、采用所述寄生电容的测试结构进行电容测试,测试方法简单、易于操作,可以分别获得单个寄生电容,克服了传统测试结构和测试方法只能获得寄生电容总和的问题,为后续分析单个寄生电容对器件性能的影响提供数据支撑。

技术特征:

1.一种寄生电容的测试结构,其特征在于,包括第一测试结构、第二测试结构及第三测试结构;

2.根据权利要求1所述的寄生电容的测试结构,其特征在于,所述第一水平间距为28nm~0.5μm。

3.根据权利要求1所述的寄生电容的测试结构,其特征在于,所述第一宽度为0.01μm~5μm。

4.根据权利要求1所述的寄生电容的测试结构,其特征在于,所述第二宽度为0.01μm~0.05μm。

5.根据权利要求1所述的寄生电容的测试结构,其特征在于,所述第二水平间距不小于5μm。

6.根据权利要求1所述的寄生电容的测试结构,其特征在于,所述测试结构还包括第四测试结构,用于测试所述第一寄生电容、所述第二寄生电容和所述第三寄生电容之和,其中所述第四测试结构与所述第一测试结构间仅所述接触孔结构的数量不同,且所述第四测试结构和所述第三测试结构的接触孔结构数量相同。

7.一种寄生电容的测试方法,其特征在于,对权利要求1至5任一项所述的测试结构进行测试,所述测试方法包括:

8.根据权利要求7所述的寄生电容的测试方法,其特征在于,进行电容测试时,使所述第一测试衬垫接地,并在所述第二测试衬垫上施加偏置电压。

9.根据权利要求8所述的寄生电容的测试方法,其特征在于,所述偏置电压为被测结构的工作电压。

10.根据权利要求7所述的寄生电容的测试方法,其特征在于,对第四测试结构进行测试,获得所述第一寄生电容、第二寄生电容和第三寄生电容之和,所述第四测试结构与所述第一测试结构间仅所述接触孔结构的数量不同,且所述第四测试结构和所述第三测试结构的接触孔结构数量相同。

技术总结

本申请提供一种寄生电容的测试结构和测试方法,所述测试结构包括第一测试结构、第二测试结构及第三测试结构,第一测试结构、第二测试结构及第三测试结构均包括位于衬底上的栅极结构、位于衬底中的源漏结构以及接触孔结构,其中栅极结构电连接至第一测试衬垫,并与衬底间形成第一寄生电容,源漏结构与栅极结构间形成第二寄生电容,接触孔结构电连接至第二测试衬垫,并与栅极结构间形成第三寄生电容,第一测试结构用于测试第一寄生电容和第二寄生电容之和,第二测试结构用于测试第二寄生电容,第三测试结构用于测试第二寄生电容。本申请技术方案的测试结构和测试方法能够测试出单个寄生电容。

技术研发人员:牛刚

受保护的技术使用者:中芯国际集成电路制造(天津)有限公司

技术研发日:

技术公布日:2024/3/21

- 还没有人留言评论。精彩留言会获得点赞!