半导体装置的制作方法

1.本发明涉及半导体装置,特别涉及具有沟槽栅极的半导体装置。

背景技术:

2.作为具有沟槽栅极的半导体装置,典型地,可以举出绝缘栅型双极晶体管(igbt:insulated gate bipolar transistor)。

3.igbt的基本结构为如下结构,即,在半导体基板的一个主面内设置沟槽,由栅极绝缘膜将沟槽的内表面覆盖,具有多个在内表面被栅极绝缘膜覆盖的沟槽内埋入有栅极电极的沟槽栅极。

4.相对于此,在专利文献1所公开的igbt中,公开了在相邻的沟槽栅极间设置有不作为栅极起作用的大于或等于1个哑沟槽栅极的结构。例如,在专利文献1的图1中,在相邻的沟槽栅极间设置3个哑沟槽栅极,它们中的中央的哑沟槽栅极被赋予栅极电位,成为有源哑沟槽栅极,其两侧的哑沟槽栅极成为被赋予发射极电位的隔离哑沟槽栅极。

5.这些哑沟槽栅极之上被连续的层间绝缘膜覆盖,哑沟槽栅极间的p型基极区域未连接于发射极电位而是成为浮置状态。

6.通过采用这样的结构,配置被赋予栅极电位的有源哑沟槽栅极和在其两侧未被赋予发射极电位的浮置的p型基极区域,增大了igbt的栅极和集电极之间的栅极-集电极间电容(反馈电容)cgc。增大反馈电容(cgc)的原因在于,在漏极电压v相对于时间t的变动即dv/dt恒定的条件下降低导通损耗,提高由反馈电容(cgc)相对于栅极-发射极间电容cge的电容比规定的栅极电容比cgc/cge。

7.专利文献1:日本专利第6253769号公报

8.如上所述,在现有的半导体装置中,由于在半导体基板的一个主面内即集电极层的上方设置有有源哑沟槽栅极,因此在导通时从集电极层注入的空穴使浮置的p型基极区域的电位产生变动,由此在有源哑沟槽栅极流过位移电流,栅极电压被偏置,因此即使增大栅极电阻(rg)也无法减小dv/dt,即dv/dt的栅极电阻控制性降低,在dv/dt低的区域中有可能导致导通损耗的增加。

技术实现要素:

9.本发明就是为了解决上述那样的问题而提出的,其目的在于提供使dv/dt的控制性提高,降低了导通损耗的半导体装置。

10.本发明涉及的半导体装置在共通的半导体基板形成了晶体管和二极管,所述半导体基板具有:晶体管区域,其形成有所述晶体管;以及二极管区域,其形成有所述二极管,所述二极管区域具有:第1导电型的第1半导体层,其设置于所述半导体基板的第2主面侧;第1导电型的第2半导体层,其设置于所述第1半导体层之上;第2导电型的第3半导体层,其与所述第2半导体层相比设置于所述半导体基板的第1主面侧;第1主电极,其对所述二极管赋予第1电位;第2主电极,其对所述二极管赋予第2电位;以及至少1个哑有源沟槽栅极,其设置

为从所述半导体基板的所述第1主面到达所述第2半导体层,所述至少1个哑有源沟槽栅极在两个侧面的至少一者侧具有未被赋予所述第1电位而是成为浮置状态的所述第3半导体层,对所述至少1个哑有源沟槽栅极赋予所述晶体管的栅极电位。

11.发明的效果

12.根据本发明涉及的半导体装置,在二极管区域,在两个侧面的至少一者侧具有未被赋予第1电位而是成为浮置状态的第3半导体层,具有被赋予晶体管的栅极电位的至少1个哑有源沟槽栅极,因此能够得到漏极电压v相对于时间t的变动即dv/dt的控制性提高,导通损耗降低的半导体装置。

附图说明

13.图1是表示rc-igbt即半导体装置的俯视图。

14.图2是表示rc-igbt即半导体装置的俯视图。

15.图3是rc-igbt中的igbt区域的局部俯视图。

16.图4是rc-igbt中的igbt区域的局部剖视图。

17.图5是rc-igbt中的igbt区域的局部剖视图。

18.图6是rc-igbt中的二极管区域的局部俯视图。

19.图7是rc-igbt中的二极管区域的局部剖视图。

20.图8是rc-igbt中的二极管区域的局部剖视图。

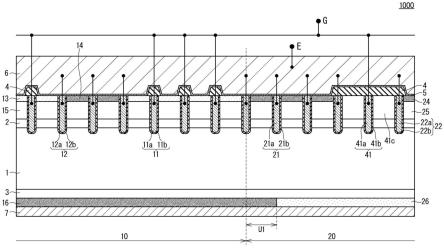

21.图9是rc-igbt的igbt区域和二极管区域的边界部分的剖视图。

22.图10是rc-igbt的igbt区域和末端区域的边界部分的剖视图。

23.图11是rc-igbt的igbt区域和末端区域的边界部分的剖视图。

24.图12是说明rc-igbt的制造方法的剖视图。

25.图13是说明rc-igbt的制造方法的剖视图。

26.图14是说明rc-igbt的制造方法的剖视图。

27.图15是说明rc-igbt的制造方法的剖视图。

28.图16是说明rc-igbt的制造方法的剖视图。

29.图17是说明rc-igbt的制造方法的剖视图。

30.图18是说明rc-igbt的制造方法的剖视图。

31.图19是说明rc-igbt的制造方法的剖视图。

32.图20是说明rc-igbt的制造方法的剖视图。

33.图21是说明rc-igbt的制造方法的剖视图。

34.图22是说明rc-igbt的制造方法的剖视图。

35.图23是表示实施方式1涉及的rc-igbt的结构的局部剖视图。

36.图24是表示实施方式1涉及的rc-igbt的变形例的结构的局部剖视图。

37.图25是表示实施方式2涉及的rc-igbt的结构的局部剖视图。

38.图26是表示实施方式2涉及的rc-igbt的变形例1的结构的局部剖视图。

39.图27是表示实施方式2涉及的rc-igbt的变形例2的结构的局部剖视图。

40.图28是表示实施方式3涉及的rc-igbt的结构的局部剖视图。

41.图29是表示实施方式3涉及的rc-igbt的变形例的结构的局部剖视图。

42.图30是表示实施方式4涉及的rc-igbt的结构的局部剖视图。

43.图31是表示实施方式5涉及的半导体装置的俯视图。

44.图32是实施方式5涉及的半导体装置中的二极管区域的局部剖视图。

45.图33是实施方式5涉及的半导体装置中的igbt区域的局部剖视图。

46.图34是实施方式5涉及的半导体装置中的二极管区域的局部俯视图。

47.图35是实施方式5涉及的半导体装置中的二极管区域的局部剖视图。

48.图36是实施方式5涉及的半导体装置中的二极管区域的局部剖视图。

具体实施方式

49.《前言》

50.在下面的说明中,n型及p型表示半导体的导电型,在本发明中,以第1导电型为n型,第2导电型为p型进行说明,但也可以以第1导电型为p型,以第2导电型为n型。另外,n-型表示杂质浓度比n型低的浓度,n

+

型表示杂质浓度比n型高的浓度。相同地,p-型表示杂质浓度比p型低的浓度,p

+

型表示杂质浓度比p型高的浓度。

51.另外,附图只是示意性地示出的,在不同的附图中各自示出的图像的尺寸及位置的相互关系未必是准确地记载的,能够进行适当变更。另外,在下面的说明中,对相同的结构要素标注相同的标号而进行图示,它们的名称及功能也相同。因此,有时会省略对它们的详细说明。

52.另外,在下面的说明中,有时使用“上”、“下”、“侧”、“表”及“背”等表示特定的位置及方向的术语,这些术语只是为了容易对实施方式的内容进行理解,出于方便而使用的,与实际实施时的方向没有关系。

53.下面,在实施方式的说明之前,对在共通的半导体基板设置有igbt和续流二极管(fwd:free wheeling diode)的反向导通igbt(rc-igbt:reverse conducting igbt)进行说明。

54.图1是表示rc-igbt即半导体装置的俯视图。另外,图2是表示其它结构的rc-igbt即半导体装置的俯视图。图1所示的半导体装置100条带状排列地设置有igbt区域10和二极管区域20,可以简称为“条带型”。就图2所示的半导体装置101而言,在纵向和横向设置多个二极管区域20,在二极管区域20的周围设置有igbt区域10,可以简称为“岛型”。

55.(1)条带型的整体平面构造

56.在图1中,半导体装置100在1个半导体装置内具有igbt区域10和二极管区域20。igbt区域10及二极管区域20从半导体装置100的一端侧延伸至另一端侧,在与igbt区域10及二极管区域20的延伸方向正交的方向上交替地设置为条带状。在图1中示出3个igbt区域10、2个二极管区域,以全部二极管区域20都被igbt区域10夹着的结构示出,但igbt区域10和二极管区域20的数量并不限于此,igbt区域10的数量可以是大于或等于3个,也可以是小于或等于3个,二极管区域20的数量可以是大于或等于2个,也可以是小于或等于2个。另外,也可以是将图1的igbt区域10和二极管区域20的位置交换的结构,还可以是全部igbt区域10都被二极管区域20夹着的结构。另外,igbt区域10和二极管区域20也可以是各自1个1个彼此相邻地设置的结构。

57.如图1所示,与纸面下侧的igbt区域10相邻地设置有焊盘区域40。焊盘区域40是设

置用于对半导体装置100进行控制的控制焊盘410的区域。将igbt区域10及二极管区域20合起来称为单元区域。为了半导体装置100的耐压保持,在将单元区域及焊盘区域40合起来的区域的周围设置有末端区域30。能够在末端区域30适当选择性地设置公知的耐压保持构造。耐压保持构造例如可以是在半导体装置100的表面侧即第1主面侧设置通过p型半导体的p型末端阱层将单元区域包围的flr(field limiting ring)及通过具有浓度梯度的p型阱层将单元区域包围的vld(variation of lateral doping)而构成的,flr所使用的环状的p型末端阱层的数量及vld所使用的浓度分布可以根据半导体装置100的耐压设计而适当选择。另外,也可以遍及焊盘区域40的大致整个区域而设置p型末端阱层,也可以在焊盘区域40设置igbt单元及二极管单元。

58.控制焊盘410例如可以是电流感测焊盘410a、开尔文发射极焊盘410b、栅极焊盘410c、温度感测二极管焊盘410d、410e。电流感测焊盘410a是用于对在半导体装置100的单元区域流动的电流进行检测的控制焊盘,并且是以在半导体装置100的单元区域流动电流时流过在单元区域整体流动的电流的几分之一至几万分之一的电流的方式与单元区域的一部分igbt单元或二极管单元电连接的控制焊盘。

59.开尔文发射极焊盘410b及栅极焊盘410c是被施加用于对半导体装置100进行通断控制的栅极驱动电压的控制焊盘。开尔文发射极焊盘410b与igbt单元的p型基极层电连接,栅极焊盘410c与igbt单元的栅极沟槽电极电连接。开尔文发射极焊盘410b和p型基极层也可以经由p

+

型接触层而电连接。温度感测二极管焊盘410d、410e是与设置于半导体装置100的温度感测二极管的阳极及阴极电连接的控制焊盘。对在单元区域内设置的未图示的温度感测二极管的阳极和阴极之间的电压进行测定,对半导体装置100的温度进行测定。

60.(2)岛型的整体平面构造

61.在图2中,半导体装置101在1个半导体装置内具有igbt区域10和二极管区域20。二极管区域20在半导体装置内的纵向及横向分别排列配置有多个,二极管区域20的周围被igbt区域10包围。即,在igbt区域10内多个二极管区域20设置为岛状。在图2中示出二极管区域20以在纸面左右方向具有4列、在纸面上下方向具有2行的矩阵状设置的结构,但二极管区域20的个数及配置并不限于此,只要是在igbt区域10内散布地设置1个或多个二极管区域20,各个二极管区域20的周围被igbt区域10包围的结构即可。

62.如图2所示,在igbt区域10的纸面下侧与其相邻地设置有焊盘区域40。焊盘区域40是设置用于对半导体装置101进行控制的控制焊盘410的区域。将igbt区域10及二极管区域20合起来称为单元区域。为了半导体装置101的耐压保持,在将单元区域及焊盘区域40合起来的区域的周围设置有末端区域30。能够在末端区域30适当选择性地设置公知的耐压保持构造。耐压保持构造例如可以是在半导体装置101的表面侧即第1主面侧设置通过p型半导体的p型末端阱层将单元区域及焊盘区域40合起来的区域包围的flr(field limiting ring)及通过具有浓度梯度的p型阱层将单元区域包围的vld(variation of lateral doping)而构成的,flr所使用的环状的p型末端阱层的数量及vld所使用的浓度分布可以根据半导体装置101的耐压设计而适当选择。另外,也可以遍及焊盘区域40的大致整个区域而设置p型末端阱层,也可以在焊盘区域40设置igbt单元及二极管单元。

63.控制焊盘410例如可以是电流感测焊盘410a、开尔文发射极焊盘410b、栅极焊盘410c、温度感测二极管焊盘410d、410e。电流感测焊盘410a是用于对在半导体装置101的单

元区域流动的电流进行检测的控制焊盘,并且是以在半导体装置101的单元区域流动电流时流过在单元区域整体流动的电流的几分之一至几万分之一的电流的方式与单元区域的一部分igbt单元或二极管单元电连接的控制焊盘。

64.开尔文发射极焊盘410b及栅极焊盘410c是被施加用于对半导体装置101进行通断控制的栅极驱动电压的控制焊盘。开尔文发射极焊盘410b与igbt单元的p型基极层及n

+

型源极层电连接,栅极焊盘410c与igbt单元的栅极沟槽电极电连接。开尔文发射极焊盘410b和p型基极层也可以经由p

+

型接触层而电连接。温度感测二极管焊盘410d、410e是与设置于半导体装置101的温度感测二极管的阳极及阴极电连接的控制焊盘。对在单元区域内设置的未图示的温度感测二极管的阳极和阴极之间的电压进行测定,对半导体装置101的温度进行测定。

65.(3)igbt区域10的通常构造

66.图3是表示rc-igbt即半导体装置的igbt区域的结构的局部放大俯视图。另外,图4及图5是表示rc-igbt即半导体装置的igbt区域的结构的剖视图。图3放大表示图1所示的半导体装置100或图2所示的半导体装置101中的由虚线包围的区域82。图4是图3所示的半导体装置100或半导体装置101的虚线a-a处的箭头方向剖视图,图5是图3所示的半导体装置100或半导体装置101的虚线b-b处的箭头方向剖视图。

67.如图3所示,在igbt区域10,有源沟槽栅极11和哑沟槽栅极12是以条带状设置的。就半导体装置100而言,有源沟槽栅极11及哑沟槽栅极12在igbt区域10的长度方向上延伸,igbt区域10的长度方向成为有源沟槽栅极11及哑沟槽栅极12的长度方向。另一方面,就半导体装置101而言,在igbt区域10,长度方向和宽度方向没有特别地进行区分,可以将纸面左右方向设为有源沟槽栅极11及哑沟槽栅极12的长度方向,也可以将纸面上下方向设为有源沟槽栅极11及哑沟槽栅极12的长度方向。

68.有源沟槽栅极11是在形成于半导体基板的沟槽内隔着栅极沟槽绝缘膜11b设置栅极沟槽电极11a而构成的。哑沟槽栅极12是在形成于半导体基板的沟槽内隔着哑沟槽绝缘膜12b设置哑沟槽电极12a而构成的。有源沟槽栅极11的栅极沟槽电极11a与栅极焊盘410c电连接。哑沟槽栅极12的哑沟槽电极12a与在半导体装置100或半导体装置101的第1主面之上设置的发射极电极电连接。

69.n

+

型源极层13设置为在有源沟槽栅极11的宽度方向上的两侧与栅极沟槽绝缘膜11b接触。n

+

型源极层13为作为n型杂质具有例如砷或磷等的半导体层,n型杂质的浓度为1.0

×

10

17

/cm3~1.0

×

10

20

/cm3。n

+

型源极层13是沿有源沟槽栅极11的延伸方向与p

+

型接触层14交替地设置的。在相邻的2个哑沟槽栅极12之间也设置p

+

型接触层14。p

+

型接触层14为作为p型杂质具有例如硼或铝等的半导体层,p型杂质的浓度为1.0

×

10

15

/cm3~1.0

×

10

20

/cm3。

70.如图3所示,在半导体装置100或半导体装置101的igbt区域10处呈如下结构,即,在并排的3个有源沟槽栅极11的旁边排列3个哑沟槽栅极12,在并排的3个哑沟槽栅极12的旁边排列3个有源沟槽栅极11。如上所述,igbt区域10呈有源沟槽栅极11的组和哑沟槽栅极12的组交替地排列的结构。在图3中,1个有源沟槽栅极11的组所包含的有源沟槽栅极11的数量为3个,但只要是大于或等于1个即可。另外,1个哑沟槽栅极12的组所包含的哑沟槽栅极12的数量可以大于或等于1个,哑沟槽栅极12的数量也可以为0。即,也可以将设置于igbt

区域10的沟槽全部设为有源沟槽栅极11。

71.图4是半导体装置100或半导体装置101的图3中的虚线a-a处的箭头方向剖视图,是igbt区域10的剖视图。半导体装置100或半导体装置101具有由半导体基板构成的第2半导体层即n-型漂移层1。n-型漂移层1为作为n型杂质具有例如砷或磷等的半导体层,n型杂质的浓度为1.0

×

10

12

/cm3~1.0

×

10

15

/cm3。半导体基板在图4中是从n

+

型源极层13及p

+

型接触层14至p型集电极层16为止的范围。将图4中n

+

型源极层13及p

+

型接触层14的纸面上端称为半导体基板的第1主面,将p型集电极层16的纸面下端称为半导体基板的第2主面。半导体基板的第1主面为半导体装置100的表面侧的主面,半导体基板的第2主面为半导体装置100的背面侧的主面。半导体装置100在单元区域即igbt区域10处,在第1主面和与第1主面相对的第2主面之间具有n-型漂移层1。

72.如图4所示,在igbt区域10,在n-型漂移层1的第1主面侧设置有n型杂质的浓度比n-型漂移层1高的n型载流子积蓄层2。n型载流子积蓄层2为作为n型杂质具有例如砷或磷等的半导体层,n型杂质的浓度为1.0

×

10

13

/cm3~1.0

×

10

17

/cm3。此外,半导体装置100或半导体装置101也可以是不设置n型载流子积蓄层2,而在图4所示的n型载流子积蓄层2的区域也设置有n-型漂移层1的结构。通过设置n型载流子积蓄层2,能够降低在igbt区域10流动电流时的通电损耗。也可以将n型载流子积蓄层2和n-型漂移层1合起来称为漂移层。

73.n型载流子积蓄层2是通过将n型杂质向构成n-型漂移层1的半导体基板进行离子注入,之后通过退火使注入的n型杂质在n-型漂移层1即半导体基板内扩散而形成的。

74.在n型载流子积蓄层2的第1主面侧设置有p型基极层15。p型基极层15为作为p型杂质具有例如硼或铝等的半导体层,p型杂质的浓度为1.0

×

10

12

/cm3~1.0

×

10

19

/cm3。p型基极层15与有源沟槽栅极11的栅极沟槽绝缘膜11b接触。在p型基极层15的第1主面侧与有源沟槽栅极11的栅极沟槽绝缘膜11b接触地设置有n

+

型源极层13,在剩余区域设置有p

+

型接触层14。n

+

型源极层13及p

+

型接触层14构成半导体基板的第1主面。此外,p

+

型接触层14为p型杂质的浓度比p型基极层15高的区域,在需要区分p

+

型接触层14和p型基极层15的情况下可以对各自单独地进行称呼,也可以将p

+

型接触层14和p型基极层15合起来称为p型基极层。

75.另外,就半导体装置100或半导体装置101而言,在n-型漂移层1的第2主面侧设置有n型杂质的浓度比n-型漂移层1高的n型缓冲层3。n型缓冲层3是为了对在半导体装置100成为断开状态时从p型基极层15延伸至第2主面侧的耗尽层击穿进行抑制而设置的。n型缓冲层3例如可以是注入磷(p)或质子(h

+

)而形成的,也可以是注入磷(p)以及质子(h

+

)这两者而形成的。n型缓冲层3的n型杂质的浓度为1.0

×

10

12

/cm3~1.0

×

10

18

/cm3。

76.此外,半导体装置100或半导体装置101也可以是不设置n型缓冲层3,而在图4所示的n型缓冲层3的区域也设置了n-型漂移层1的结构。也可以将n型缓冲层3和n-型漂移层1合起来称为漂移层。

77.半导体装置100或半导体装置101在n型缓冲层3的第2主面侧设置有p型集电极层16。即,在n-型漂移层1和第2主面之间设置有p型集电极层16。p型集电极层16为作为p型杂质具有例如硼或铝等的半导体层,p型杂质的浓度为1.0

×

10

16

/cm3~1.0

×

10

20

/cm3。p型集电极层16构成半导体基板的第2主面。p型集电极层16不仅设置在igbt区域10,而且还设置在末端区域30,p型集电极层16中的设置于末端区域30的部分构成p型末端集电极层16a。另外,p型集电极层16的一部分也可以设置为从igbt区域10伸出到二极管区域20。

78.如图4所示,就半导体装置100或半导体装置101而言,形成有从半导体基板的第1主面贯穿p型基极层15而到达n-型漂移层1的沟槽。通过在沟槽内隔着栅极沟槽绝缘膜11b设置栅极沟槽电极11a,从而构成有源沟槽栅极11。栅极沟槽电极11a隔着栅极沟槽绝缘膜11b与n-型漂移层1相对。另外,通过在沟槽内隔着哑沟槽绝缘膜12b设置哑沟槽电极12a,从而构成哑沟槽栅极12。哑沟槽电极12a隔着哑沟槽绝缘膜12b与n-型漂移层1相对。有源沟槽栅极11的栅极沟槽绝缘膜11b与p型基极层15及n

+

型源极层13接触。如果将栅极驱动电压施加于栅极沟槽电极11a,则在与有源沟槽栅极11的栅极沟槽绝缘膜11b接触的p型基极层15形成沟道。

79.如图4所示,在有源沟槽栅极11的栅极沟槽电极11a之上设置有层间绝缘膜4。在半导体基板的第1主面的没有设置层间绝缘膜4的区域之上及层间绝缘膜4之上形成有阻挡金属5。阻挡金属5例如可以是包含钛(ti)的导体,例如可以是氮化钛,可以是使钛和硅(si)合金化后的tisi。如图4所示,阻挡金属5与n

+

型源极层13、p

+

型接触层14及哑沟槽电极12a进行欧姆接触,与n

+

型源极层13、p

+

型接触层14及哑沟槽电极12a电连接。在阻挡金属5之上设置发射极电极6。发射极电极6例如可以通过铝硅合金(al-si类合金)等铝合金形成,也可以是在由铝合金形成的电极之上通过化学镀或电镀形成了镀膜的由多层金属膜构成的电极。通过化学镀或电镀形成的镀膜例如可以是镍(ni)镀膜。另外,在存在相邻的层间绝缘膜4间等微小且发射极电极6无法良好地埋入的区域的情况下,也可以将与发射极电极6相比埋入性良好的钨配置于微小的区域,在钨之上设置发射极电极6。此外,也可以不设置阻挡金属5,在n

+

型源极层13、p

+

型接触层14及哑沟槽电极12a之上设置发射极电极6。另外,也可以仅在n

+

型源极层13等n型的半导体层之上设置阻挡金属5。可以将阻挡金属5和发射极电极6合起来称为发射极电极。此外,在图4中示出在哑沟槽栅极12的哑沟槽电极12a之上没有设置层间绝缘膜4的图,但也可以在哑沟槽栅极12的哑沟槽电极12a之上形成层间绝缘膜4。当在哑沟槽栅极12的哑沟槽电极12a之上形成了层间绝缘膜4的情况下,在其它剖面中将发射极电极6和哑沟槽电极12a电连接即可。

80.在p型集电极层16的第2主面侧设置集电极(collector)电极(electrode)7。集电极电极7也可以与发射极电极6相同地,由铝合金或由铝合金和镀膜构成。另外,集电极电极7也可以是与发射极电极6不同的结构。集电极电极7与p型集电极层16进行欧姆接触,与p型集电极层16电连接。

81.图5是半导体装置100或半导体装置101的图3中的虚线b-b处的箭头方向剖视图,是igbt区域10的剖视图。与图4所示的虚线a-a处的箭头方向剖视图在如下方面不同,即,在图5的虚线b-b处的箭头方向剖面中观察不到与有源沟槽栅极11接触地在半导体基板的第1主面侧设置的n

+

型源极层13。即,如图3所示,n

+

型源极层13选择性地设置于p型基极层的第1主面侧。此外,这里所说的p型基极层是指将p型基极层15和p

+

型接触层14合起来称呼的p型基极层。

82.(4)二极管区域20的通常构造

83.图6是表示rc-igbt即半导体装置的二极管区域的结构的局部放大俯视图。另外,图7及图8是表示rc-igbt即半导体装置的二极管区域的结构的剖视图。图6放大示出图1所示的半导体装置100或半导体装置101中的由虚线包围的区域83。图7是图6所示的半导体装置100的虚线c-c处的箭头方向剖视图。图8是图6所示的半导体装置100的虚线d-d处的箭头

方向剖视图。

84.二极管沟槽栅极21沿半导体装置100或半导体装置101的第1主面从单元区域即二极管区域20的一端侧向相对的另一端侧延伸。二极管沟槽栅极21是通过在二极管区域20的形成于半导体基板的沟槽内隔着二极管沟槽绝缘膜21b设置二极管沟槽电极21a而构成的。二极管沟槽电极21a隔着二极管沟槽绝缘膜21b与n-型漂移层1相对。在相邻的2个二极管沟槽栅极21之间设置有p

+

型接触层24及第3半导体层即p型阳极层25。p

+

型接触层24为作为p型杂质具有例如硼或铝等的半导体层,p型杂质的浓度为1.0

×

10

15

/cm3~1.0

×

10

20

/cm3。p型阳极层25为作为p型杂质具有例如硼或铝等的半导体层,p型杂质的浓度为1.0

×

10

12

/cm3~1.0

×

10

19

/cm3。p

+

型接触层24和p型阳极层25在二极管沟槽栅极21的长度方向上交替地设置。

85.图7是半导体装置100或半导体装置101的图6中的虚线c-c处的箭头方向剖视图,是二极管区域20的剖视图。半导体装置100或半导体装置101在二极管区域20也与igbt区域10相同地具有由半导体基板构成的n-型漂移层1。二极管区域20的n-型漂移层1和igbt区域10的n-型漂移层1连续地一体构成,通过同一半导体基板构成。在图7中,半导体基板为从p

+

型接触层24至第1半导体层即n

+

型阴极层26为止的范围。将图7中p

+

型接触层24的纸面上端称为半导体基板的第1主面,将n

+

型阴极层26的纸面下端称为半导体基板的第2主面。二极管区域20的第1主面和igbt区域10的第1主面为同一面,二极管区域20的第2主面和igbt区域10的第2主面为同一面。

86.如图7所示,在二极管区域20也与igbt区域10相同地,在n-型漂移层1的第1主面侧设置有n型载流子积蓄层2,在n-型漂移层1的第2主面侧设置有n型缓冲层3。在二极管区域20设置的n型载流子积蓄层2及n型缓冲层3呈与在igbt区域10设置的n型载流子积蓄层2及n型缓冲层3相同的结构。此外,并非必须在igbt区域10及二极管区域20设置n型载流子积蓄层2,即使在igbt区域10设置n型载流子积蓄层2的情况下,也可以设为在二极管区域20没有设置n型载流子积蓄层2的结构。另外,与igbt区域10相同地,可以将n-型漂移层1、n型载流子积蓄层2及n型缓冲层3合起来称为漂移层。

87.在n型载流子积蓄层2的第1主面侧设置有p型阳极层25。p型阳极层25设置于n-型漂移层1和第1主面之间。也可以将p型阳极层25的p型杂质的浓度设为与igbt区域10的p型基极层15相同的浓度,同时形成p型阳极层25和p型基极层15。另外,也可以构成为将p型阳极层25的p型杂质的浓度设得比igbt区域10的p型基极层15的p型杂质的浓度低,使得在二极管动作时注入至二极管区域20的空穴的量减少。通过使在二极管动作时注入的空穴的量减少,能够降低二极管动作时的恢复损耗。

88.在p型阳极层25的第1主面侧设置有p

+

型接触层24。p

+

型接触层24的p型杂质的浓度可以设为与igbt区域10的p

+

型接触层14的p型杂质相同的浓度,也可以设为不同的浓度。p

+

型接触层24构成半导体基板的第1主面。此外,p

+

型接触层24为p型杂质的浓度比p型阳极层25高的区域,在需要区分p

+

型接触层24和p型阳极层25的情况下可以对各自单独地进行称呼,也可以将p

+

型接触层24和p型阳极层25合起来称为p型阳极层。

89.在二极管区域20,在n型缓冲层3的第2主面侧设置有n

+

型阴极层26。n

+

型阴极层26设置于n-型漂移层1和第2主面之间。n

+

型阴极层26为作为n型杂质具有例如砷或磷等的半导体层,n型杂质的浓度为1.0

×

10

16

/cm3~1.0

×

10

21

/cm3。如图2所示,n

+

型阴极层26设置于二

极管区域20的一部分或全部。n

+

型阴极层26构成半导体基板的第2主面。此外,虽然未图示,但也可以进一步选择性地将p型杂质注入至如上所述形成了n

+

型阴极层26的区域,使形成了n

+

型阴极层26的区域的一部分成为p型半导体而设置p

+

型阴极层。将这样沿半导体基板的第2主面交替地配置了n

+

型阴极层和p

+

型阴极层的二极管称为rfc(relaxed field of cathode)二极管。

90.如图7所示,在半导体装置100或半导体装置101的二极管区域20,形成有从半导体基板的第1主面贯穿p型阳极层25而到达n-型漂移层1的沟槽。通过在二极管区域20的沟槽内隔着二极管沟槽绝缘膜21b设置二极管沟槽电极21a,从而构成二极管沟槽栅极21。二极管沟槽电极21a隔着二极管沟槽绝缘膜21b与n-型漂移层1相对。

91.如图7所示,在二极管沟槽电极21a及p

+

型接触层24之上设置有阻挡金属5。阻挡金属5与二极管沟槽电极21a及p

+

型接触层24进行欧姆接触,与二极管沟槽电极及p

+

型接触层24电连接。阻挡金属5可以为与igbt区域10的阻挡金属5相同的结构。在阻挡金属5之上设置发射极电极6。在二极管区域20设置的发射极电极6与在igbt区域10设置的发射极电极6连续地形成。此外,也可以与igbt区域10的情况相同地,不设置阻挡金属5,使二极管沟槽电极21a及p

+

型接触层24与发射极电极6进行欧姆接触。此外,在图7中示出在二极管沟槽栅极21的二极管沟槽电极21a之上没有设置层间绝缘膜4的图,但也可以在二极管沟槽栅极21的二极管沟槽电极21a之上形成层间绝缘膜4。当在二极管沟槽栅极21的二极管沟槽电极21a之上形成了层间绝缘膜4的情况下,在其它剖面中将发射极电极6和二极管沟槽电极21a电连接即可。

92.在n

+

型阴极层26的第2主面侧设置集电极电极7。与发射极电极6相同地,二极管区域20的集电极电极7与在igbt区域10设置的集电极电极7连续地形成。集电极电极7与n

+

型阴极层26进行欧姆接触,与n

+

型阴极层26电连接,也作为阴极电极起作用。

93.图8是半导体装置100或半导体装置101的图6中的虚线d-d处的箭头方向剖视图,是二极管区域20的箭头方向剖视图。与图7所示的虚线c-c处的箭头方向剖视图的区别在于,在p型阳极层25和阻挡金属5之间没有设置p

+

型接触层24,p型阳极层25构成半导体基板的第1主面。即,图7所示的p

+

型接触层24选择性地设置于p型阳极层25的第1主面侧。

94.(5)igbt区域10和二极管区域20的边界区域

95.图9是表示rc-igbt即半导体装置的igbt区域和二极管区域的边界的结构的剖视图。图9是图1所示的半导体装置100或半导体装置101的虚线g-g处的箭头方向剖视图。

96.如图9所示,在igbt区域10的第2主面侧设置的p型集电极层16设置为从igbt区域10和二极管区域20的边界向二极管区域20侧伸出距离u1。这样,通过将p型集电极层16设置为伸出到二极管区域20,从而能够增大二极管区域20的n

+

型阴极层26和有源沟槽栅极11的距离,即使在续流二极管动作时对栅极沟槽电极11a施加了栅极驱动电压的情况下,也能够对电流从igbt区域10的与有源沟槽栅极11相邻地形成的沟道流动至n

+

型阴极层26进行抑制。距离u1例如可以为100μm。此外,根据rc-igbt即半导体装置100或半导体装置101的用途,距离u1也可以为零或比100μm小的距离。

97.(6)末端区域30的通常构造

98.图10及图11是表示rc-igbt即半导体装置的末端区域的结构的剖视图。图10是图1或图2中的虚线e-e处的箭头方向剖视图,是从igbt区域10到末端区域30的剖视图。另外,图

11是图1中的虚线f-f处的箭头方向剖视图,是从二极管区域20到末端区域30的剖视图。

99.如图10及图11所示,半导体装置100的末端区域30在半导体基板的第1主面和第2主面之间具有n-型漂移层1。末端区域30的第1主面及第2主面分别与igbt区域10及二极管区域20的第1主面及第2主面为同一面。另外,末端区域30的n-型漂移层1分别与igbt区域10及二极管区域20的n-型漂移层1为相同结构,连续地一体形成。

100.在n-型漂移层1的第1主面侧即半导体基板的第1主面和n-型漂移层1之间设置有p型末端阱层31。p型末端阱层31为作为p型杂质具有例如硼或铝等的半导体层,p型杂质的浓度为1.0

×

10

14

/cm3~1.0

×

10

19

/cm3。p型末端阱层31设置为将包含igbt区域10及二极管区域20的单元区域包围。p型末端阱层31设置为多个环状,p型末端阱层31的设置数量是根据半导体装置100或半导体装置101的耐压设计而适当选择的。另外,在p型末端阱层31的更外缘侧设置有n

+

型沟道截断层32,n

+

型沟道截断层32将p型末端阱层31包围。

101.在n-型漂移层1和半导体基板的第2主面之间设置有p型末端集电极层16a。p型末端集电极层16a与在单元区域设置的p型集电极层16连续地一体形成。因此,也可以连同p型末端集电极层16a在内称为p型集电极层16。另外,在如图1所示的半导体装置100那样二极管区域20与末端区域30相邻地设置的结构中,如图11所示,p型末端集电极层16a设置为二极管区域20侧的端部向二极管区域20伸出距离u2。这样,通过将p型末端集电极层16a设置为伸出到二极管区域20,从而能够增大二极管区域20的n

+

型阴极层26与p型末端阱层31的距离,能够抑制p型末端阱层31作为二极管的阳极进行动作。距离u2例如可以为100μm。

102.在半导体基板的第2主面之上设置有集电极电极7。集电极电极7从包含igbt区域10及二极管区域20的单元区域至末端区域30为止连续地一体形成。另一方面,在末端区域30的半导体基板的第1主面之上设置与单元区域连续的发射极电极6、和与发射极电极6分离的末端电极6a。

103.发射极电极6和末端电极6a经由半绝缘性膜33而电连接。半绝缘性膜33例如可以是sinsin(semi-insulating silicon nitride:半绝缘性氮化硅膜)。末端电极6a与p型末端阱层31及n

+

型沟道截断层32经由在设置于末端区域30的第1主面之上的层间绝缘膜4形成的接触孔而电连接。另外,在末端区域30设置有将发射极电极6、末端电极6a及半绝缘性膜33覆盖的末端保护膜34。末端保护膜34例如可以由聚酰亚胺形成。

104.(7)rc-igbt的通常的制造方法

105.图12~图22是表示rc-igbt即半导体装置的制造方法的图。图12~图19是表示形成半导体装置100或半导体装置101的表面侧的工序的图,图20~图22是表示形成半导体装置100或半导体装置101的背面侧的工序的图。

106.首先,如图12所示准备构成n-型漂移层1的半导体基板。半导体基板例如可以使用通过fz(floating zone)法制作出的所谓的fz晶片或通过mcz(magnetic field applied czochralski)法制作出的所谓的mcz晶片,也可以是包含n型杂质的n型晶片。半导体基板所包含的n型杂质的浓度是根据制作的半导体装置的耐压而适当选择的,例如,就耐压为1200v的半导体装置而言,对n型杂质的浓度进行调整,使得构成半导体基板的n-型漂移层1的电阻率为40~120ω

·

cm左右。如图12所示,在准备半导体基板的工序中,半导体基板的整体为n-型漂移层1,但通过从这样的半导体基板的第1主面侧或第2主面侧注入p型或n型杂质离子,之后通过热处理等使其在半导体基板内扩散,从而形成p型或n型的半导体层,对

半导体装置100或半导体装置101进行制造。

107.如图12所示,构成n-型漂移层1的半导体基板具有成为igbt区域10及二极管区域20的区域。另外,虽然未图示,但在成为igbt区域10及二极管区域20的区域的周围具有成为末端区域30的区域。下面,主要对半导体装置100或半导体装置101的igbt区域10及二极管区域20的结构的制造方法进行说明,但可以通过公知的制造方法对半导体装置100或半导体装置101的末端区域30进行制作。例如,当在末端区域30形成具有p型末端阱层31的flr作为耐压保持构造的情况下,可以在对半导体装置100或半导体装置101的igbt区域10及二极管区域20进行加工前注入p型杂质离子而形成,也可以在将p型杂质向半导体装置100的igbt区域10或二极管区域20进行离子注入时同时注入p型杂质离子而形成。

108.接着,如图13所示,从半导体基板的第1主面侧注入磷(p)等n型杂质而形成n型载流子积蓄层2。另外,从半导体基板的第1主面侧注入硼(b)等p型杂质而形成p型基极层15及p型阳极层25。n型载流子积蓄层2、p型基极层15及p型阳极层25是通过在将杂质离子向半导体基板内注入后利用热处理使杂质离子扩散而形成的。n型杂质及p型杂质由于是在半导体基板的第1主面之上实施了掩模处理后进行离子注入,因此选择性地形成于半导体基板的第1主面侧。n型载流子积蓄层2、p型基极层15及p型阳极层25形成于igbt区域10及二极管区域20,在末端区域30与p型末端阱层31连接。此外,掩模处理是将抗蚀剂涂敷于半导体基板之上,使用照相制版技术在抗蚀剂的规定的区域形成开口,为了经由开口向半导体基板的规定的区域实施离子注入或实施蚀刻,在半导体基板之上形成掩模的处理。

109.p型基极层15及p型阳极层25也可以是同时对p型杂质进行离子注入而形成。在该情况下,p型基极层15和p型阳极层25的深度及p型杂质浓度相同且为相同结构。另外,也可以通过利用掩模处理分别将p型杂质向p型基极层15和p型阳极层25进行离子注入,从而使p型基极层15和p型阳极层25的深度及p型杂质浓度不同。

110.另外,在其它剖面中形成的p型末端阱层31也可以是与p型阳极层25同时对p型杂质进行离子注入而形成。在该情况下,能够将p型末端阱层31和p型阳极层25的深度及p型杂质浓度设为相同且设为相同结构。另外,也可以同时对p型杂质进行离子注入而形成p型末端阱层31和p型阳极层25,将p型末端阱层31和p型阳极层25的p型杂质浓度设为不同的浓度。在该情况下,将某一者或两者的掩模设为网格状的掩模,对开口率进行变更即可。

111.另外,也可以通过利用掩模处理将p型杂质分别离子注入至p型末端阱层31及p型阳极层25,从而使p型末端阱层31及p型阳极层25的深度及p型杂质浓度不同。也可以同时对p型杂质进行离子注入而形成p型末端阱层31、p型基极层15、及p型阳极层25。

112.接着,如图14所示,通过掩模处理将n型杂质选择性地注入至igbt区域10的p型基极层15的第1主面侧而形成n

+

型源极层13。注入的n型杂质例如可以是砷(as)或磷(p)。另外,通过掩模处理,选择性地将p型杂质注入至igbt区域10的p型基极层15的第1主面侧而形成p

+

型接触层14,选择性地将p型杂质注入至二极管区域20的p型阳极层25的第1主面侧而形成p

+

型接触层24。注入的p型杂质例如可以是硼(b)或铝(al)。

113.接着,如图15所示,形成从半导体基板的第1主面侧贯穿p型基极层15及p型阳极层25而到达n-型漂移层1的沟槽8。在igbt区域10,贯穿n

+

型源极层13的沟槽8的侧壁构成n

+

型源极层13的一部分。沟槽8也可以通过如下方式形成,即,在半导体基板之上沉积了sio2等氧化膜后,通过掩模处理在形成沟槽8的部分的氧化膜形成开口,将形成了开口的氧化膜作

为掩模而对半导体基板进行蚀刻。在图15中,在igbt区域10和二极管区域20使沟槽8的间距相同地形成沟槽8,但也可以在igbt区域10和二极管区域20使沟槽8的间距不同。沟槽8的间距的俯视观察时的图案能够根据掩模处理的掩模图案而适当变更。

114.接着,如图16所示,在含有氧的环境中对半导体基板进行加热而在沟槽8的内壁及半导体基板的第1主面形成氧化膜9。在沟槽8的内壁形成的氧化膜9中的在igbt区域10的沟槽8形成的氧化膜9为有源沟槽栅极11的栅极沟槽绝缘膜11b及哑沟槽栅极12的哑沟槽绝缘膜12b。另外,在二极管区域20的沟槽8形成的氧化膜9为二极管沟槽绝缘膜21b。在半导体基板的第1主面形成的氧化膜9会通过之后的工序除去。

115.接着,如图17所示,在内壁形成有氧化膜9的沟槽8内,通过cvd(chemical vapor deposition)等沉积掺杂了n型或p型杂质的多晶硅,形成栅极沟槽电极11a、哑沟槽电极12a及二极管沟槽电极21a。

116.接着,如图18所示,在igbt区域10的有源沟槽栅极11的栅极沟槽电极11a之上形成了层间绝缘膜4后,除去在半导体基板的第1主面形成的氧化膜9。层间绝缘膜4例如可以是sio2。然后,通过掩模处理在沉积出的层间绝缘膜4形成接触孔。接触孔形成于n

+

型源极层13之上、p

+

型接触层14之上、p

+

型接触层24之上、哑沟槽电极12a之上及二极管沟槽电极21a之上。

117.接着,如图19所示,在半导体基板的第1主面及层间绝缘膜4之上形成阻挡金属5,进一步在阻挡金属5之上形成发射极电极6。阻挡金属5通过利用pvd(physical vapor deposition)或cvd对氮化钛进行成膜而形成。

118.例如可以通过溅射或蒸镀等pvd使铝硅合金(al-si类合金)沉积于阻挡金属5之上而形成发射极电极6。另外,也可以在形成的铝硅合金之上通过化学镀或电镀进一步形成镍合金(ni合金)而作为发射极电极6。如果通过镀敷形成发射极电极6,则能够容易地形成厚的金属膜作为发射极电极6,因此能够使发射极电极6的热容增加而使耐热性提高。此外,在通过pvd形成了由铝硅合金构成的发射极电极6后,通过镀敷处理进一步形成镍合金的情况下,用于形成镍合金的镀敷处理也可以在进行了半导体基板的第2主面侧的加工后实施。

119.接着,如图20所示,对半导体基板的第2主面侧进行研磨,将半导体基板薄化为设计好的规定的厚度。研磨后的半导体基板的厚度例如可以为80μm~200μm。

120.接着,如图21所示,从半导体基板的第2主面侧注入n型杂质而形成n型缓冲层3。而且,从半导体基板的第2主面侧注入p型杂质而形成p型集电极层16。n型缓冲层3可以形成于igbt区域10、二极管区域20及末端区域30,也可以仅形成于igbt区域10或二极管区域20。

121.n型缓冲层3例如可以通过注入磷(p)离子而形成。另外,可以通过注入质子(h

+

)而形成。而且,可以通过注入质子和磷这两者而形成。质子能够以比较低的加速能量从半导体基板的第2主面注入至深的位置。另外,通过改变加速能量能够比较容易地对质子的注入深度进行变更。因此,如果在通过质子形成n型缓冲层3时,变更加速能量而多次进行注入,则与通过磷形成相比能够形成在半导体基板的厚度方向上宽度更宽的n型缓冲层3。

122.另外,磷与质子相比,能够提高作为n型杂质的激活率,因此即使是通过利用磷形成n型缓冲层3而薄化后的半导体基板,也能够更可靠地对耗尽层击穿进行抑制。为了将半导体基板进一步薄化,优选注入质子和磷这两者而形成n型缓冲层3,此时,与磷相比质子从第2主面注入至更深的位置。

123.p型集电极层16例如可以通过注入硼(b)而形成。p型集电极层16也形成于末端区域30,末端区域30的p型集电极层16成为p型末端集电极层16a。在从半导体基板的第2主面侧进行了离子注入后,通过将激光照射至第2主面而进行激光退火,从而将注入的硼激活而形成p型集电极层16。此时,从半导体基板的第2主面注入至比较浅的位置的n型缓冲层3所用的磷也同时被激活。另一方面,由于质子在350℃~500℃这样的比较低的退火温度下被激活,因此除了在注入了质子后用于质子的激活的工序之外,需要留心不使半导体基板整体成为比350℃~500℃高的温度。激光退火由于能够仅使半导体基板的第2主面附近成为高温,因此在注入了质子后也能够用于n型杂质及p型杂质的激活。

124.接着,如图22所示,在二极管区域20形成n

+

型阴极层26。n

+

型阴极层26例如可以通过注入磷(p)而形成。如图22所示,以p型集电极层16和n

+

型阴极层26的边界位于从igbt区域10和二极管区域20的边界向二极管区域20侧离开距离u1的位置处的方式,从第2主面侧通过掩模处理选择性地注入磷。用于形成n

+

型阴极层26的n型杂质的注入量比用于形成p型集电极层16的p型杂质的注入量多。在图22中,示出从第2主面起的p型集电极层16和n

+

型阴极层26的深度相同,但n

+

型阴极层26的深度大于或等于p型集电极层16的深度。由于形成n

+

型阴极层26的区域需要将n型杂质注入至注入了p型杂质的区域而成为n型半导体,因此将在形成n

+

型阴极层26的整个区域注入的p型杂质的浓度设得比n型杂质的浓度高。

125.接着,通过在半导体基板的第2主面之上形成集电极电极7,能够得到图9所示的剖面结构。集电极电极7是遍及第2主面的igbt区域10、二极管区域20及末端区域30的整面而形成的。另外,集电极电极7可以遍及半导体基板即n型晶片的第2主面的整面而形成。集电极电极7可以通过溅射或蒸镀等pvd,沉积铝硅合金(al-si类合金)或钛(ti)等而形成,也可以通过使铝硅合金、钛、镍或金等多个金属层叠而形成。而且,也可以在利用pvd形成的金属膜之上通过化学镀或电镀,进一步形成金属膜而设为集电极电极7。

126.通过以上那样的工序对半导体装置100或半导体装置101进行制作。就半导体装置100或半导体装置101而言,由于在1片n型晶片矩阵状地制作多个,因此通过采用激光切割或刀片切割而切分为各个半导体装置100或半导体装置101,从而完成半导体装置100或半导体装置101。

127.《实施方式1》

128.《结构》

129.图23是表示实施方式1涉及的rc-igbt 1000的结构的局部剖视图,是与图1所示的半导体装置100或图2所示的半导体装置101的虚线g-g处的箭头方向剖视图相当的剖视图。此外,对与图9所示的半导体装置100或半导体装置101的剖视图即图9相同的结构标注相同的标号,省略重复的说明。

130.如图23所示,在igbt区域10的第2主面侧设置的p型集电极层16设置为从igbt区域10和二极管区域20的边界向二极管区域20侧伸出距离u1。这样,通过将p型集电极层16设置为伸出到二极管区域20,从而能够增大二极管区域20的n

+

型阴极层26与有源沟槽栅极11的距离,即使在续流二极管动作时对栅极沟槽电极11a施加了栅极驱动电压的情况下,也能够对电流从igbt区域10的与有源沟槽栅极11相邻地形成的沟道流动至n

+

型阴极层26进行抑制。

131.就图23所示的rc-igbt 1000而言,二极管区域20具有半导体基板的第1主面即n

+

型源极层13、p

+

型接触层14、从p

+

型接触层24及p型阳极层25的纸面上端到达n-型漂移层1的多个有源沟槽栅极11、多个哑沟槽栅极12、多个二极管沟槽栅极21、多个二极管半沟槽(semi-trench)栅极22及二极管哑有源沟槽栅极41。

132.此外,在本发明中,特征在于二极管区域20的结构,因此下面以二极管区域20的结构为中心进行说明。

133.如图23所示,二极管哑有源沟槽栅极41设置为被两个二极管半沟槽栅极22夹着,在二极管哑有源沟槽栅极41和二极管半沟槽栅极22之间设置有第3半导体层即p型阳极层41c。而且,两个二极管半沟槽栅极22及二极管哑有源沟槽栅极41之上被连续的层间绝缘膜4覆盖,对p型阳极层41c未赋予第1电位即发射极电位而是成为浮置状态。

134.二极管沟槽栅极21在将p

+

型接触层24、p型阳极层25及n型载流子积蓄层2贯穿而到达n-型漂移层1的沟槽内,隔着二极管沟槽绝缘膜21b而设置有二极管沟槽电极21a,二极管沟槽电极21a与发射极电极6电连接。

135.二极管半沟槽栅极22在将p型阳极层25及n型载流子积蓄层2贯穿而到达n-型漂移层1的沟槽内,隔着二极管半沟槽绝缘膜22b而设置有二极管半沟槽电极22a,二极管半沟槽电极22a与发射极电极6电连接。

136.在二极管半沟槽栅极22的两个侧面的一者侧设置由与发射极电极6电连接的p型阳极层25,在另一者侧设置有未与发射极电极6电连接而是成为浮置状态的p型阳极层41c。将这样在沟槽栅极的单侧具有成为浮置状态的p型阳极层的结构这一沟槽栅极称为“半(semi)沟槽栅极”。

137.二极管哑有源沟槽栅极41在将p型阳极层41c及n型载流子积蓄层2贯穿而到达n-型漂移层1的沟槽内,隔着二极管哑有源沟槽绝缘膜41b而设置有二极管哑有源沟槽电极41a,二极管哑有源沟槽电极41a与未图示的栅极电极电连接。

138.在二极管哑有源沟槽栅极41的侧面的两侧设置有未与发射极电极6电连接而是成为浮置状态的p型阳极层41c。将这样使沟槽电极与栅极电极电连接,在栅极的单侧具有成为浮置状态的p型阳极层的结构称为“哑有源沟槽栅极”。

139.如上所述,rc-igbt 1000在二极管区域20处,对二极管沟槽栅极21的二极管沟槽电极21a及二极管半沟槽栅极22的二极管半沟槽电极22a赋予发射极电位e,对二极管哑有源沟槽栅极41的二极管哑有源沟槽电极41a赋予栅极电位g。

140.这样,通过在二极管区域配置二极管哑有源沟槽栅极41,能够对位移电流进行抑制。即,在二极管区域,由于在二极管动作时从阳极注入空穴,没有从阴极注入空穴,因此不会由于从阴极注入的空穴而使p型阳极层41c的电位产生变动,能够对流过二极管哑有源沟槽栅极41的位移电流进行抑制。

141.另外,在igbt区域10的第2主面侧设置的p型集电极层16设置为从igbt区域10和二极管区域20的边界向二极管区域20侧伸出距离u1,但在与该p型集电极层16伸出的区域对应的第1主面侧没有配置二极管哑有源沟槽栅极41。由此,能够对流过二极管哑有源沟槽栅极41的位移电流进行抑制。

142.此外,由于在igbt区域没有设置哑有源沟槽栅极,因此在导通时从集电极层注入的空穴不会使浮置的p型基极层15的电位变动,因此能够对位移电流流过哑有源沟槽栅极进行抑制,对dv/dt的栅极电阻控制性降低进行抑制。

143.另外,通过两个二极管半沟槽栅极22夹着二极管哑有源沟槽栅极41,在二极管哑有源沟槽栅极41和二极管半沟槽栅极22之间设置p型阳极层41c,p型阳极层41c未与发射极电位连接而是成为浮置状态。

144.因此,通过二极管哑有源沟槽栅极41的二极管哑有源沟槽电极41a、二极管哑有源沟槽绝缘膜41b、浮置的p型阳极层41c及n-型漂移层1形成电容器。这意味着在二极管哑有源沟槽电极41a和集电极电极7即赋予第2电位的阴极电极之间形成电容器,这意味着增大igbt的栅极和集电极之间的栅极-集电极间电容(反馈电容)cgc。通过增大反馈电容(cgc),在漏极电压v相对于时间t的变动即dv/dt恒定的条件下能够降低导通损耗。

145.此外,在图23中,在二极管哑有源沟槽栅极41的两侧配置的p型阳极层41c为浮置电位,但在单元区域内p型阳极层41c也可以与发射极电极6连接。另外,在末端区域可以与p型末端阱层31(图11)连接,也可以不连接。在该情况下,p型末端阱层31也可以与发射极电极6电连接。即,p型阳极层41c可以在末端区域与发射极电极6和电极电连接,也可以不连接。通过使p型阳极层41c不与正上方的发射极电极6电连接,而在远离的位置处与发射极电极6电连接,从而经由高电阻与发射极电极6连接,模拟地成为浮置状态,因此能够得到增大反馈电容(cgc)的效果。

146.《效果》

147.如上所述,根据实施方式1涉及的rc-igbt 1000,能够对在二极管哑有源沟槽栅极41流过的位移电流进行抑制,另外,在二极管区域20设置二极管哑有源沟槽栅极41,在其旁边设置浮置状态的p型阳极层41c,由此能够增大igbt的栅极与集电极之间的反馈电容cgc,因此在dv/dt恒定的条件下能够降低导通损耗。

148.《变形例》

149.就图23所示的rc-igbt 1000而言,公开了被两个二极管半沟槽栅极22夹着的二极管哑有源沟槽栅极41仅有1个的结构,但并不限于此,也可以设置多个二极管哑有源沟槽栅极41。

150.例如,图24所示的rc-igbt 1001成为在两个二极管半沟槽栅极22之间设置有2个二极管哑有源沟槽栅极41的结构。

151.二极管哑有源沟槽栅极41设置为被两个二极管半沟槽栅极22夹着。这样,在二极管哑有源沟槽栅极41和二极管半沟槽栅极22以相邻的方式配置的情况下,在栅极电位的二极管哑有源沟槽栅极41和发射极电位的二极管半沟槽栅极22之间产生耦合电容即栅极-发射极间电容cge。如果产生了栅极-发射极间电容cge,则栅极电容比cgc/cge变小,不利于降低导通损耗。

152.因此,如图24所示的rc-igbt 1001那样,通过增加二极管哑有源沟槽栅极41的个数,从而能够进一步增大栅极电容比cgc/cge,进一步降低导通损耗。

153.《实施方式2》

154.《结构》

155.图25是表示实施方式2涉及的rc-igbt 2000的结构的局部剖视图,是与图1所示的半导体装置100或图2所示的半导体装置101的虚线g-g处的箭头方向剖视图相当的剖视图。此外,对与图9所示的半导体装置100或半导体装置101的剖视图即图9相同的结构标注相同的标号,省略重复的说明。

156.就图25所示的rc-igbt 2000而言,二极管区域20具有从半导体基板的第1主面即p型阳极层25的纸面上端到达n-型漂移层1的多个二极管沟槽栅极21及相邻地配置的两个二极管半哑有源沟槽栅极51。而且,在两个二极管半哑有源沟槽栅极51之间设置有p型阳极层41c。两个二极管半哑有源沟槽栅极51之上被连续的层间绝缘膜4覆盖,对p型阳极层41c未赋予发射极电位而是成为浮置状态。

157.二极管半哑有源沟槽栅极51在将p型阳极层41c及n型载流子积蓄层2贯穿而到达n-型漂移层1的沟槽内,隔着二极管半哑有源沟槽绝缘膜51b而设置有二极管半哑有源沟槽电极51a,二极管半哑有源沟槽电极51a与未图示的栅极电极电连接。

158.在二极管半哑有源沟槽栅极51的两个侧面的一者侧设置有与发射极电极6电连接的p型阳极层25,在另一者侧设置有成为浮置状态的p型阳极层41c。

159.如上所述,rc-igbt 2000在二极管区域20处,对二极管沟槽栅极21的二极管沟槽电极21a及二极管半沟槽栅极22的二极管半沟槽电极22a赋予发射极电位e,对二极管半哑有源沟槽栅极51的二极管半哑有源沟槽电极51a赋予栅极电位g。

160.这样,通过在二极管区域配置二极管半哑有源沟槽栅极51,能够对位移电流进行抑制。即,在二极管区域,由于在二极管动作时从阳极注入空穴,没有从阴极注入空穴,因此不会由于从阴极注入的空穴使p型阳极层41c的电位产生变动,能够对流过二极管半哑有源沟槽栅极51的位移电流进行抑制。

161.另外,在igbt区域10的第2主面侧设置的p型集电极层16设置为从igbt区域10和二极管区域20的边界向二极管区域20侧伸出距离u1,但在与该p型集电极层16伸出的区域对应的第1主面侧没有配置二极管半哑有源沟槽栅极51。由此,也能够对流过二极管半哑有源沟槽栅极51的位移电流进行抑制。

162.此外,由于在igbt区域没有设置哑有源沟槽栅极,因此在导通时从集电极层注入的空穴不会使浮置的p型基极层15的电位变动,因此能够对位移电流流过哑有源沟槽栅极进行抑制,对dv/dt的栅极电阻控制性降低进行抑制。

163.另外,在两个二极管半哑有源沟槽栅极51之间设置有p型阳极层41c,p型阳极层41c没有与发射极电位连接而是成为浮置状态。

164.因此,通过二极管半哑有源沟槽栅极51的二极管半哑有源沟槽电极51a、二极管半哑有源沟槽绝缘膜51b、浮置的p型阳极层41c及n-型漂移层1形成电容器。这意味着在二极管半哑有源沟槽电极51a和集电极电极7即赋予第2电位的阴极电极之间形成电容器,这意味着增大igbt的栅极和集电极之间的栅极-集电极间电容(反馈电容)cgc。通过增大反馈电容(cgc),在漏极电压v相对于时间t的变动即dv/dt恒定的条件下能够降低导通损耗。

165.《效果》

166.如上所述,根据实施方式2涉及的rc-igbt 2000,能够对在二极管半哑有源沟槽栅极51流过的位移电流进行抑制,另外,在二极管区域20设置二极管半哑有源沟槽栅极51,在其旁边设置浮置状态的p型阳极层41c,由此能够增大igbt的栅极与集电极之间的反馈电容cgc,因此在dv/dt恒定的条件下能够降低导通损耗。

167.《变形例1》

168.就图25所示的rc-igbt 2000而言,示出了在二极管半哑有源沟槽栅极51之间设置有浮置状态的p型阳极层41c的结构,但也可以如图26所示的rc-igbt 2001那样,设为在二

极管半哑有源沟槽栅极51旁边设置了二极管哑有源沟槽栅极41的结构。

169.如图26所示,二极管哑有源沟槽栅极41在将p型阳极层41c及n型载流子积蓄层2贯穿而到达n-型漂移层1的沟槽内,隔着二极管哑有源沟槽绝缘膜41b而设置有二极管哑有源沟槽电极41a,二极管哑有源沟槽电极41a与未图示的栅极电极电连接。而且,两个二极管半哑有源沟槽栅极51及二极管哑有源沟槽栅极41之上被连续的层间绝缘膜4覆盖,对p型阳极层41c未赋予发射极电位而是成为浮置状态。

170.这样,通过在二极管区域以与二极管半哑有源沟槽栅极51相邻的方式配置二极管哑有源沟槽栅极41,能够对位移电流进行抑制。即,在二极管区域,由于在二极管动作时从阳极注入空穴,没有从阴极注入空穴,因此不会由于从阴极注入的空穴使p型阳极层41c的电位产生变动,能够对流过二极管哑有源沟槽栅极41的位移电流进行抑制。

171.另外,通过配置二极管哑有源沟槽栅极41,从而由二极管哑有源沟槽栅极41的二极管哑有源沟槽电极41a、二极管哑有源沟槽绝缘膜41b、浮置的p型阳极层41c及n-型漂移层1形成电容器。由此,能够进一步增大igbt的栅极和集电极之间的栅极-集电极间电容(反馈电容)cgc。通过进一步增大反馈电容(cgc),从而在漏极电压v相对于时间t的变动即dv/dt恒定的条件下能够进一步降低导通损耗。

172.另外,由于被赋予栅极电位的二极管哑有源沟槽栅极41和二极管半哑有源沟槽栅极51相邻地配置,因此在两者之间没有产生耦合电容即栅极-发射极间电容cge,能够增大栅极电容比cgc/cge,因此能够降低导通损耗。

173.就图26所示的rc-igbt 2001而言,公开了被两个二极管半哑有源沟槽栅极51夹着的二极管哑有源沟槽栅极41仅有1个的结构,但并不限于此,也可以设置多个二极管哑有源沟槽栅极41。

174.通过增加二极管哑有源沟槽栅极41的个数,从而能够进一步增大栅极电容比cgc/cge,进一步降低导通损耗。

175.《变形例2》

176.就图26所示的rc-igbt 2001而言,示出设置有从半导体基板的第1主面即p型阳极层25的纸面上端到达n-型漂移层1的多个二极管沟槽栅极21的结构,但也可以如图27所示的rc-igbt 2002那样,设为取代多个二极管沟槽栅极21而具有从半导体基板的第1主面到达n-型漂移层1的多个二极管有源沟槽栅极61的结构。

177.二极管有源沟槽栅极61在将p

+

型接触层24、p型阳极层25及n型载流子积蓄层2贯穿而到达n-型漂移层1的沟槽内,隔着二极管有源沟槽绝缘膜61b而设置有二极管有源沟槽电极61a,二极管有源沟槽电极61a与未图示的栅极电极电连接。

178.因此,通过二极管有源沟槽栅极61的二极管有源沟槽电极61a、二极管有源沟槽绝缘膜61b、与发射极电极6电连接的p型阳极层25形成电容器,产生栅极-发射极间电容cge。但是,同时,通过由二极管有源沟槽电极61a、二极管有源沟槽绝缘膜61b及n-型漂移层1形成的电容器,也产生栅极-集电极间电容(反馈电容)cgc。因此,能够与由配置二极管哑有源沟槽栅极41及二极管半哑有源沟槽栅极51形成的栅极-集电极间电容(反馈电容)cgc相配合地,进一步增大反馈电容(cgc),在漏极电压v相对于时间t的变动即dv/dt恒定的条件下能够进一步降低导通损耗。

179.《实施方式3》

180.《结构》

181.图28是表示实施方式3涉及的rc-igbt 3000的结构的局部剖视图,是与图1所示的半导体装置100或图2所示的半导体装置101的虚线g-g处的箭头方向剖视图相当的剖视图。此外,对与图9所示的半导体装置100或半导体装置101的剖视图即图9相同的结构标注相同的标号,省略重复的说明。

182.就图28所示的rc-igbt 3000而言,与图26所示的rc-igbt2001相同地,成为在二极管半哑有源沟槽栅极51旁边设置有二极管哑有源沟槽栅极41的结构,但二极管哑有源沟槽栅极41和二极管半哑有源沟槽栅极51的间隔设定得比相邻的二极管沟槽栅极21的间隔、或相邻的有源沟槽栅极11的间隔、或相邻的有源沟槽栅极11与哑沟槽栅极12的间隔短。

183.此外,在图28中,将二极管哑有源沟槽栅极41的配置个数设为1个,但并不限于此,能够配置多个二极管哑有源沟槽栅极41。

184.在该情况下,二极管哑有源沟槽栅极41与二极管半哑有源沟槽栅极51的间隔、及相邻的二极管哑有源沟槽栅极41的间隔能够设为其它相邻的沟槽栅极的间隔的1/2~1/4。

185.《效果》

186.通过将二极管哑有源沟槽栅极41与二极管半哑有源沟槽栅极51的间隔设得窄,从而能够高密度地配置二极管哑有源沟槽栅极41及二极管半哑有源沟槽栅极51,因此通过增加二极管哑有源沟槽栅极41的配置个数,从而能够增大igbt的栅极与集电极之间的栅极-集电极间电容(反馈电容)cgc,在漏极电压v相对于时间t的变动即dv/dt恒定的条件下能够降低导通损耗。

187.《变形例》

188.就以上说明过的实施方式3的rc-igbt 3000而言,公开了通过使二极管哑有源沟槽栅极41与二极管半哑有源沟槽栅极51的间隔比其它相邻的沟槽栅极的间隔窄,增加二极管哑有源沟槽栅极41的配置个数,从而增加反馈电容cgc的结构,但如图29所示的rc-igbt3001那样,通过将二极管哑有源沟槽栅极41的配置图案设为格子状,也能够增加反馈电容cgc。

189.图29是表示rc-igbt 3001的结构的局部俯视图,是针对二极管区域20的一部分,从上方观察二极管哑有源沟槽栅极41及二极管半哑有源沟槽栅极51的情况下的图。此外,为了方便,在图29中省略了发射极电极6等结构的图示。

190.如图29所示,二极管哑有源沟槽栅极41成为在沟槽的延伸方向上的多个部分处,向与沟槽的延伸方向垂直的方向进行分支,与相邻的二极管半哑有源沟槽栅极51连接的结构。其结果,由二极管哑有源沟槽栅极41和二极管半哑有源沟槽栅极51形成格子状的沟槽栅极,p型阳极层41c成为被格子状的沟槽栅极包围的在俯视观察时呈矩形的区域。

191.因此,由配置二极管哑有源沟槽栅极41及二极管半哑有源沟槽栅极51形成的栅极-集电极间电容(反馈电容)cgc增大,在漏极电压v相对于时间t的变动即dv/dt恒定的条件下能够降低导通损耗。

192.此外,在俯视观察时呈矩形的p型阳极层41c的形成个数只要是在条带状的二极管哑有源沟槽栅极41的长度的范围内落在能够形成二极管哑有源沟槽绝缘膜41b及二极管哑有源沟槽电极41a的大小的范围,就没有特别限制。

193.《实施方式4》

194.《结构》

195.图30是表示实施方式4涉及的rc-igbt 4000的结构的局部剖视图,是与图1所示的半导体装置100或图2所示的半导体装置101的虚线g-g处的箭头方向剖视图相当的剖视图。此外,对与图9所示的半导体装置100或半导体装置101的剖视图即图9相同的结构标注相同的标号,省略重复的说明。

196.就图30所示的rc-igbt 4000而言,与图23所示的rc-igbt1001相同地,二极管哑有源沟槽栅极41设置为被两个二极管半沟槽栅极22夹着,但在二极管哑有源沟槽栅极41和二极管半沟槽栅极22之间的台面区域没有设置p型阳极层41c,成为n-型漂移层1,也没有设置n型载流子积蓄层2。

197.《效果》

198.当在二极管哑有源沟槽栅极41和二极管半沟槽栅极22之间的台面区域设置有p型阳极层41c的情况下,在二极管的恢复动作时由反向恢复电流引起的少量的空穴使浮置的p型阳极层41c的电位产生变动,有时产生位移电流。但是,通过在该处不形成p型半导体层,能够抑制位移电流对二极管哑有源沟槽栅极41的影响。

199.《实施方式5》

200.《结构》

201.图31是作为实施方式5涉及的半导体装置,示出岛型的半导体装置102的俯视图,在1个半导体装置内具有igbt区域10和二极管区域20。在图31中,用箭头ar表示沟槽栅极的延伸方向。如图31所示,沟槽栅极沿控制焊盘410的排列方向延伸。此外,对与图2所示的半导体装置101相同的结构标注相同的标号,省略重复的说明。

202.图32是图31中的e-e线处的箭头方向剖视图。图32所示的igbt区域10的剖面结构与图4所示的igbt区域10的剖面结构相同,对相同结构标注相同的标号,省略重复的说明。

203.图33是图31中的g-g线处的箭头方向剖视图。图33所示的二极管区域20的剖面结构与图26所示的rc-igbt 2001的剖面结构基本上相同,成为在二极管半哑有源沟槽栅极51旁边设置有二极管哑有源沟槽栅极41的结构。此外,对与rc-igbt 2001相同的结构标注相同的标号,省略重复的说明。

204.如图31所示,igbt区域10及二极管区域20在沟槽栅极的延伸方向上交替地配置,沟槽栅极成为在俯视观察时将igbt区域10及二极管区域20贯穿的结构。

205.在该结构中,在igbt区域10,如图32所示,例如,在具有与栅极焊盘410c(图31)电连接的栅极沟槽电极11a的有源沟槽栅极11的两个侧面中的两者或一者的外侧设置有n

+

型源极层13,n

+

型源极层13与发射极电极6电连接。

206.另一方面,在二极管区域20,如图33所示,在两个二极管半哑有源沟槽栅极51及设置于它们之间的二极管哑有源沟槽栅极41处,各个二极管半哑有源沟槽电极51a及二极管哑有源沟槽电极41a与栅极焊盘410c(图31)电连接。此外,在二极管哑有源沟槽栅极41和二极管半哑有源沟槽栅极51之间设置的p型阳极层41c未与发射极电极6电连接,成为浮置状态。

207.《效果》

208.如上所述,通过使igbt区域10中的有源沟槽栅极11、二极管区域20中的二极管哑有源沟槽栅极41及二极管半哑有源沟槽栅极51由连续的沟槽栅极构成,能够增加反馈电容

cgc。其原因在于,加上了由igbt区域10中的栅极沟槽电极11a、栅极沟槽绝缘膜11b及n-型漂移层1形成的电容器产生的反馈电容cgc。

209.《变形例》

210.图34是放大表示图31所示的半导体装置102中的二极管区域20的由虚线包围的区域83的局部俯视图。如图34所示,在二极管区域20,二极管沟槽栅极21沿半导体装置102的第1主面从单元区域即二极管区域20的一端侧向相对的另一端侧延伸。在相邻的2个二极管沟槽栅极21之间设置有p

+

型接触层24及p型阳极层25。另外,以夹在两个二极管沟槽栅极21之间的方式设置有二极管哑有源沟槽栅极41。

211.而且,在二极管哑有源沟槽栅极41的延伸方向上,其一部分形成为二极管有源沟槽栅极61,其上部被层间绝缘膜4覆盖。但是,以夹着二极管有源沟槽栅极61的方式设置的p

+

型接触层24及p型阳极层25的一部分与发射极电极电连接。

212.另一方面,以夹着二极管哑有源沟槽栅极41的方式设置的p型阳极层41c的上部被层间绝缘膜4覆盖,未与发射极电极电连接而是成为浮置状态。

213.图35是图34中的c-c线处的箭头方向剖视图。如图35所示,二极管有源沟槽栅极61的上部被层间绝缘膜4覆盖,但二极管有源沟槽栅极61的两个侧面的外侧的p

+

型接触层24与发射极电极6电连接。

214.图36是图34中的d-d线处的箭头方向剖视图。如图36所示,二极管哑有源沟槽栅极41、将其夹住的两个二极管沟槽栅极21之上被连续的层间绝缘膜4覆盖,对p型阳极层41c未赋予发射极电位而是成为浮置状态。

215.这样,在二极管区域20,成为二极管哑有源沟槽栅极41的区域、成为二极管有源沟槽栅极61的区域在沟槽栅极的延伸方向上交替地配置,这些沟槽栅极的沟槽电极与栅极焊盘410c电连接。另外,这些沟槽栅极的沟槽电极在igbt区域10成为有源沟槽栅极11的栅极沟槽电极11a,有源沟槽栅极11、二极管哑有源沟槽栅极41及二极管有源沟槽栅极61由连续的沟槽栅极构成。此外,也可以取代二极管哑有源沟槽栅极41而设置二极管半哑有源沟槽栅极51。

216.《效果》

217.如上所述,通过使igbt区域10中的有源沟槽栅极11、二极管区域20中的二极管哑有源沟槽栅极41及二极管有源沟槽栅极61由连续的沟槽栅极构成,能够增加反馈电容cgc。其原因在于,加上了由igbt区域10中的栅极沟槽电极11a、栅极沟槽绝缘膜11b及n-型漂移层1形成的电容器产生的反馈电容cgc。

218.《能够应用的半导体材料》

219.在以上说明过的实施方式1~5中没有提及半导体基板的构成材料,但作为半导体基板的构成材料,既能够由硅(si)构成,也能够由碳化硅(sic)构成。

220.由sic构成的开关元件的通断损耗小,能够进行高速通断动作。

221.另外,由sic构成的开关元件的电力损耗小,耐热性也高。因此,在构成具有冷却部的功率模块的情况下,能够将散热器的散热鳍片小型化,因此能够实现半导体模块的进一步小型化。

222.另外,由sic构成的开关元件适于高频通断动作。因此,在应用于高频化要求高的转换器电路的情况下,通过通断频率的高频化,也能够将与转换器电路连接的电抗器或电

容器等小型化。

223.作为sic之外的宽带隙半导体,也能够由氮化镓类材料、氧化镓类材料或金刚石等构成。

224.此外,本发明可以在其发明的范围内将各实施方式自由地组合,对各实施方式适当进行变形、省略。

225.标号的说明

226.1n-型漂移层,6发射极电极,7集电极电极,10igbt区域,11有源沟槽栅极,16p型集电极层,20二极管区域,25、41c p型阳极层,26n

+

型阴极层,41二极管哑有源沟槽栅极,51二极管半哑有源沟槽栅极,61二极管有源沟槽栅极。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1