用于GPU芯片和片上系统设备封装的反向嵌入式电源结构的制作方法

本申请总地涉及具有用于集成电路(ic)封装(诸如片上系统封装(soc))的电源结构的晶粒(die),更具体地,涉及具有用于图形处理单元(gpu)和soc封装的嵌入式电源结构的晶粒。

背景技术:

1、gpu和soc技术的两个持续趋势是使用更小的片上晶体管和在芯片上使用越来越多的晶体管,导致晶体管占据的芯片面积或密度增加。随着晶体管尺寸的减小和晶体管数量的增加,芯片晶粒互连层中互连线的宽度和厚度也相应减小,以互连更小尺寸和更多数量的晶体管。通常,为了实现每芯片更多数量的互连,使用更多的芯片互连层。通常,晶体管占据的芯片面积的增加会导致互连线的整体长度或平均长度增加。互连线的宽度和厚度的减小和长度的增加也会导致互连线的阻抗显著增加,这又会由于随着总图形功率(tgp)需求的增加提供足够的功率,以及处理增加的散热需求和防止信号完整性损失,而带来新的问题。

2、存在增加对芯片晶体管的功率分配以帮助避免提高芯片性能的瓶颈的持续需求。

技术实现思路

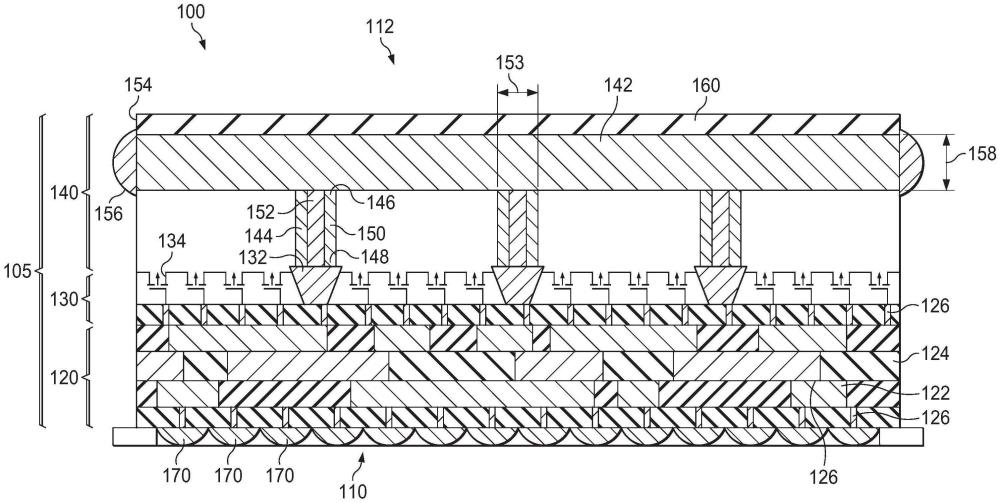

1、一个方面提供了一种包括晶粒体的晶粒。晶粒体具有第一体表面、与第一体表面位于晶粒体的相对侧上的第二体表面。晶粒体包括互连区、晶体管区和电源区。互连区位于第一体表面附近,并且互连区包括具有金属线和通孔的互连介电层。晶体管区位于互连区上方,并且金属线和通孔与晶体管区的一个或更多个电源轨进行电连接,并且电源轨电连接到晶体管区的一个或更多个晶体管。电源区位于晶体管区上方,电源区包括第二体表面上的导电薄膜和嵌入电源区中的硅通孔(tsv),其中对于每一tsv,tsv的外端接触导电薄膜,tsv的嵌入端接触晶体管区的电源轨之一。

2、另一方面是一种制造ic封装的方法。该方法包括:提供晶粒体,该晶粒体具有第一体表面110、与第一体表面位于晶粒体的相对侧上的第二体表面112,该晶粒体包括互连区、晶体管区和电源区。该方法还包括:形成穿过电源区的一个或更多个tsv,包括形成穿过电源区的孔,所述孔在晶体管区的电源轨之一上停止,然后用金属插塞填充所述孔,使得tsv的嵌入端接触晶体管区的电源轨之一。该方法还包括:在晶粒体的第二表面上形成导电薄膜,使得导电薄膜接触至少一个tsv的外端。所述方法还包括:在电源区的侧边缘上形成焊料凸块并与导电薄膜接触。

3、另一方面是一种计算机,其具有一个或更多个电路,所述一个或更多个电路包括ic封装,其包括本文公开的晶粒的任何实施例。

技术特征:

1.一种晶粒,包括:

2.如权利要求1所述的晶粒,其中所述tsv的孔包含金属插塞。

3.如权利要求1所述的晶粒,其中所述孔的直径是0.001至1000微米范围内的值。

4.如权利要求1所述的晶粒,其中所述导电薄膜横穿所述第二体表面到所述晶粒体的侧边缘,并且所述晶粒体的所述侧边缘上的一个或更多个焊料凸块接触所述导电薄膜。

5.如权利要求1所述的晶粒,其中所述导电薄膜的厚度为1至1000微米范围内的值。

6.如权利要求1所述的晶粒,还包括晶粒衬底,其中所述晶粒体位于所述晶粒衬底的第一衬底表面上,一条或更多条衬底导线位于所述第一衬底表面上,并且引线键合将所述衬底导线电连接到所述导电薄膜。

7.如权利要求6所述的晶粒,其中所述引线键合的一端接触位于所述晶粒体的侧边缘上的第一焊料凸块,所述第一焊料凸块接触所述导电薄膜,并且所述引线键合的相对端接触所述第一衬底表面上的晶粒衬底焊料凸块,所述晶粒衬底焊料凸块接触所述衬底导线之一。

8.如权利要求6所述的晶粒,其中所述晶粒和所述晶粒衬底是ic封装的一部分,其中所述晶粒衬底安装到封装衬底,所述封装衬底包括封装导线并且所述封装导线电连接以形成到所述晶粒体的所述晶体管的第一电流通路,所述第一通路包括:所述衬底导线、所述引线键合、所述晶粒衬底焊料凸块、所述导电薄膜和所述晶粒体的所述电源区的所述tsv。

9.如权利要求8所述的晶粒,其中所述封装导线电连接以形成到所述晶粒体的所述晶体管的第二电流通路,所述第二通路包括:晶粒衬底焊球、晶粒衬底通孔和所述晶粒衬底的晶粒衬底安装焊盘,以及所述晶粒体的所述电源区互连区的所述金属线和通孔。

10.如权利要求8所述的晶粒,其中所述第一电流通路和所述第二电流通路是通过所述晶粒衬底到所述晶粒体的所述晶体管区的独立导电通路。

11.一种制造ic封装的方法,包括:

12.如权利要求11所述的方法,其中形成所述一个或更多个tsv包括:通过激光钻孔或深度反应离子蚀刻工艺形成所述孔;以及通过电镀或物理气相沉积填充所述孔以形成金属插塞。

13.如权利要求11所述的方法,其中所蚀刻的孔的直径为0.001至1000微米范围内的值。

14.如权利要求11所述的方法,其中形成所述导电薄膜包括:物理或化学气相沉积或电镀铜或钨以形成所述金属插塞。

15.如权利要求11所述的方法,其中所述导电薄膜的厚度为1至1000微米范围内的值。

16.如权利要求11所述的方法,还包括:在所述导电薄膜上沉积密封层。

17.如权利要求16所述的方法,其中沉积所述密封层包括:在所述导电薄膜上化学气相沉积氧化硅。

18.如权利要求11所述的方法,还包括:将所述晶粒体安装到晶粒衬底,其包括将所述晶粒体的所述第一表面上的焊球连接到位于所述晶粒衬底的第一衬底表面上的安装焊盘。

19.如权利要求18所述的方法,还包括:在所述电源区的侧边缘上的所述焊料凸块和所述第一衬底表面上的晶粒衬底焊料凸块之间形成引线键合,所述晶粒衬底焊料凸块接触所述第一衬底表面上的衬底导线。

20.一种计算机,其具有一个或更多个电路,所述一个或更多个电路包括如权利要求11所述的ic封装。

技术总结

公开了用于GPU芯片和片上系统设备封装的反向嵌入式电源结构,具体公开了一种晶粒,包括晶粒体,该晶粒体具有第一体表面、与第一体表面处于晶粒体的相对侧上的第二体表面;与第一体表面相邻的互连区,包括具有金属线和通孔的互连介电层;互连区上方的晶体管区,金属线和通孔与晶体管区的一个或更多个电源轨进行电连接并电连接到晶体管区的晶体管;晶体管区上方的电源区,包括第二体表面上的导电薄膜和电源区中的TSV,TSV的外端与薄膜接触并且TSV的嵌入端与电源轨之一接触。还公开了一种制造IC封装的方法和具有该IC封装的计算机。

技术研发人员:肖杨杨,蒋知,李源,周杰,焦莹

受保护的技术使用者:辉达公司

技术研发日:

技术公布日:2024/3/24

- 还没有人留言评论。精彩留言会获得点赞!