一种含V型坑双波长的LED外延结构及其制备方法与流程

一种含v型坑双波长的led外延结构及其制备方法

技术领域

1.本发明涉及半导体光电子领域,更具体地说,涉及一种含v型坑双波长的led外延结构及其制备方法。

背景技术:

2.近年来,led(light emitting diode,发光二极管)器件凭借其体积小、高效节能及使用寿命长等优点,被广泛应用于照明、显示、医疗和可见光通信等领域。随着科技的进步以及人们生活水平的提高,人们对于照明的要求已经不再是高亮度、高光效的照明模式转而追求更加节能、环保、健康、智能的照明模式。由于全光谱无荧光粉照明能够改善led照明的光谱质量,可以满足人们对照明的要求,因此全光谱无荧光粉照明成为了led照明技术的发展趋势之一。

3.然而多芯片多基色无荧光粉led存在由于混光困难导致出光不均匀,以及驱动电路较为复杂导致生产成本高等问题,因此需要一种可行的方案来解决多芯片多基色在混合发光时存在混光不均的问题。

技术实现要素:

4.有鉴于此,为解决上述问题,本发明提供一种含v型坑双波长的led外延结构及其制备方法,技术方案如下:

5.一种含v型坑双波长的led外延结构,所述led外延结构包括:

6.衬底;

7.在第一方向上,依次位于所述衬底的一侧n型氮化镓层、低温氮化镓层、第一多量子阱层和第二多量子阱层,所述第一方向垂直于所述衬底且由所述衬底指向所述n型氮化镓层;

8.所述led外延结构还包括:第一v型坑和第二v型坑;

9.在所述第一方向上,所述第一v型坑贯穿所述第一多量子阱层和所述第二多量子阱层,以及部分延伸至所述低温氮化镓层;所述第二v型坑贯穿所述第二多量子阱层;

10.所述第一多量子阱层包括在所述第一方向上依次堆叠设置的多组第一堆叠膜层;

11.所述第一堆叠膜层包括在所述第一方向上依次叠层设置的in

x

ga

(1-x)

n量子阱层、alyga

(1-y)

n量子垒层和第一gan量子垒层;

12.所述第二多量子阱层包括在所述第一方向上依次堆叠设置的多组第二堆叠膜层;

13.所述第二堆叠膜层包括在所述第一方向上依次叠层设置的inzga

(1-z)

n量子阱层和第二gan量子垒层;

14.所述in

x

ga

(1-x)

n量子阱层中x的取值大于所述inzga

(1-z)

n量子阱层中z的取值。

15.优选的,在上述含v型坑双波长的led外延结构中,所述第一v型坑为倒六角锥形v型坑,所述第二v型坑为倒六角锥形v型坑。

16.优选的,在上述含v型坑双波长的led外延结构中,所述led外延结构还包括:

17.依次位于所述衬底面向所述n型氮化镓层一侧的缓冲层、三维形核层以及二维合并层;

18.位于所述低温氮化镓层和所述第一多量子阱层之间的应力释放层;

19.位于所述第二多量子阱层背离所述第一多量子阱层一侧的p型电子阻挡层和p型氮化镓层。

20.优选的,在上述含v型坑双波长的led外延结构中,所述p型电子阻挡层填充所述第一v型坑和所述第二v型坑。

21.优选的,在上述含v型坑双波长的led外延结构中,所述第一v型坑的开口尺寸的取值范围为98nm-280nm,所述第一v型坑在所述第一方向上的深度的取值范围为90nm-200nm,所述第一v型坑的密度的取值范围为1.5e8/cm

2-6e8/cm2;

22.所述第二v型坑的开口尺寸的取值范围为98nm-280nm,所述第二v型坑在所述第一方向上的深度的取值范围为90nm-200nm,所述第二v型坑的密度的取值范围为1.5e8/cm

2-6e8/cm2。

23.优选的,在上述含v型坑双波长的led外延结构中,所述in

x

ga

(1-x)

n量子阱层中x的取值范围为0≤x≤0.5,所述alyga

(1-y)

n量子垒层中y的取值范围为0≤y≤0.5,所述inzga

(1-z)

n量子阱层中z的取值范围为0≤z≤0.5。

24.优选的,在上述含v型坑双波长的led外延结构中,所述低温氮化镓层的厚度范围为50nm-400nm,所述in

x

ga

(1-x)

n量子阱层的厚度范围为2nm-4nm,所述alyga

(1-y)

n量子垒层的厚度范围为2nm-4nm,所述inzga

(1-z)

n量子阱层的厚度范围为2nm-4nm,所述第一gan量子垒层的厚度范围为8nm-15nm,所述第二gan量子垒层的厚度范围为8nm-15nm。

25.优选的,在上述含v型坑双波长的led外延结构中,所述第一多量子阱层的周期数的取值范围为3-9,所述第二多量子阱层的周期数的取值范围为3-9。

26.一种含v型坑双波长的led外延结构的制备方法,所述制备方法包括:

27.提供一衬底;

28.在所述衬底的一侧依次形成n型氮化镓层、低温氮化镓层、第一多量子阱层和第二多量子阱层;

29.其中led外延结构包括第一v型坑和第二v型坑,在第一方向上,所述第一v型坑贯穿所述第一多量子阱层和所述第二多量子阱层,以及部分延伸至所述低温氮化镓层,所述第二v型坑贯穿所述第二多量子阱层,所述第一方向垂直于所述衬底且由所述衬底指向所述n型氮化镓层;

30.所述第一多量子阱层包括在所述第一方向上依次堆叠设置的多组第一堆叠膜层,所述第一堆叠膜层包括在所述第一方向上依次叠层设置的in

x

ga

(1-x)

n量子阱层、alyga

(1-y)

n量子垒层和第一gan量子垒层;

31.所述第二多量子阱层包括在所述第一方向上依次堆叠设置的多组第二堆叠膜层,所述第二堆叠膜层包括在所述第一方向上依次叠层设置的inzga

(1-z)

n量子阱层和第二gan量子垒层,所述in

x

ga

(1-x)

n量子阱层中x的取值大于所述inzga

(1-z)

n量子阱层中z的取值。

32.优选的,在上述含v型坑双波长的led外延结构的制备方法中,在形成所述n型氮化镓层之前,所述制备方法还包括:

33.在所述衬底面向所述n型氮化镓层的一侧依次形成缓冲层、三维形核层以及二维

合并层。

34.优选的,在上述含v型坑双波长的led外延结构的制备方法中,在形成所述低温氮化镓层之后,所述制备方法还包括:

35.在所述低温氮化镓层面向所述第一多量子阱层的一侧形成应力释放层。

36.优选的,在上述含v型坑双波长的led外延结构的制备方法中,在形成所述第二多量子阱层之后,所述制备方法还包括:

37.在所述第二多量子阱层背离所述第一多量子阱层的一侧依次形成p型电子阻挡层和p型氮化镓层。

38.优选的,在上述含v型坑双波长的led外延结构的制备方法中,所述形成所述低温氮化镓层包括:

39.在温度范围为600℃-800℃的条件下形成所述低温氮化镓层。

40.相较于现有技术,本发明实现的有益效果为:

41.本发明提供的一种含v型坑双波长的led外延结构及其制备方法,所述led外延结构包括衬底、n型氮化镓层、低温氮化镓层、第一多量子阱层和第二多量子阱层;所述n型氮化镓层具有线位错,通过形成所述低温氮化镓层使得线位错不断增多,从而至少在所述第一多量子阱层和所述第二多量子阱层形成两种不同深度的v型坑,使得有源发光区由传统的平面结构变为立体结构,通过第一v型坑可以将载流子注入到所述第一多量子阱层,通过第二v型坑可以将载流子注入到所述第二多量子阱层,从而可以实现在单芯片上发出两种不同波长的光;另外,第一多量子阱层包括in

x

ga

(1-x)

n量子阱层和alyga

(1-y)

n量子垒层,所述第二多量子阱层包括inzga

(1-z)

n量子阱层,所述alyga

(1-y)

n量子垒层可以提供高势垒阻挡载流子在第一多量子阱层中复合发光,所述in

x

ga

(1-x)

n量子阱层中x的取值大于所述inzga

(1-z)

n量子阱层中z的取值,高in组分的量子阱层对空穴限制作用强,不同in组分可以控制载流子在不同深度的v型坑中的输运路径,从而实现在载流子分布的均匀性,解决了混光不均的问题。

附图说明

42.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据提供的附图获得其他的附图。

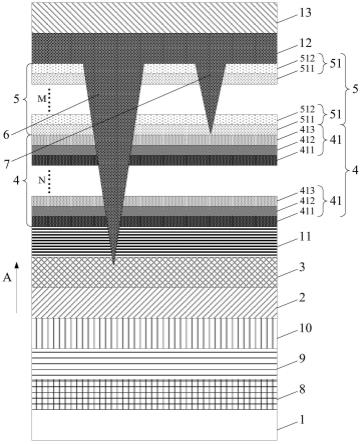

43.图1为本发明实施例提供的一种含v型坑双波长的led外延结构的结构示意图;

44.图2为本发明实施例提供的另一种含v型坑双波长的led外延结构的结构示意图;

45.图3为本发明实施例提供的一种含v型坑双波长的led外延结构的制备方法的流程示意图;

46.图4为本发明实施例提供的另一种含v型坑双波长的led外延结构的制备方法的流程示意图。

具体实施方式

47.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完

整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

48.为使本发明的上述目的、特征和优点能够更加明显易懂,下面结合附图和具体实施方式对本发明作进一步详细的说明。

49.本发明实施例中提供了一种含v型坑双波长的led外延结构,参考图1,图1为本发明实施例提供的一种含v型坑双波长的led外延结构的结构示意图,结合图1,所述led外延结构包括:

50.衬底1;在第一方向a上,依次位于所述衬底1的一侧n型氮化镓层2、低温氮化镓层3、第一多量子阱层4和第二多量子阱层5,所述第一方向a垂直于所述衬底1且由所述衬底1指向所述n型氮化镓层2。

51.具体的,在本发明实施例中,所述衬底1包括但不限定于使用si衬底、pss蓝宝石衬底或sic衬底等;所述低温氮化镓层3位于所述n型氮化镓层2背离所述衬底1的一侧,所述第一多量子阱层4位于所述低温氮化镓层3背离所述n型氮化镓层2的一侧,所述第二多量子阱层5位于所述第一多量子阱层4背离所述低温氮化镓层3的一侧。

52.所述led外延结构还包括:第一v型坑6和第二v型坑7;在所述第一方向a上,所述第一v型坑6贯穿所述第一多量子阱层4和所述第二多量子阱层5,以及部分延伸至所述低温氮化镓层3;所述第二v型坑7贯穿所述第二多量子阱层5。

53.具体的,在本发明实施例中,所述第一v型坑6贯穿所述第一多量子阱层4和所述第二多量子阱层5,并且所述第一v型坑6在贯穿所述第一多量子阱层4和所述第二多量子阱层5的基础上延伸至所述低温氮化镓层3,但所述第一v型坑6并没有贯穿所述低温氮化镓层3。

54.所述第一多量子阱层4包括在所述第一方向a上依次堆叠设置的多组第一堆叠膜层41;所述第一堆叠膜层41包括在所述第一方向a上依次叠层设置的in

x

ga

(1-x)

n量子阱层411、alyga

(1-y)

n量子垒层412和第一gan量子垒层413。

55.具体的,在本发明实施例中,所述第一多量子阱层4包括在所述第一方向a上依次堆叠设置的n组第一堆叠膜层41;其中,在所述第一堆叠膜层41中,所述alyga

(1-y)

n量子垒层412位于所述in

x

ga

(1-x)

n量子阱层411背离所述衬底1的一侧,所述第一gan量子垒层413位于所述alyga

(1-y)

n量子垒层412背离所述in

x

ga

(1-x)

n量子阱层411的一侧。

56.所述第二多量子阱层5包括在所述第一方向a上依次堆叠设置的多组第二堆叠膜层51;所述第二堆叠膜层51包括在所述第一方向a上依次叠层设置的inzga

(1-z)

n量子阱层511和第二gan量子垒层512;所述in

x

ga

(1-x)

n量子阱层411中x的取值大于所述inzga

(1-z)

n量子阱层511中z的取值。

57.具体的,在本发明实施例中,所述第二多量子阱层5包括在所述第一方向a上依次堆叠设置的m组第二堆叠膜层51;其中,在所述第二堆叠膜层51中,所述第二gan量子垒层512位于所述inzga

(1-z)

n量子阱层511背离所述衬底1的一侧。

58.通过上述描述可知,本发明提供了一种含v型坑双波长的led外延结构,所述led外延结构包括衬底1、n型氮化镓层2、低温氮化镓层3、第一多量子阱层4、第二多量子阱层5、第一v型坑6和第二v型坑7;所述第一v型坑6贯穿所述第一多量子阱层4和所述第二多量子阱层5,以及部分延伸至所述低温氮化镓层3,所述第二v型坑7贯穿所述第二多量子阱层5,通

过两种不同深度的v型坑使得有源发光区由传统的平面结构变为立体结构,通过第一v型坑6可以将载流子注入到所述第一多量子阱层4,通过第二v型坑7可以将载流子注入到所述第二多量子阱层5,从而可以实现在单芯片上发出两种不同波长的光;另外,第一多量子阱层4包括in

x

ga

(1-x)

n量子阱层411和alyga

(1-y)

n量子垒层412,所述第二多量子阱层5包括inzga

(1-z)

n量子阱层511,所述alyga

(1-y)

n量子垒层412可以提供高势垒阻挡载流子在第一多量子阱层中复合发光,所述in

x

ga

(1-x)

n量子阱层411中x的取值大于所述inzga

(1-z)

n量子阱层511中z的取值,高in组分的量子阱层对空穴限制作用强,不同in组分可以控制载流子在不同深度的v型坑中的输运路径,从而实现在载流子分布的均匀性,解决了混光不均的问题,优化了电路的设计。

59.可选的,在本发明的另一实施例中,对上述含v型坑双波长的led外延结构中的第一v型坑6和第二v型坑7做进一步说明,详细介绍如下:

60.所述第一v型坑6为倒六角锥形v型坑,所述第二v型坑7为倒六角锥形v型坑。

61.具体的,在本发明实施例中,所述倒六角锥形v型坑的开口区域背离所述衬底1,所述倒六角锥形v型坑的尖端区域面向所述衬底1;所述倒六角锥形v型坑是三维载流子结构,可以作为载流子传输通道,通过所述第一v型坑6可以将载流子注入到所述第一多量子阱层4中,通过所述第二v型坑7可以将载流子注入到所述第二多量子阱层5中。

62.所述第一v型坑6的开口尺寸的取值范围为98nm-280nm,所述第一v型坑6在所述第一方向a上的深度的取值范围为90nm-200nm,所述第一v型坑6的密度的取值范围为1.5e8/cm

2-6e8/cm2。

63.所述第二v型坑7的开口尺寸的取值范围为98nm-280nm,所述第二v型坑7在所述第一方向a上的深度的取值范围为90nm-200nm,所述第二v型坑7的密度的取值范围为1.5e8/cm

2-6e8/cm2。

64.具体的,在本发明实施例中,所述第一v型坑6的开口尺寸可以在98nm-280nm范围内取任意值,例如:所述第一v型坑6的开口尺寸可以为98nm、220nm、280nm等;所述第二v型坑7的开口尺寸可以在98nm-280nm范围内取任意值,例如:所述第二v型坑7的开口尺寸可以为98nm、200nm、280nm等;其中,所述第一v型坑6和所述第二v型坑7的开口尺寸不相同,所述第一v型坑6的开口尺寸大于所述第二v型坑7的开口尺寸。

65.所述第一v型坑6在所述第一方向a上的深度的取值范围可以在90nm-200nm范围内取任意值,例如:所述第一v型坑6的深度可以为90nm、175nm、200nm等;所述第二v型坑7在所述第一方向a上的深度的取值范围可以在90nm-200nm范围内取任意值,例如:所述第二v型坑7的深度可以为90nm、150nm、200nm等;其中,所述第一v型坑6和所述第二v型坑7在所述第一方向a上的深度不相同,所述第一v型坑6的深度大于所述第二v型坑7的深度。

66.所述第一v型坑6的密度可以在1.5e8/cm

2-6e8/cm2范围内取任意值,例如:所述第一v型坑6的密度可以为1.5e8/cm2、3e8/cm2、6e8/cm2等;所述第二v型坑7的密度可以在1.5e8/cm

2-6e8/cm2范围内取任意值,例如:所述第二v型坑7的密度可以为1.5e8/cm2、3e8/cm2、6e8/cm2等;其中,所述第一v型坑6和所述第二v型坑7的密度可以相同也可以不相同。

67.可选的,在本发明的另一实施例中,对上述含v型坑双波长的led外延结构进行进一步说明,参考图2,图2为本发明实施例提供的另一种含v型坑双波长的led外延结构的结构示意图,结合图2,所述led外延结构还包括:

68.依次位于所述衬底1面向所述n型氮化镓层2一侧的缓冲层8、三维形核层9以及二维合并层10。

69.具体的,在本发明实施例中,所述缓冲层8为铝氮缓冲层;所述三维形核层9位于所述缓冲层8背离所述衬底1的一侧,所述二维合并层10位于所述三维形核层9背离所述缓冲层8的一侧。

70.位于所述低温氮化镓层3和所述第一多量子阱层4之间的应力释放层11。

71.具体的,在本发明实施例中,所述第一v型坑6还贯穿所述应力释放层11,所述第一v型坑6在贯穿所述第一多量子阱层4、所述第二多量子阱层5和所述应力释放层11的基础上延伸至所述低温氮化镓层3,但所述第一v型坑6并没有贯穿所述低温氮化镓层3。

72.位于所述第二多量子阱层5背离所述第一多量子阱层4一侧的p型电子阻挡层12和p型氮化镓层13。

73.具体的,在本发明实施例中,所述p型电子阻挡层填充所述第一v型坑和所述第二v型坑;所述p型氮化镓层13位于所述p型电子阻挡层12背离所述衬底1的一侧;由于在gan材料体系中,空穴的有效质量大约是电子有效质量的五倍,导致空穴的迁移率低,只能注入到靠近p型氮化镓层13的几个量子阱中,通常认为在多量子阱led中发光主要在靠近p型氮化镓的量子阱区域,因此将所述第二多量子阱层5设置的靠近p型氮化镓层有利于载流子在第二多量子阱层5中发光。

74.可选的,在本发明的另一实施例中,对上述含v型坑双波长的led外延结构再次进行进一步说明,详细介绍如下:

75.所述in

x

ga

(1-x)

n量子阱层411中x的取值范围为0≤x≤0.5,所述alyga

(1-y)

n量子垒层412中y的取值范围为0≤y≤0.5,所述inzga

(1-z)

n量子阱层511中z的取值范围为0≤z≤0.5。

76.具体的,在本发明实施例中,所述in

x

ga

(1-x)

n量子阱层411中x可以为0、0.3、0.5等,所述alyga

(1-y)

n量子垒层412中y可以为0、0.3、0.5等,所述inzga

(1-z)

n量子阱层511中z可以为0、0.3、0.5,所述x、y、z的取值可以根据所述含v型坑双波长的led外延结构的性能决定;其中in

x

ga

(1-x)

n量子阱层411中x的取值始终大于inzga

(1-z)

n量子阱层511中z的取值。

77.所述低温氮化镓层3的厚度范围为50nm-400nm,所述in

x

ga

(1-x)

n量子阱层411的厚度范围为2nm-4nm,所述alyga

(1-y)

n量子垒层412的厚度范围为2nm-4nm,所述inzga

(1-z)

n量子阱层511的厚度范围为2nm-4nm,所述第一gan量子垒层413的厚度范围为8nm-15nm,所述第二gan量子垒层512的厚度范围为8nm-15nm。

78.具体的,在本发明实施例中,所述低温氮化镓层3的厚度可以在50nm-400nm范围内取任意值,例如:所述低温氮化镓层3的厚度可以为50nm、100nm、250nm、400nm等;所述in

x

ga

(1-x)

n量子阱层411的厚度可以在2nm-4nm范围内取任意值,例如:所述in

x

ga

(1-x)

n量子阱层411的厚度可以为2nm、3nm、3.5nm、4nm等;所述inzga

(1-z)

n量子阱层511的厚度可以在2nm-4nm范围内取任意值,例如:所述inzga

(1-z)

n量子阱层511的厚度可以为2nm、3nm、3.5nm、4nm等;所述第一gan量子垒层413的厚度可以在8nm-15nm范围内取任意值,例如:所述第一gan量子垒层413的厚度可以为8nm、10nm、13.5nm、15nm等;所述第二gan量子垒层512的厚度可以在8nm-15nm范围内取任意值,例如:所述第二gan量子垒层512的厚度可以为8nm、10nm、13.5nm、15nm等。

79.所述第一多量子阱层4的周期数的取值范围为3-9,所述第二多量子阱层5的周期数的取值范围为3-9。

80.具体的,在本发明实施例中,所述第一多量子阱层4包括在所述第一方向a上依次堆叠设置的多组第一堆叠膜层41,所述周期数即为所述第一堆叠膜层41的堆叠层数;一组第一堆叠膜层41为一个周期,则所述一个周期的第一多量子阱层4包括在所述第一方向a上依次设置的in

x

ga

(1-x)

n量子阱层411、alyga

(1-y)

n量子垒层412和第一gan量子垒层413,图2中所示的第一多量子阱层4包括在所述第一方向a上依次堆叠设置的n组第一堆叠膜层41,即n为所述第一多量子阱层4的周期数,所述周期数的取值范围为3-9。

81.例如,所述第一多量子阱层4的周期数为3,则所述第一多量子阱层4包括在所述第一方向a上依次设置的in

x

ga

(1-x)

n量子阱层411、alyga

(1-y)

n量子垒层412、第一gan量子垒层413、in

x

ga

(1-x)

n量子阱层411、alyga

(1-y)

n量子垒层412、第一gan量子垒层413、in

x

ga

(1-x)

n量子阱层411、alyga

(1-y)

n量子垒层412、第一gan量子垒层413。

82.所述第二多量子阱层5包括在所述第一方向a上依次堆叠设置的多组第二堆叠膜层51,所述周期数即为所述第二堆叠膜层51的堆叠层数;一组第二堆叠膜层51为一个周期,则所述一个周期的第二多量子阱层5包括在所述第一方向a上依次设置的inzga

(1-z)

n量子阱层511和第二gan量子垒层512,图2中所示的第二多量子阱层5包括在所述第一方向a上依次堆叠设置的m组第二堆叠膜层51,即m为所述第二多量子阱层5的周期数,所述周期数的取值范围为3-9。

83.例如,所述第二多量子阱层5的周期数为3,则所述第二多量子阱层5包括在所述第一方向a上依次设置的inzga

(1-z)

n量子阱层511、第二gan量子垒层512、inzga

(1-z)

n量子阱层511、第二gan量子垒层512、inzga

(1-z)

n量子阱层511、第二gan量子垒层512。

84.本发明实施例中还提供了一种含v型坑双波长的led外延结构的制备方法,参考图3,图3为本发明实施例提供的一种含v型坑双波长的led外延结构的制备方法的流程示意图,结合图3,所述制备方法包括:

85.s100:提供一衬底1。

86.具体的,在该步骤s100中,所述衬底1包括但不限定为si衬底、pss蓝宝石衬底、sic衬底。

87.s200:在所述衬底1的一侧依次形成n型氮化镓层2和低温氮化镓层3。

88.具体的,在该步骤s200中,需要在温度范围为600℃-800℃的条件下形成所述低温氮化镓层3,例如,形成所述低温氮化镓层3的温度条件可以为600℃、750℃、800℃等。

89.s300:在所述低温氮化镓层3背离所述衬底1的一侧依次形成第一多量子阱层4和第二多量子阱层5。

90.其中led外延结构包括第一v型坑6和第二v型坑7,在第一方向上a,所述第一v型坑6贯穿所述第一多量子阱层4和所述第二多量子阱层5,以及部分延伸至所述低温氮化镓层3,所述第二v型坑6贯穿所述第二多量子阱层5,所述第一方向a垂直于所述衬底1且由所述衬底1指向所述n型氮化镓层2。

91.具体的,在该步骤s300中,所述第一v型坑6贯穿所述第一多量子阱层4和所述第二多量子阱层5,并且所述第一v型坑6在贯穿所述第一多量子阱层4和所述第二多量子阱层5的基础上延伸至所述低温氮化镓层3,但所述第一v型坑6并没有贯穿所述低温氮化镓层3。

92.所述第一多量子阱层4包括在所述第一方向a上依次堆叠设置的多组第一堆叠膜层41,所述第一堆叠膜层41包括在所述第一方向a上依次叠层设置的in

x

ga

(1-x)

n量子阱层411、alyga

(1-y)

n量子垒层412和第一gan量子垒层413。

93.所述第二多量子阱层5包括在所述第一方向a上依次堆叠设置的多组第二堆叠膜层51,所述第二堆叠膜层51包括在所述第一方向a上依次叠层设置的inzga

(1-z)

n量子阱层511和第二gan量子垒层512,所述in

x

ga

(1-x)

n量子阱层411中x的取值大于所述inzga

(1-z)

n量子阱层511中z的取值。

94.通过上述描述可知,本发明提供了一种含v型坑双波长的led外延结构的制备方法,所述制备方法包括提供衬底1,在衬底1的一侧依次形成n型氮化镓层2、低温氮化镓层3、第一多量子阱层4和第二多量子阱层5;所述n型氮化镓层2具有线位错,通过形成所述低温氮化镓层3,随着生长所述低温氮化镓层3的厚度的增加,使得生长应力不断积累在多量子阱层中或者低温氮化镓层3靠近多量子阱层的位置,进而使得线位错不断增多,从而至少在所述第一多量子阱层4和所述第二多量子阱层5形成两种不同深度的v型坑,不同深度的v型坑间隔分布可以构成v型坑阵列,使得有源发光区由传统的平面结构变为立体结构,通过第一v型坑6可以将载流子注入到所述第一多量子阱层4,通过第二v型坑7可以将载流子注入到所述第二多量子阱层5,从而可以实现在单芯片上发出两种不同波长的光;另外,第一多量子阱层4包括in

x

ga

(1-x)

n量子阱层411和alyga

(1-y)

n量子垒层412,所述第二多量子阱层5包括inzga

(1-z)

n量子阱层511,所述alyga

(1-y)

n量子垒层412可以提供高势垒阻挡载流子在第一多量子阱层4中复合发光,所述in

x

ga

(1-x)

n量子阱层411中x的取值大于所述inzga

(1-z)

n量子阱层511中z的取值,高in组分的量子阱层对空穴限制作用强,不同in组分可以控制载流子在不同深度的v型坑中的输运路径,从而实现在载流子分布的均匀性,解决了混光不均的问题,优化了电路的设计。

95.可选的,在本发明的另一实施例中,对上述所述含v型坑双波长的led外延结构的制备方法进行进一步介绍,参考图4,图4为本发明实施例提供的零一种含v型坑双波长的led外延结构的制备方法的流程示意图详细如下,所述制备方法还包括:

96.s400:在所述衬底面向所述n型氮化镓层2的一侧依次形成缓冲层8、三维形核层9以及二维合并层10。

97.具体的,该步骤s400是在步骤s200形成n型氮化镓层2之前执行,在该步骤s400中,所述缓冲层8为铝氮缓冲层;在形成所述三维形核层9的过程中以gan与aln之间的晶格失配作为驱动力,在小氨气氛围下,利用沉积分解实现三维岛状生长模式;在形成二维合并层10的过程中,在高温大氨气氛围下,利用扩散实现侧向生长模式,将三维岛状合并gan平面,从而降低位错密度。

98.s500:在所述低温氮化镓层3面向所述第一多量子阱层4的一侧形成应力释放层11。

99.具体的,该步骤s500是在步骤s200形成低温氮化镓层之后执行,在该步骤s500中,所述第一v型坑6还贯穿所述应力释放层11,所述第一v型坑6在贯穿所述第一多量子阱层4、所述第二多量子阱层5和所述应力释放层11的基础上延伸至所述低温氮化镓层3,但所述第一v型坑6并没有贯穿所述低温氮化镓层3;形成所述应力释放层11的目的是为了将v型坑进一步打开,利用相对较低的in组分为后面的量子阱缓冲应力。

100.s600:在所述第二多量子阱层5背离所述第一多量子阱层4的一侧依次形成p型电子阻挡层12和p型氮化镓层13。

101.具体的,该步骤s600是在步骤s300形成第一v型坑6和第二v型坑7之后执行的,在该步骤s600中,所述p型电子阻挡层12填充所述第一v型坑6和第二v型坑7。

102.可选的,本发明示例了一种含v型坑双波长的led外延结构的制备方法,这种制备方法采用设备mocvd在si衬底上制备含v型坑双波长的led外延结构,其中以三甲基镓tmga和三乙基镓tega为ga源,氨气nh3为n源,三甲基铟tmin为in源,三甲基铝tmal为al源,h2、n2为载气,硅烷sih4为掺杂源,二茂镁cp2mg为p型掺杂源,石墨盘为载盘来进行制备,其具体实施过程如下:

103.步骤1:对si衬底进行处理。

104.具体的,在温度范围为900℃-1150℃的条件下通入h2对si衬底进行5min氢化处理,本发明实施例中以高温1000℃为最优实施例对si衬底进行氢化处理,去除衬底表面的杂质、划痕等;在si衬底的一侧预铺al层,阻隔ga元素回融腐蚀si衬底。

105.步骤2:形成aln缓冲层。

106.具体的,在温度范围为600℃-800℃的条件下通入nh3进行反应,本发明实施例中以在低温700℃的条件下通入nh3为最优实施例进行反应,可以将al层固定在si衬底的一侧,进而形成一层薄的aln层;再通入tmal、sih4、nh3、h2、n2,在温度范围为900℃-1150℃的条件下生长aln缓冲层,在本发明实施例中以在温度1000℃的条件下生长aln缓冲层为最优实施例;所述aln缓冲层的厚度范围为5nm-50nm,si和al的摩尔比的取值范围为0.05-0.5,在本发明实施例中以aln缓冲层的厚度取值20nm,si和al的摩尔比取值0.2为最优实施例。

107.步骤3:形成三维形核层9。

108.具体的,通入nh3、h2、n2,在温度范围为800℃-1000℃、nh3组分取值范围为30%-80%和时间取值范围为0.5min-3min的条件下,以gan与aln之间的晶格失配作为驱动力,在小氨气氛围下,利用沉积分解实现三维岛状生长模式,进而形成三维形核层9;在本发明实施例中以温度900℃、nh3组分20%和时间1min的条件下形成三维形核层9为最优实施例。

109.步骤4:形成二维合并层10。

110.具体的,通入nh3、h2、n2,在温度范围为900℃-1200℃,nh3组分取值范围为70%-100%和时间取值范围为0.5min-3min的条件下,在高温大氨气氛围下,利用扩散实现侧向生长模式,将三维岛状合并gan平面,形成所述二维合并层10,从而降低位错密度;本发明实施例中以温度1150℃、nh3组分取值80%和时间2min的条件下形成二维合并层10为最优实施例。

111.步骤5:形成n型氮化镓层2。

112.具体的,通入tmga、sih4、nh3、h2、n2,在温度范围为900℃-1200℃和sih4的浓度为8e18/cm3的条件下形成所述n型氮化镓层2,所述n型氮化镓层2的厚度的取值范围为1500nm-2500nm;本发明实施例中以在温度1070℃的条件下形成n型氮化镓层2,且n型氮化镓层2的厚度为2000nm为最优实施例。

113.步骤6:形成低温氮化镓层3。

114.具体的,通入tmga、nh3、n2,在温度范围为600℃-800℃的条件下形成低温氮化镓层3,可以将位错密度转化形成v型坑,所述低温氮化镓层3的厚度的取值范围为50nm-400nm;

本发明实施例中以在温度750℃的条件下形成低温氮化镓层3,且低温氮化镓层3的厚度为100nm为最优实施例。

115.步骤7:形成应力释放层11。

116.具体的,通入tega、tmin、nh3、h2、n2,以5nm ingan阱层和2nm gan超晶格垒层为1个周期,生长25-35个周期形成应力释放层11,所述应力释放层11的总厚度的取值范围为150nm-250nm,本发明实施例中以生长30个周期形成应力释放层11,且所述应力释放层11的总厚度为210nm为最优实施例;其中,ingan阱层的温度范围为700℃-850℃,gan超晶格垒层的温度范围为800℃-1000℃,本发明实施例中以ingan阱层的温度为800℃和gan超晶格垒层的温度为880℃为最优实施例;目的是将v型坑进一步打开,利用相对较低的in组分为后面的量子阱缓冲应力,同时周期性阱垒结构还有利于电流扩展。

117.步骤8:形成第一多量子阱层4。

118.具体的,通入tega、tmin、tmal、sih4、nh3、h2、n2(形成in

x

ga

(1-x)

n量子阱层411时不通h2,alyga

(1-y)

n量子垒层412和第一gan量子垒层413中掺si),in

x

ga

(1-x)

n量子阱层411厚度为2.5nm,alyga

(1-y)

n量子垒层412和第一gan量子垒层413的总厚度为10.5nm,所述第一多量子阱层4的总厚度的取值范围为10nm-16nm;其中in

x

ga

(1-x)

n量子阱层411的温度的取值范围为700℃-850℃,alyga

(1-y)

n量子垒层412的温度的取值范围为700℃-850℃,al组分的取值范围为0%-50%,第一gan量子垒层413的温度的取值范围为800℃-1000℃,阱垒周期数的取值范围为3-9。

119.在本发明实施例中以第一多量子阱层4的总厚度为13nm、in

x

ga

(1-x)

n量子阱层411的温度为750℃、alyga

(1-y)

n量子垒层412的温度为750℃、al组分为20%、第一gan量子垒层413的温度为880℃、阱垒周期数为4为最优实施例。

120.步骤9:形成第二多量子阱层5。

121.具体的,通入tega、tmin、sih4、nh3、h2、n2(生长inzga

(1-z)

n量子阱层511时不通h2,第二gan量子垒层512中掺si),inzga

(1-z)

n量子阱层511厚3nm,第二gan量子垒层512厚11nm,所述第二多量子阱层5的总厚度的取值范围为10nm-16nm,其中inzga

(1-z)

n量子阱层511的温度的取值范围为700℃-850℃,第二gan量子垒层512的温度的取值范围为800℃-1000℃,阱垒周期数的取值范围为3-9。

122.在本发明实施例中以第二多量子阱层5的总厚度为14nm、inzga

(1-z)

n量子阱层511的温度为780℃、第二gan量子垒层512的温度为880℃、阱垒周期数为4为最优实施例。

123.步骤10:形成p型电子阻挡层12。

124.具体的,所述p型电子阻挡层12为p型algan电子阻挡层,通入tmal,tmga、cp2mg、nh3、h2、n2,在温度范围为850℃-1050℃、mg的浓度为1e19/cm3、al组分的取值范围为0%-50%的条件下形成p型电子阻挡层12,所述p型电子阻挡层12的厚度的取值范围为150nm-250nm;本发明实施例中以在温度为950℃、mg的浓度为1e19/cm3、al组分为30%的条件下形成p型电子阻挡层12,且所述p型电子阻挡层12的厚度为200nm为最优实施例。

125.步骤11:形成p型氮化镓层13。

126.具体的,通入tmga,cp2mg,nh3、h2、n2,在温度范围为800℃-1200℃且mg浓度的取值范围为1e19/cm

3-4e19/cm3的条件下形成p型氮化镓层13,所述p型氮化镓层13的厚度的取值范围为200nm-600nm;本发明实施例中以在温度为1050℃且mg的浓度为3e19/cm3的条件下

形成p型氮化镓层13,且所述p型氮化镓层13的厚度为400nm为最优实施例。

127.步骤12:进行降温退火处理,结束生长。

128.在本发明示例的这种实施例中,对上述含v型坑双波长的led外延结构进行测试及芯片制作,通过el进行光电参数测试可以得出,相比传统结构,通过v型坑设计使得有源发光区由传统的平面结构变为立体结构,增加了水平的pn结,可以控制载流子输运路径以及载流子分布,从而实现双波长发光,但存在第一多量子阱层4中发光峰强度较弱的问题。

129.可选的,在本发明的另一实施例中,考虑到第一多量子阱层4中发光峰强度较弱这一问题,本发明的另一实施例还示例了几种制备含v型坑双波长的led外延结构可选的实现方式,详细方案如下:

130.第一种、基于上述示例的一种含v型坑双波长的led外延结构的制备方法,对所述步骤6形成低温氮化镓层3提供了另一种可选实现方式:

131.具体的,通入tmga、nh3、n2,在温度范围为600℃-800℃的条件下形成低温氮化镓层3,所述低温氮化镓层3的厚度的取值范围为50nm-400nm;本发明实施例中以在温度600℃的条件下形成低温氮化镓层3,且低温氮化镓层3的厚度为250nm为最优实施例。

132.在本发明实施例中,降低了所述低温氮化镓层3的生长温度,增加了所述低温氮化镓层3的厚度,通过扫面电镜结果显示相比于上述示例的制备方法,v型坑尺寸增大,且出现小尺寸v型坑;el测试结果显示,靠近n型氮化镓层2的第一多量子阱层4发光峰强度有所提升。

133.第二种、基于上述第一种示例的制备方法,对所述步骤8形成第一多量子阱层4和步骤9形成第二多量子阱层5提供了另一种可选的实现方式:

134.对于上述步骤8形成第一多量子阱层4的另一种可选的实现方式,具体的,通入tega、tmin、tmal、sih4、nh3、h2、n2(形成in

x

ga

(1-x)

n量子阱层411时不通h2,alyga

(1-y)

n量子垒层412和第一gan量子垒层413中掺si),in

x

ga

(1-x)

n量子阱层411厚度为2.5nm,alyga

(1-y)

n量子垒层412和第一gan量子垒层413的总厚度为10.5nm,所述第一多量子阱层4的总厚度的取值范围为10nm-16nm;其中in

x

ga

(1-x)

n量子阱层411的温度的取值范围为700℃-850℃,alyga

(1-y)

n量子垒层412的温度的取值范围为700℃-850℃,al组分的取值范围为0%-50%,第一gan量子垒层413的温度的取值范围为800℃-1000℃,阱垒周期数的取值范围为3-9。

135.在本发明实施例中以第一多量子阱层4的总厚度为13nm、in

x

ga

(1-x)

n量子阱层411的温度为750℃、alyga

(1-y)

n量子垒层412的温度为750℃、al组分从30%线性减少到10%、第一gan量子垒层413的温度为880℃、阱垒周期数为5为最优实施例。

136.对于上述步骤9形成第二多量子阱层5的另一种可选的实现方式,具体的,通入tega、tmin、sih4、nh3、h2、n2(生长inzga

(1-z)

n量子阱层511时不通h2,第二gan量子垒层512中掺si),inzga

(1-z)

n量子阱层511厚3nm,第二gan量子垒层512厚11nm,所述第二多量子阱层5的总厚度的取值范围为10nm-16nm,其中inzga

(1-z)

n量子阱层511的温度的取值范围为700℃-850℃,第二gan量子垒层512的温度的取值范围为800℃-1000℃,阱垒周期数的取值范围为3-9。

137.在本发明实施例中以第二多量子阱层5的总厚度为14nm、inzga

(1-z)

n量子阱层511的温度为780℃、第二gan量子垒层512的温度为880℃、阱垒周期数为3为最优实施例。

138.本发明实施例中,增加了第一多量子阱层4的阱垒周期数、降低了第二多量子阱层

5的阱垒周期数且使得第一多量子阱层4中alyga

(1-y)

n量子垒层412的al组分从30%线性减少到10%,通过el测试结果显示,相比于上述第一种示例的制备方法,靠近n型氮化镓层2的第一多量子阱层4发光峰强度有所提升,且发光峰强度相比第二多量子阱层5发光强度更强。

139.以上对本发明所提供的一种含v型坑双波长的led外延结构及其制备方法进行了详细介绍,本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的一般技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本发明的限制。

140.需要说明的是,本说明书中的各个实施例均采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似的部分互相参见即可。对于实施例公开的装置而言,由于其与实施例公开的方法相对应,所以描述的比较简单,相关之处参见方法部分说明即可。

141.还需要说明的是,在本文中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备所固有的要素,或者是还包括为这些过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。

142.对所公开的实施例的上述说明,使本领域专业技术人员能够实现或使用本发明。对这些实施例的多种修改对本领域的专业技术人员来说将是显而易见的,本文中所定义的一般原理可以在不脱离本发明的精神或范围的情况下,在其它实施例中实现。因此,本发明将不会被限制于本文所示的这些实施例,而是要符合与本文所公开的原理和新颖特点相一致的最宽的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1