具有自对准到外延源极的后侧接触部的全环绕栅极集成电路结构的制作方法

本公开的实施例属于集成电路结构和处理的领域,具体而言,属于具有自对准到外延源极区或漏极区的后侧接触部的全环绕栅极集成电路结构,以及制造具有自对准到外延源极区或漏极区的后侧接触部的全环绕栅极集成电路结构的方法的领域。

背景技术:

1、过去几十年来,集成电路中特征的缩放已经成为不断成长的半导体行业背后的驱动力。通过缩放使特征越来越小允许在半导体芯片的有限占用区域上实现提高密度的功能单元。例如,缩小晶体管尺寸允许在芯片上结合更大数量的存储器或逻辑器件,有助于具有更大容量的产品的制造。不过,对越来越大容量的追求并非毫无问题。优化每个器件性能的必要性变得越来越显著。

2、在集成电路器件的制造当中,随着器件尺寸的持续缩小,多栅极晶体管(例如,三栅极晶体管)变得越来越占据主导地位。在常规工艺中,三栅极晶体管通常是在体硅衬底或绝缘体上硅衬底上制造的。在一些情况下,体硅衬底是优选的,因为它们的成本更低,并且因为它们能够进行较不复杂的三栅极制造工艺。在另一方面中,在微电子器件尺度缩小到10纳米(nm)节点以下的同时保持迁移率改进和短沟道控制给器件制造提出了挑战。用于制造器件的纳米线提供了改进的短沟道控制。

3、不过,缩放多栅极和纳米线晶体管并非没有后果。随着微电子电路的这些功能构建块的尺度减小并随着给定区域中制造的功能构建块的绝对数量增大,对用于图案化这些构建块的光刻工艺的约束已经变得十分巨大。具体而言,在半导体堆叠体中图案化的特征的最小尺度与此类特征间的间距之间可能存在着折中关系。

技术实现思路

技术特征:

1.一种集成电路结构,包括:

2.根据权利要求1所述的集成电路结构,其中,所述导电接触结构将所述第一外延源极或漏极结构之一耦合到后侧接触部。

3.根据权利要求1或2所述的集成电路结构,其中,所述第一外延源极或漏极结构和所述第二外延源极或漏极结构均为非离散的外延源极或漏极结构。

4.根据权利要求1或2所述的集成电路结构,其中,所述纳米线的第一垂直布置结构在第一子鳍上方,并且所述纳米线的第二垂直布置结构在第二子鳍上方,并且其中,所述第二子鳍在与所述第一外延源极或漏极结构之一相邻的所述第二外延源极或漏极结构之一下方垂直延伸。

5.根据权利要求4所述的集成电路结构,其中,电介质壁将所述第一外延源极或漏极结构之一与所述第二外延源极或漏极结构之一分隔开,并且电介质层至少部分地在所述第一外延源极或漏极结构之一和所述第二外延源极或漏极结构之一上,其中,所述电介质壁与所述电介质层不同。

6.根据权利要求1或2所述的集成电路结构,其中,所述导电结构在横向上不延伸超过所述第一外延源极或漏极结构之一。

7.一种集成电路结构,包括:

8.根据权利要求7所述的集成电路结构,其中,所述导电接触结构将所述第一外延源极或漏极结构之一耦合到后侧接触部。

9.根据权利要求7或8所述的集成电路结构,其中,所述第一外延源极或漏极结构和所述第二外延源极或漏极结构均为非离散的外延源极或漏极结构。

10.根据权利要求7或8所述的集成电路结构,其中,所述第一鳍在第一子鳍上方,并且所述第二鳍在第二子鳍上方,并且其中,所述第二子鳍在与所述第一外延源极或漏极结构之一相邻的所述第二外延源极或漏极结构之一下方垂直延伸。

11.根据权利要求10所述的集成电路结构,其中,电介质壁将所述第一外延源极或漏极结构之一与所述第二外延源极或漏极结构之一分隔开,并且电介质层至少部分地在所述第一外延源极或漏极结构之一和所述第二外延源极或漏极结构之一上,其中,所述电介质壁与所述电介质层不同。

12.根据权利要求7或8所述的集成电路结构,其中,所述导电结构在横向上不延伸超过所述第一外延源极或漏极结构之一。

13.一种计算装置,包括:

14.根据权利要求13所述的计算装置,还包括:

15.根据权利要求13或14所述的计算装置,还包括:

16.根据权利要求13或14所述的计算装置,还包括:

17.根据权利要求13或14所述的计算装置,其中,所述部件是封装集成电路管芯。

18.一种计算装置,包括:

19.根据权利要求18所述的计算装置,还包括:

20.根据权利要求18或19所述的计算装置,还包括:

21.根据权利要求18或19所述的计算装置,还包括:

22.根据权利要求18或19所述的计算装置,其中,所述部件是封装集成电路管芯。

技术总结

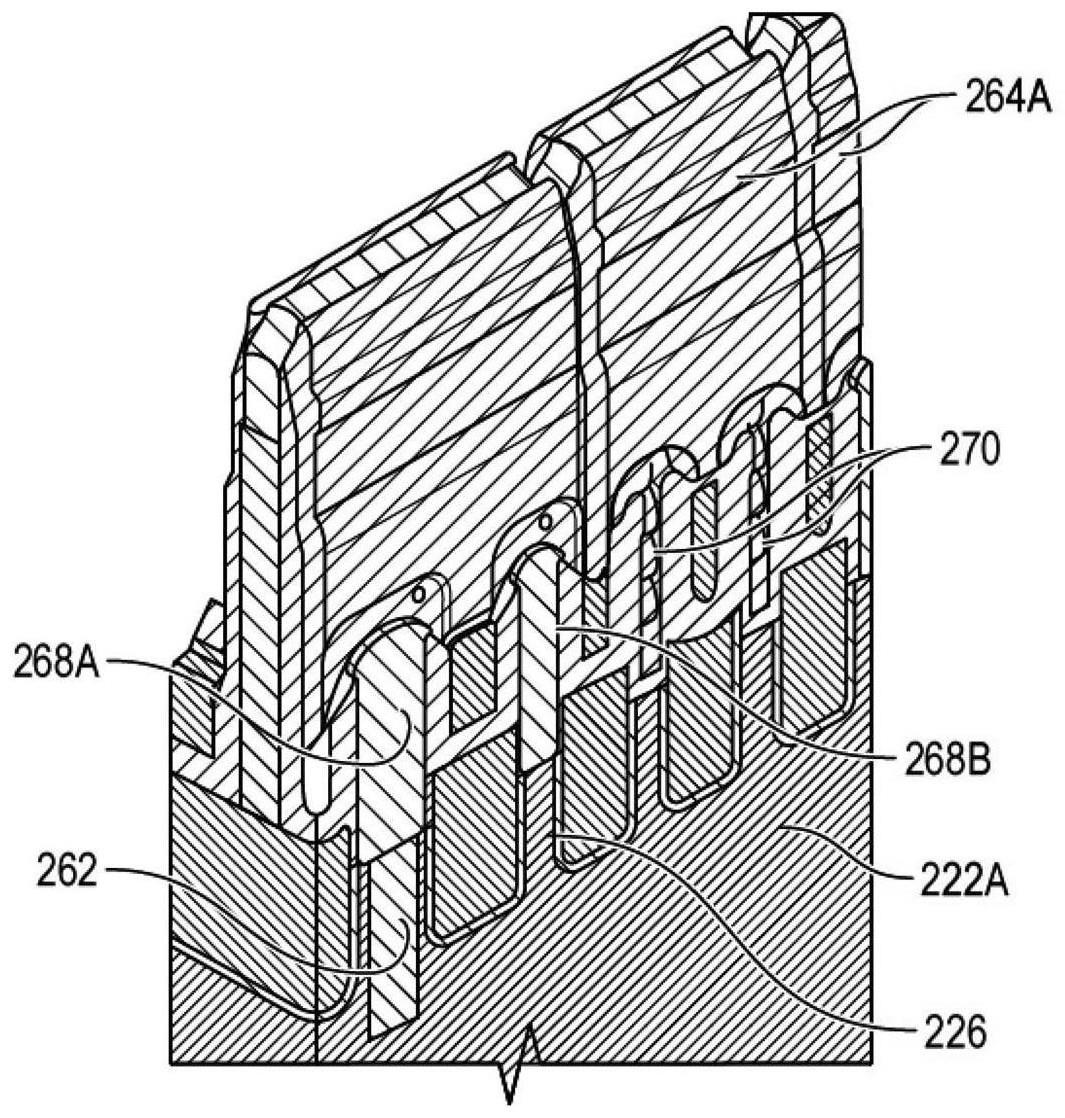

描述了具有自对准到外延源极或漏极区的后侧接触部的全环绕栅极集成电路结构。例如,一种集成电路结构包括纳米线的第一垂直布置结构和纳米线的第二垂直布置结构。栅极堆叠体位于纳米线的第一和第二垂直布置结构上方。第一外延源极或漏极结构位于纳米线的第一垂直布置结构的末端处。第二外延源极或漏极结构位于纳米线的第二垂直布置结构的末端处。导电结构在第一外延源极或漏极结构之一的垂直下方并且与其接触。

技术研发人员:G·布歇,A·纳瓦比-设拉子,A·C-H·韦,M·J·科布林斯基,S·米尔斯,P·帕特尔

受保护的技术使用者:英特尔公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!