功率半导体的晶圆片级芯片规模封装及其制造方法与流程

下面的描述涉及功率半导体的晶圆片级芯片规模封装及其制造方法,其可以通过在半导体衬底的上表面上形成具有预定厚度的前金属层来防止由于半导体衬底与后金属层的热膨胀系数之间的差异而导致的半导体管芯的翘曲。

背景技术:

1、目前,半导体工业的主要趋势之一是尽可能减小半导体器件的尺寸。因此,提出芯片规模封装(芯片尺寸封装)以将半导体器件封装的尺寸减小为像芯片一样。特别地,晶圆片级芯片规模封装(wlcsp)可以由半导体晶片一次性组装和制造封装。因此,wlcsp可以以低成本和良好的电子特性制造具有芯片尺寸的最小封装。

2、然而,封装的厚度可以根据功率半导体的类型而减小。在一个示例中,典型的封装厚度大约超过100μm。由于mosfet类型的wlcsp需要较低的导通电阻(低ron),即,低漏-源电阻(低rdson)和低源-源电阻(rsson),因此设计与典型封装相比更薄厚度的封装可能是重要的。

3、因此,在传统技术中已经存在减小半导体衬底的厚度以及增加后金属层的厚度的方法。

4、后金属层可以实现为公共漏电极,并且可以通过增加后金属层的厚度来减小漏电极的电阻。

5、然而,在具有这样的结构的封装中,由于半导体衬底与后金属层的热膨胀系数之间的差异而可能发生翘曲,并且随着半导体衬底的厚度变得更薄以及随着后金属层的厚度变得更厚,翘曲可能变得更严重。在这种情况下,可能对半导体器件施加过大的应力。因此,当封装安装在印刷电路板(pcb)上时,组装质量可能较差,并且薄半导体衬底可能破裂和破坏。

技术实现思路

1、提供该

技术实现要素:

是为了以简化的形式介绍一系列构思,这些构思将在下面的具体实施方式中进一步描述。该发明内容不旨在标识所要求保护的主题的关键特征或必要特征,也不旨在用作在确定所要求保护的主题的范围时的帮助。

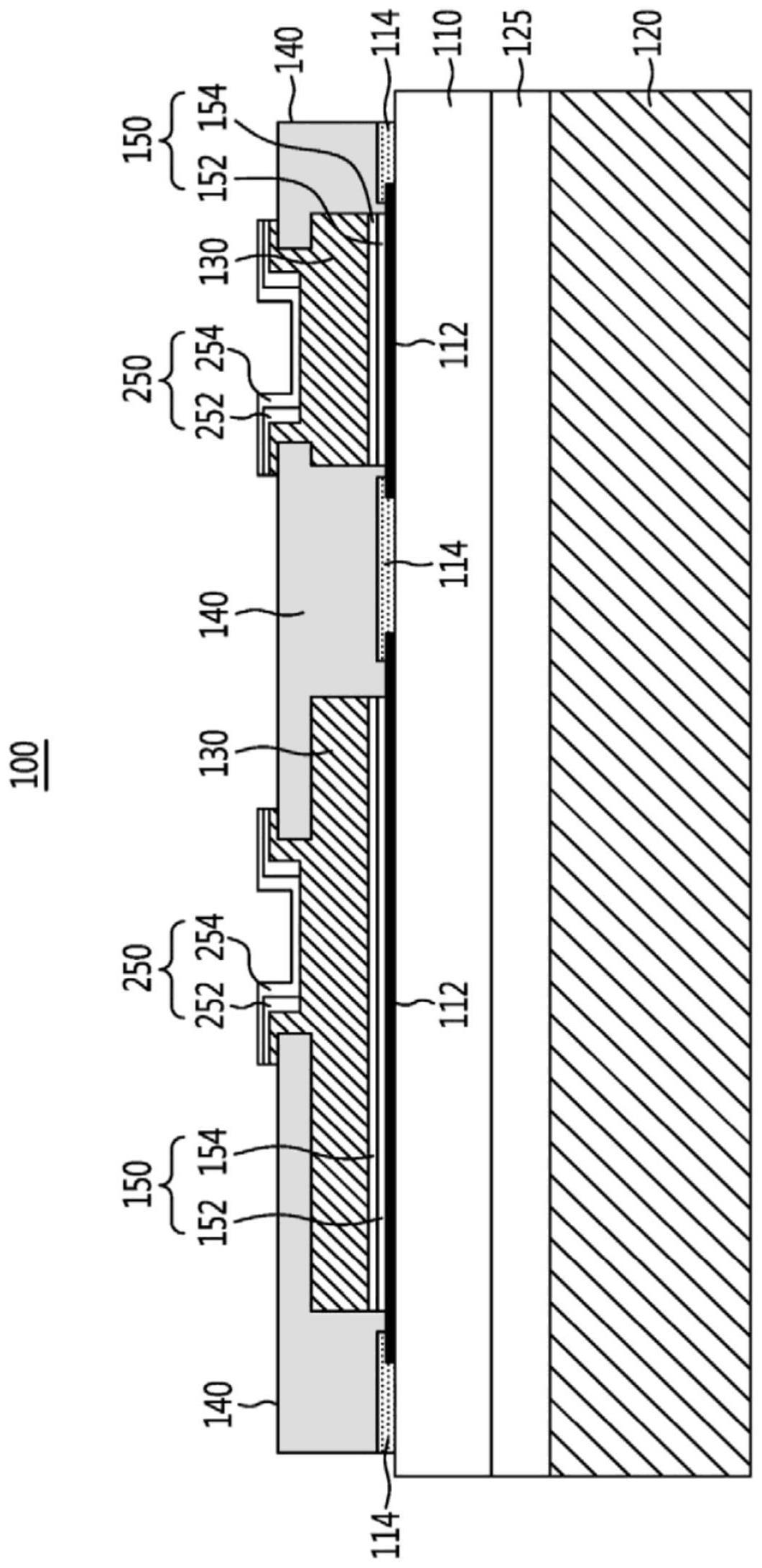

2、在一般方面,一种晶圆片级芯片规模封装,包括:具有第一厚度的半导体衬底;形成在半导体衬底上的输入-输出垫;形成在输入-输出垫上的具有第二厚度的前金属层;形成在半导体衬底的下表面上的具有第三厚度的后金属层;以及形成在半导体衬底上的金属凸块。

3、第一厚度可以小于60μm,并且第二厚度可以在10μm至60μm的范围内。第三厚度可以在10μm至100μm的范围内。

4、前金属层和后金属层可以包括铜(cu)。

5、该晶圆片级芯片规模封装还可以包括:围绕前金属层的聚酰亚胺层;以及形成在前金属层上的种子金属层。

6、前金属层可以形成在除了输入-输出垫之外的半导体衬底上。

7、在将该晶圆片级芯片规模封装安装在pcb基板上的工艺中,该后金属层的翘曲可以被该前金属层和该聚酰亚胺层抵消。

8、该前金属层和该后金属层由具有相同热膨胀系数的相同金属形成。

9、该金属凸块可以包括可焊接金属层。

10、在另一一般方面,一种晶圆片级芯片规模封装可以包括:具有第一厚度的半导体衬底;形成在该半导体衬底的上表面上的具有第二厚度的前金属层;以及形成在该半导体衬底的下表面上的具有第三厚度的后金属层,其中,前金属层和后金属层具有相同的热膨胀系数,使得该封装被构造成当该封装安装在pcb衬底上时保持平衡状态。

11、第一厚度大于第二厚度,并且第三厚度大于第一厚度。

12、在一般方面,一种晶圆片级芯片规模封装的制造方法,包括:制备具有第一厚度的半导体衬底;在半导体衬底上形成第一种子金属层;在第一种子金属层上形成光掩模图案并且形成具有第二厚度的前金属层;去除在除了前金属层之外的区域中形成的光掩模图案和第一种子金属层;在半导体衬底上形成聚酰亚胺层;在聚酰亚胺层上形成第二种子金属层;在第二种子金属层上形成金属凸块;以及在半导体衬底的下表面上形成具有第三厚度的后金属层。

13、该前金属层的第二厚度可以最薄,并且后金属层的第三厚度可以最厚。

14、第一厚度可以小于60μm,并且第二厚度可以在10μm至60μm的范围内,并且第三厚度可以在10μm至100μm的范围内。

15、后金属层的翘曲可以被前金属层和聚酰亚胺层抵消,并且因此,安装在pcb基板上的该晶圆片级芯片规模封装可以保持平衡状态。

16、该晶圆片级芯片规模封装的制造方法还可以包括:在半导体衬底上形成输入-输出垫,并且前金属层可以形成在半导体衬底的除了输入-输出垫之外的整个区域上。

17、根据以下具体实施方式、附图以及权利要求,其他特征和方面将是明显的。

技术特征:

1.一种晶圆片级芯片规模封装,包括:

2.根据权利要求1所述的晶圆片级芯片规模封装,其中,所述第一厚度小于60μm,并且所述第二厚度在10μm至60μm的范围内,并且所述第三厚度在10μm至100μm的范围内。

3.根据权利要求1所述的晶圆片级芯片规模封装,其中,所述前金属层和所述后金属层包括铜(cu)。

4.根据权利要求1所述的晶圆片级芯片规模封装,还包括:

5.根据权利要求1所述的晶圆片级芯片规模封装,其中,所述前金属层形成在除了所述输入-输出垫之外的所述半导体衬底上。

6.根据权利要求4所述的晶圆片级芯片规模封装,其中,所述前金属层和所述聚酰亚胺层被构造成在将所述晶圆片级芯片规模封装安装在印刷电路板(pcb)基板上的工艺中抵消所述后金属层的翘曲。

7.根据权利要求4所述的晶圆片级芯片规模封装,其中,所述前金属层和所述后金属层由具有相同热膨胀系数的相同金属形成。

8.根据权利要求1所述的晶圆片级芯片规模封装,其中,所述金属凸块包括可焊接金属层。

9.一种晶圆片级芯片规模封装,包括:

10.根据权利要求9所述的晶圆片级芯片规模封装,其中,所述第一厚度大于所述第二厚度,并且所述第二厚度大于所述第三厚度。

11.一种晶圆片级芯片规模封装的制造方法,所述方法包括:

12.根据权利要求11所述的晶圆片级芯片规模封装的制造方法,其中,所述前金属层的所述第二厚度最薄,并且所述后金属层的所述第三厚度最厚。

13.根据权利要求11所述的晶圆片级芯片规模封装的制造方法,其中,所述第一厚度小于60μm,并且所述第二厚度在10μm至60μm的范围内,并且所述第三厚度在10μm至100μm的范围内。

14.根据权利要求11所述的晶圆片级芯片规模封装的制造方法,其中,所述前金属层和所述聚酰亚胺层被构造成抵消所述后金属层的翘曲,使得安装在印刷电路板(pcb)基板上的所述晶圆片级芯片规模封装保持平衡状态。

15.根据权利要求11所述的晶圆片级芯片规模封装的制造方法,还包括:

技术总结

公开了功率半导体的晶圆片级芯片规模封装及其制造方法。晶圆片级芯片规模封装包括:具有第一厚度的半导体衬底;形成在半导体衬底上的输入‑输出垫;形成在输入‑输出垫上的具有第二厚度的前金属层;形成在半导体衬底的底部上的具有第三厚度的后金属层;以及形成在半导体衬底上的金属凸块。

技术研发人员:朴命镐,朴喜津,金范洙

受保护的技术使用者:美格纳半导体有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!