具有栅保护功能的SiCMOSFET及制备方法

具有栅保护功能的sic mosfet及制备方法

技术领域

1.本发明属于半导体器件技术领域,具体涉及一种具有栅保护功能的sic mosfet,本发明还涉及具有栅保护功能的sic mosfet的制备方法。

背景技术:

2.sic mosfet具有导通损耗低、阻断电压高、开关速度快、工作频率高等特点,在轨道交通、电动汽车、新能源发电等领域有非常大的应用前景。sic mosfet工作于高压与高频状态时,线路存在的杂散电感在高频工作状态下所产生的电压尖峰容易超过sic mosfet的栅源击穿电压,使栅氧化层击穿导致sic mosfet失效。为了对sic mosfet进行保护,往往需要在sic mosfet使用时设置复杂的保护电路,避免电压尖峰击穿栅氧化层,以保障sic mosfet的安全运行。保护电路虽然能够降低sic mosfet栅源失效风险,但是却增加了系统的体积与复杂度,升高了sic mosfet的使用成本。

技术实现要素:

3.本发明的目的是提供一种具有栅保护功能的sic mosfet,解决了现有技术中存在的sic mosfet栅极容易损坏、制作成本高、体积大的问题。

4.本发明所采用的第一技术方案是,具有栅保护功能的sic mosfet,包括n

+

衬底,n

+

衬底其中一侧表面向上制作有n+缓冲层,n+缓冲层上制作有凸台,n+缓冲层表面向上制作有n-漂移区,n-漂移区表面向上均匀制作有若干个p基区、p阱区,p基区的上表面制作有n+源区,p阱区的上表面均匀制作有若干个n+结区,p基区与p阱区之间以及p基区与p基区之间制作有n型电阻调制区,n-漂移区表面向上还制作有p+结区,p基区以及n+源区靠近电阻调制区一侧区域的上表面以及电阻调制区的上表面覆盖有栅氧化层,栅氧化层的上方覆盖有多晶硅栅,n+源区靠近p+结区一侧上表面、p+结区上表面、n+结区中心区域上表面均覆盖有正面欧姆接触金属,栅氧化层与多晶硅栅侧壁、多晶硅栅上表面、正面欧姆接触金属侧壁以及正面欧姆接触金属上表面边缘均覆盖有隔离氧化层,n+源区靠近p+结区一侧上表面、p+结区上表面覆盖的正面欧姆接触金属的上表面覆盖有源电极金属,位于p阱区上表面边缘的n+结区上表面覆盖的正面欧姆接触金属的上表面覆盖有源电极金属,位于p阱区上表面中心的n+结区上表面覆盖的正面欧姆接触金属的上表面覆盖有栅电极金属,n

+

衬底的下表面依次覆盖有背面欧姆接触金属、漏电极金属。

5.本发明第一技术方案的特点还在于,

6.n

+

衬底材料为4h-sic,n

+

衬底厚度为150~350μm,施主杂质浓度为1.0

×

10

18

cm-3

~2.0

×

10

19

cm-3

;n+缓冲层最高上表面与下表面的厚度为0.5~2.0μm,杂质浓度为1.0

×

10

18

cm-3

~1.0

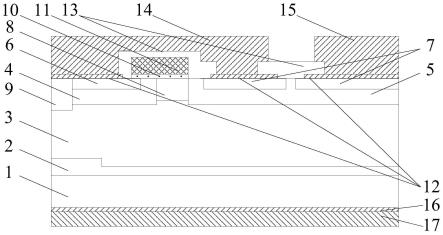

×

10

19

cm-3

,凸台高度为0.3~1.0μm,凸台宽度为1.0~10.0μm;n-漂移区厚度为2.0~60μm,n-漂移区杂质浓度为1.0

×

10

13

cm-3

~1.0

×

10

17

cm-3

;p基区结深为0.4μm~1.0μm,杂质浓度为1.0

×

10

16

cm-3

~5.0

×

10

17

cm-3

;p阱区结深为0.4μm~1.0μm,杂质浓度为1.0

×

10

16

cm-3

~5.0

×

10

17

cm-3

;n+源区结深为0.1μm~0.3μm,杂质浓度为1.0

×

10

18

cm-3

~5.0

×

10

19

cm-3

;n+结区结深为0.1μm~0.3μm,杂质浓度为1.0

×

10

18

cm-3

~5.0

×

10

19

cm-3

;n型电阻调制区结深为0.4μm~0.9μm,杂质浓度为1.0

×

10

15

cm-3

~1.0

×

10

17

cm-3

。

7.p+结区嵌于所述n-漂移区的上表面,且被所述p基区、n+源区包围,p+结区的结深为0.5μm~1.1μm,杂质浓度为1.0

×

10

18

cm-3

~2.0

×

10

19

cm-3

,p+结区的下表面低于p基区的下表面,p+结区中心向下与n+缓冲层上表面的凸台中心呈正对关系。

8.栅氧化层的材料为sio2,厚度为25nm~100nm;多晶硅栅的厚度为100nm~600nm;正面欧姆接触金属与n+源区、p+结区、n+结区之间的电学性质均为欧姆接触性质,正面欧姆接触金属由ti、ni、w、al中的一种或多种的组合形成,正面欧姆接触金属厚度为100nm~300nm;隔离氧化层的材质为sio2,厚度为200nm~2000nm;源电极金属的材质为w、al、cu、au中的一种或多种的组合,厚度为8.0μm~20μm;栅电极金属的材质为w、al、cu、au中的一种或多种的组合,厚度为8.0μm~20μm;背面欧姆接触金属由ti、ni、w、au中的一种或多种的组合形成,厚度为100nm~300nm;漏电极金属的材质为ni、ag、au中的一种或多种的组合,厚度为1.0μm~5.0μm。

9.本发明所采用的第二技术方案是,具有栅保护功能的sic mosfet的制备方法,具体按照以下步骤实施:

10.步骤1、通过物理气相传输pvt法制备n+衬底,如图6所示;

11.步骤2、通过化学气相淀积cvd法在衬底表面向上外延制备n+缓冲层;

12.步骤3、通过光刻加干法刻蚀工艺刻蚀n+缓冲层使n+缓冲层上表面呈凸台状;

13.步骤4、通过化学气相淀积cvd法在n+缓冲层表面向上外延制备n-漂移区3;

14.步骤5、通过铝离子注入在n-漂移区上表面同时制作p基区与p阱区;

15.步骤6、通过氮离子注入在p基区与p阱区上表面同时制作n+源区与n+结区;

16.步骤7、通过氮离子注入在p基区与p阱区之间的n-漂移区上表面,以及p基区与p基区之间的n-漂移区上表面制备n型电阻调制区;

17.步骤8、通过铝离子注入在n+源区之间,n-漂移区、p基区的上表面制备p+结区;

18.步骤9、通过高温退火与牺牲氧化的工艺方法对p基区、p阱区、n+源区、n+结区、电阻调制区、p+结区进行激活;

19.步骤10、通过高温氧化加氮钝化的工艺方法在p基区、p阱区、n+源区、n+结区、电阻调制区、p+结区上表面制备栅氧化层;

20.步骤11、通过cvd的方法在栅氧化层上表面淀积多晶硅栅;

21.步骤12、通过光刻加干法刻蚀的方法刻蚀多晶硅栅与栅氧化层,使p基区的上表面、n+源区靠近电阻调制区一侧区域的上表面、电阻调制区的上表面保留有多晶硅栅与栅氧化层;

22.步骤13、通过真空蒸镀与快速热退火的方法在n+源区靠近p+结区一侧上表面、p+结区上表面、n+结区中心区域上表面制备正面欧姆接触金属;

23.步骤14、通过cvd的方法在器件正面上方制作隔离氧化层;

24.步骤15、通过光刻与干法刻蚀的方法刻蚀隔离氧化层,使栅氧化层与多晶硅栅侧壁、多晶硅栅上表面、正面欧姆接触金属侧壁、正面欧姆接触金属上表面边缘保留有隔离氧化层;

25.步骤16、通过真空蒸镀与湿法刻蚀的方法制备源电极金属14与栅电极金属;

26.步骤17、通过衬底减薄工艺减薄衬底的厚度,通过真空蒸镀与激光退火方法在衬底下表面制作背面欧姆接触金属;

27.步骤18、通过真空蒸镀的方法在背面欧姆接触金属下表面制作漏电极金属;

28.步骤19、通过打点、划片、封装实现具有栅保护功能的sic mosfet的制备。

29.本发明第二技术方案的特点还在于,

30.步骤1中物理气相传输pvt法的温度为2100℃~2200℃,压强为0.5pa~1.5pa,氩气气体流量为100sccm~500sccm;

31.步骤2中化学气相淀积cvd法的淀积温度为1500℃~1600℃;步骤4中化学气相淀积cvd法的淀积温度为1500℃~1600℃;步骤11中化学气相淀积cvd的方法在栅氧化层10上表面淀积多晶硅栅11的温度为室温~550℃;步骤14中cvd法的温度为室温~350℃;

32.步骤3中干法刻蚀工艺的气氛为cf4与sf6,压强范围为1.0pa~10pa;步骤12中干法刻蚀的方法刻蚀多晶硅栅的气氛为cf4,压强范围为1.0pa~5.0pa;步骤15干法刻蚀法的气氛为cf4,压强范围为1.0pa~5.0pa;

33.步骤5中铝离子注入的最高能量为400kev~500kev;步骤6中氮离子注入的最高能量为200kev~300kev;步骤7中氮离子注入的最高能量为350kev~450kev;步骤8中铝离子注入的最高能量为450kev~550kev。

34.步骤9中高温退火的温度为1700℃~1850℃;步骤10中高温氧化加氮钝化的温度为1200℃~1350℃;步骤13中真空蒸镀的本底真空为5

×

10-5

pa~5

×

10-4

pa,快速热退火的温度为950℃~1050℃;步骤16中真空蒸镀的本底真空为5

×

10-5

pa~5

×

10-4

pa;步骤17中真空蒸镀的本底真空为5

×

10-5

pa~5

×

10-4

pa;步骤18中真空蒸镀的本底真空为5

×

10-5

pa~5

×

10-4

pa。

35.本发明的有益效果是,1)通过设置p阱区5上表面的n+结区7、设置位于p阱区5上表面边缘的n+结区7与位于p阱区5上表面中心的n+结区7分别经正面欧姆接触金属12连接至源电极金属14与栅电极金属15,本发明一种具有栅保护功能的sic mosfet在栅极出现电压尖峰时由n+结区7将尖峰电压钳位在安全范围,避免了栅氧化层的击穿失效,改善了传统sic mosfet的栅极可靠性;2)通过隔离氧化层13凹凸闭合形状与倒“中”形状的设置,本发明一种具有栅保护功能的sic mosfet在栅极保护效果较传统sic mosfet更优;3)通过凸台状n+缓冲层2、p+结区9的下表面低于p基区4的下表面、p+结区9中心向下与凸台状n+缓冲层2上表面的凸台中心呈正对关系的设置,本发明一种具有栅保护功能的sic mosfet在雪崩状态时由凸台状n+缓冲层2与p+结区9对峰值电场进行限位,降低了栅氧化层的电场强度,改善了传统sic mosfet栅极的可靠性;4)通过设置厚度为8.0μm~20μm的源电极金属14与栅电极金属15,本发明一种具有栅保护功能的sic mosfet降低了栅氧化层的应力,改善了传统sic mosfet栅极可靠性。

附图说明

36.图1是本发明一种具有栅保护功能的sic mosfet实施例1的aa’截取线剖面结构示意图;

37.图2是本发明一种具有栅保护功能的sic mosfet实施例1的bb’截取线剖面结构示意图;

38.图3是本发明一种具有栅保护功能的sic mosfet实施例1的cc’截取线剖面结构示意图;

39.图4是本发明一种具有栅保护功能的sic mosfet实施例1的俯视结构示意图;

40.图5是本发明一种具有栅保护功能的sic mosfet实施例2的俯视结构示意图;

41.图6是本发明实施例1中n

+

衬底1的剖面结构示意图;

42.图7是本发明实施例1中制备n

+

缓冲层2的剖面结构示意图;

43.图8是本发明实施例1中刻蚀n

+

缓冲层2的剖面结构示意图;

44.图9是本发明实施例1中制备n-漂移区3的剖面结构示意图;

45.图10是本发明实施例1中制备p基区4与p阱区5的剖面结构示意图;

46.图11是本发明实施例1中制备n+源区6与n+结区7的剖面结构示意图;

47.图12是本发明实施例1中制备电阻调制区8的剖面结构示意图;

48.图13是本发明实施例1中制备p+结区9的剖面结构示意图;

49.图14是本发明实施例1中制备栅氧化层10的剖面结构示意图;

50.图15是本发明实施例1中制备多晶硅栅11的剖面结构示意图;

51.图16是本发明实施例1中刻蚀多晶硅栅11与栅氧化层10的剖面结构示意图;

52.图17是本发明实施例1中制备正面欧姆接触金属12的剖面结构示意图;

53.图18是本发明实施例1中制备隔离氧化层13的剖面结构示意图;

54.图19是本发明实施例1中刻蚀隔离氧化层13的剖面结构示意图;

55.图20是本发明实施例1中制备源电极金属14与栅电极金属15的剖面结构示意图;

56.图21是本发明实施例1中制备背面欧姆接触金属16的剖面结构示意图;

57.图22是本发明实施例1中制备漏电极金属17的剖面结构示意图;

58.图23为本发明实施例1中的一种具有栅保护功能的sic mosfet的栅源击穿特性曲线;

59.图中,1.n+衬底,2.n+缓冲层,3.n-漂移区,4.p基区,5.p阱区,6.n+源区,7.n+结区,8.电阻调制区,9.p+结区,10.栅氧化层,11.多晶硅栅,12.正面欧姆接触金属,13.隔离氧化层,14.源电极金属,15.栅电极金属,16.背面欧姆接触金属,17.漏电极金属。

具体实施方式

60.下面结合附图和具体实施方式对本发明进行详细说明。

61.具有栅保护功能的sic mosfet,结构如图1所示,包括n

+

衬底1,n

+

衬底1其中一侧表面向上制作有n+缓冲层2,n+缓冲层2上制作有凸台,n+缓冲层2表面向上制作有n-漂移区3,n-漂移区3表面向上均匀制作有若干个p基区4、p阱区5,p基区4的上表面制作有n+源区6,p阱区5的上表面均匀制作有若干个n+结区7,p基区4与p阱区5之间以及p基区4与p基区4之间制作有n型电阻调制区8,n-漂移区3表面向上还制作有p+结区9,p基区4以及n+源区6靠近电阻调制区8一侧区域的上表面以及电阻调制区8的上表面覆盖有栅氧化层10,栅氧化层10的上方覆盖有多晶硅栅11,n+源区6靠近p+结区9一侧上表面、p+结区9上表面、n+结区7中心区域上表面均覆盖有正面欧姆接触金属12,栅氧化层10与多晶硅栅11侧壁、多晶硅栅11上表面、正面欧姆接触金属12侧壁以及正面欧姆接触金属12上表面边缘均覆盖有隔离氧化层13,n+源区6靠近p+结区9一侧上表面、p+结区9上表面覆盖的正面欧姆接触金属12的上表面

覆盖有源电极金属14,位于p阱区5表面边缘的n+结区7上表面覆盖的正面欧姆接触金属12的上表面覆盖有源电极金属14,位于p阱区5上表面中心的n+结区7上表面覆盖的正面欧姆接触金属12的上表面覆盖有栅电极金属15,n

+

衬底1的下表面依次覆盖有背面欧姆接触金属16、漏电极金属17。

62.n

+

衬底1材料为4h-sic,n

+

衬底1厚度为150~350μm,施主杂质浓度为1.0

×

10

18

cm-3

~2.0

×

10

19

cm-3

;n+缓冲层2最高上表面与下表面的厚度为0.5~2.0μm,杂质浓度为1.0

×

10

18

cm-3

~1.0

×

10

19

cm-3

,凸台高度为0.3~1.0μm,凸台宽度为1.0~10.0μm;n-漂移区3厚度为2.0~60μm,n-漂移区3杂质浓度为1.0

×

10

13

cm-3

~1.0

×

10

17

cm-3

;p基区4结深为0.4μm~1.0μm,杂质浓度为1.0

×

10

16

cm-3

~5.0

×

10

17

cm-3

;p阱区5结深为0.4μm~1.0μm,杂质浓度为1.0

×

10

16

cm-3

~5.0

×

10

17

cm-3

;n+源区6结深为0.1μm~0.3μm,杂质浓度为1.0

×

10

18

cm-3

~5.0

×

10

19

cm-3

;n+结区7结深为0.1μm~0.3μm,杂质浓度为1.0

×

10

18

cm-3

~5.0

×

10

19

cm-3

;n型电阻调制区8结深为0.4μm~0.9μm,杂质浓度为1.0

×

10

15

cm-3

~1.0

×

10

17

cm-3

。

63.p+结区9嵌于所述n-漂移区3的上表面,且被所述p基区4、n+源区6包围,p+结区9的结深为0.5μm~1.1μm,杂质浓度为1.0

×

10

18

cm-3

~2.0

×

10

19

cm-3

,p+结区9的下表面低于p基区4的下表面,p+结区9中心向下与n+缓冲层2上表面的凸台中心呈正对关系。

64.栅氧化层10的材料为sio2,厚度为25nm~100nm;多晶硅栅11的厚度为100nm~600nm;正面欧姆接触金属12与n+源区6、p+结区9、n+结区7之间的电学性质均为欧姆接触性质,正面欧姆接触金属12由ti、ni、w、al中的一种或多种的组合形成,正面欧姆接触金属12厚度为100nm~300nm;隔离氧化层13的材质为sio2,厚度为200nm~2000nm;源电极金属14的材质为w、al、cu、au中的一种或多种的组合,厚度为8.0μm~20μm;栅电极金属15的材质为w、al、cu、au中的一种或多种的组合,厚度为8.0μm~20μm;背面欧姆接触金属16由ti、ni、w、au中的一种或多种的组合形成,厚度为100nm~300nm;漏电极金属17的材质为ni、ag、au中的一种或多种的组合,厚度为1.0μm~5.0μm。

65.具有栅保护功能的sic mosfet的制备方法,具体按照以下步骤实施:

66.步骤1、通过物理气相传输pvt法制备n+衬底1;步骤1中物理气相传输pvt法的温度为2100℃~2200℃,压强为0.5pa~1.5pa,氩气气体流量为100sccm~500sccm;

67.步骤2、通过化学气相淀积cvd法在衬底1表面向上外延制备n+缓冲层2;步骤2中化学气相淀积cvd法的淀积温度为1500℃~1600℃;步骤4中化学气相淀积cvd法的淀积温度为1500℃~1600℃;

68.步骤3、通过光刻加干法刻蚀工艺刻蚀n+缓冲层2使n+缓冲层2上表面呈凸台状;步骤3中干法刻蚀工艺的气氛为cf4与sf6,压强范围为1.0pa~10pa;

69.步骤4、通过化学气相淀积cvd法在n+缓冲层2表面向上外延制备n-漂移区3;

70.步骤5、通过铝离子注入在n-漂移区3上表面同时制作p基区4与p阱区5;步骤5中铝离子注入的最高能量为400kev~500kev;

71.步骤6、通过氮离子注入在p基区4与p阱区5上表面同时制作n+源区6与n+结区7;步骤6中氮离子注入的最高能量为200kev~300kev;

72.步骤7、通过氮离子注入在p基区4与p阱区5之间的n-漂移区3上表面,以及p基区4与p基区4之间的n-漂移区3上表面制备n型电阻调制区8;步骤7中氮离子注入的最高能量为350kev~450kev;

73.步骤8、通过铝离子注入在n+源区6之间,n-漂移区3、p基区4的上表面制备p+结区9;步骤8中铝离子注入的最高能量为450kev~550kev。

74.步骤9、通过高温退火与牺牲氧化的工艺方法对p基区4、p阱区5、n+源区6、n+结区7、电阻调制区8、p+结区9进行激活;步骤9中高温退火的温度为1700℃~1850℃;

75.步骤10、通过高温氧化加氮钝化的工艺方法在p基区4、p阱区5、n+源区6、n+结区7、电阻调制区8、p+结区9上表面制备栅氧化层10;步骤10中高温氧化加氮钝化的温度为1200℃~1350℃;

76.步骤11、通过cvd的方法在栅氧化层10上表面淀积多晶硅栅11;步骤11中化学气相淀积cvd的方法在栅氧化层10上表面淀积多晶硅栅11的温度为室温~550℃;

77.步骤12、通过光刻加干法刻蚀的方法刻蚀多晶硅栅11与栅氧化层10,使p基区4的上表面、n+源区6靠近电阻调制区8一侧区域的上表面、电阻调制区8的上表面保留有多晶硅栅11与栅氧化层10;步骤12中干法刻蚀的方法刻蚀多晶硅栅的气氛为cf4,压强范围为1.0pa~5.0pa;

78.步骤13、通过真空蒸镀与快速热退火的方法在n+源区6靠近p+结区9一侧上表面、p+结区9上表面、n+结区7中心区域上表面制备正面欧姆接触金属12;步骤13中真空蒸镀的本底真空为5

×

10-5

pa~5

×

10-4

pa,快速热退火的温度为950℃~1050℃;

79.步骤14、通过cvd的方法在器件正面上方制作隔离氧化层13;步骤14中cvd法的温度为室温~350℃;

80.步骤15、通过光刻与干法刻蚀的方法刻蚀隔离氧化层13,使栅氧化层10与多晶硅栅11侧壁、多晶硅栅11上表面、正面欧姆接触金属13侧壁、正面欧姆接触金属12上表面边缘保留有隔离氧化层13;步骤15干法刻蚀法的气氛为cf4,压强范围为1.0pa~5.0pa;

81.步骤16、通过真空蒸镀与湿法刻蚀的方法制备源电极金属(14)与栅电极金属15;步骤16中真空蒸镀的本底真空为5

×

10-5

pa~5

×

10-4

pa;

82.步骤17、通过衬底减薄工艺减薄衬底1的厚度,通过真空蒸镀与激光退火方法在衬底1下表面制作背面欧姆接触金属16;步骤17中真空蒸镀的本底真空为5

×

10-5

pa~5

×

10-4

pa;

83.步骤18、通过真空蒸镀的方法在背面欧姆接触金属16下表面制作漏电极金属17;步骤18中真空蒸镀的本底真空为5

×

10-5

pa~5

×

10-4

pa。

84.步骤19、通过打点、划片、封装实现具有栅保护功能的sic mosfet的制备。

85.实施例1

86.如图1,本发明一种具有栅保护功能的sic mosfet,包括材料为n+衬底1,厚度为150μm,施主杂质浓度为1.0

×

10

18

cm-3

;n+衬底1表面向上制作有凸台状n+缓冲层2,最高上表面与下表面的厚度为1.0μm,杂质浓度为1.0

×

10

18

cm-3

,凸台高度为0.5μm,凸台宽度为10.0μm;凸台状n+缓冲层2表面向上制作有n-漂移区3,厚度11μm,杂质浓度为1.0

×

10

16

cm-3

。嵌于n-漂移区3上表面的p基区4,结深为0.8μm,杂质浓度为1.0

×

10

17

cm-3

;嵌于n-漂移区3上表面的p阱区5,结深为0.8μm,杂质浓度为1.0

×

10

17

cm-3

;嵌于p基区4上表面的n+源区6,结深为0.2μm,杂质浓度为2.0

×

10

18

cm-3

;嵌于p阱区5上表面的n+结区7,结深为0.2μm,杂质浓度为2.0

×

10

18

cm-3

;如图1、图2,嵌于n-漂移区3上表面,位于p基区4与p阱区5之间以及p基区4与p基区4之间的n型电阻调制区8,结深为0.7μm,杂质浓度为5.0

×

10

16

cm-3

;如图2,嵌

于n-漂移区3、p基区4上表面,被p基区4、n+源区6包围的p+结区9,结深为1.1μm,杂质浓度为2.0

×

10

18

cm-3

,p+结区9中心向下与凸台状n+缓冲层2上表面的凸台中心呈正对关系。p基区4的上表面、n+源区6靠近电阻调制区8一侧区域的上表面、电阻调制区8的上表面覆盖有栅氧化层10,栅氧化层10的材料为sio2,厚度为55nm;栅氧化层10的上方覆盖有多晶硅栅11,多晶硅栅11的厚度为500nm;n+源区6靠近p+结区9一侧上表面、p+结区9上表面、n+结区7中心区域上表面覆盖有正面欧姆接触金属12,正面欧姆接触金属12与n+源区6、p+结区9、n+结区7之间的电学性质均为欧姆接触性质,正面欧姆接触金属12由ti、ni的组合形成,厚度为200nm;栅氧化层10与多晶硅栅11侧壁、多晶硅栅11上表面、正面欧姆接触金属12侧壁、正面欧姆接触金属12上表面边缘覆盖有隔离氧化层13,隔离氧化层13的材质为sio2,厚度为2000nm;n+源区6靠近p+结区9一侧上表面、p+结区9上表面覆盖的正面欧姆接触金属12的上表面覆盖有源电极金属14,位于p阱区5上表面边缘的n+结区7上表面覆盖的正面欧姆接触金属12的上表面覆盖有源电极金属14,源电极金属14的材质为al,厚度为10μm;如图3,位于p阱区5上表面中心的n+结区7上表面覆盖的正面欧姆接触金属12的上表面覆盖有栅电极金属15,栅电极金属15的材质为al,厚度为10μm;n+衬底1的下表面覆盖有背面欧姆接触金属16,背面欧姆接触金属16由ti、ni、w的组合形成,厚度为200nm;背面欧姆接触金属16下表面覆盖有漏电极金属17,漏电极金属17的材质为ag,厚度为1.0μm。

87.如图6-图22,本发明一种具有栅保护功能的sic mosfet的制备方法,按照以下步骤实施:

88.通过物理气相传输(pvt)法制备厚度为350μm的n+衬底1,温度为2100℃,压强为0.5pa,氩气气体流量为100sccm,如图6所示;

89.通过化学气相淀积(cvd)法在衬底1表面向上外延制备n+缓冲层2,温度为1500℃,如图7所示;

90.通过光刻加干法刻蚀工艺刻蚀n+缓冲层2使n+缓冲层2上表面呈凸台状,气氛为cf4,压强为1.0pa,如图8所示;

91.通过cvd法在n+缓冲层2表面向上外延制备n-漂移区3,温度为1500℃,如图9所示;

92.通过铝离子注入在n-漂移区3上表面同时制作p基区4与p阱区5,铝离子注入的最高能量为400kev,如图10所示;

93.通过氮离子注入在p基区4与p阱区5上表面同时制作n+源区6与n+结区7,氮离子注入的最高能量为200kev,如图11所示;

94.通过氮离子注入在p基区4与p阱区5之间的n-漂移区3上表面,以及p基区4与p基区4之间的n-漂移区3上表面制备n型电阻调制区8,氮离子注入的最高能量为350kev,如图12所示;

95.通过铝离子注入在n+源区6之间,n-漂移区3、p基区4的上表面制备p+结区9,铝离子注入的最高能量为450kev,如图13所示;

96.通过1700℃高温退火与牺牲氧化的工艺方法对p基区4,p阱区5,n+源区6,n+结区7,电阻调制区8,p+结区9进行激活;

97.通过1200℃高温氧化加氮钝化的工艺方法在p基区4、p阱区5、n+源区6、n+结区7、电阻调制区8、p+结区9上表面制备栅氧化层10,如图14所示;

98.通过室温cvd的方法在栅氧化层10上表面淀积多晶硅栅11,如图15所示;

99.通过光刻加干法刻蚀的方法刻蚀多晶硅栅11与栅氧化层10,使p基区4的上表面、n+源区6靠近电阻调制区8一侧区域的上表面、电阻调制区8的上表面保留有多晶硅栅11与栅氧化层10,干法刻蚀气氛为cf4,压强为1.0pa,如图16所示;

100.通过真空蒸镀与950℃快速热退火的方法在n+源区6靠近p+结区9一侧上表面、p+结区9上表面、n+结区7中心区域上表面制备正面欧姆接触金属12,真空蒸镀的本底真空为5

×

10-5

pa,如图17所示;

101.通过室温cvd的方法在器件正面上方制作隔离氧化层13,如图18所示;

102.通过光刻与干法刻蚀的方法刻蚀隔离氧化层13,使栅氧化层10与多晶硅栅11侧壁、多晶硅栅11上表面、正面欧姆接触金属12侧壁、正面欧姆接触金属12上表面边缘保留有隔离氧化层13,干法刻蚀气氛为cf4,压强为1.0pa,如图19所示;

103.通过真空蒸镀与湿法刻蚀的方法制备源电极金属14与栅电极金属15,真空蒸镀的本底真空为5

×

10-5

pa,如图20所示;

104.通过衬底减薄工艺减薄衬底1的厚度至150μm,通过真空蒸镀与激光退火方法在衬底1下表面制作背面欧姆接触金属16,真空蒸镀的本底真空为5

×

10-5

pa,如图21所示;

105.通过真空蒸镀的方法在背面欧姆接触金属16下表面制作漏电极金属17,真空蒸镀的本底真空为5

×

10-5

pa,如图22所示;

106.通过打点、划片、封装实现具有栅保护功能的sic mosfet的制备;

107.完成制备的具有栅保护功能的sic mosfet的俯视结构示意图如图4所示,俯视角度隔离氧化层13将源电极金属14与栅电极金属15隔开,隔离氧化层13呈凹凸闭合形状使源电极金属14与栅电极金属15交错排列。

108.实施例2

109.如图1,本发明一种具有栅保护功能的sic mosfet的结构是,包括材料为n+衬底1,厚度为200μm,施主杂质浓度为1.0

×

10

19

cm-3

;n+衬底1表面向上制作有凸台状n+缓冲层2,最高上表面与下表面的厚度为2.0μm,杂质浓度为2.0

×

10

18

cm-3

,凸台高度为1.0μm,凸台宽度为1.0μm;凸台状n+缓冲层2表面向上制作有n-漂移区3,厚度30μm,杂质浓度为1.0

×

10

15

cm-3

。嵌于n-漂移区3上表面的p基区4,结深为1.0μm,杂质浓度为1.0

×

10

17

cm-3

;嵌于n-漂移区3上表面的p阱区5,结深为1.0μm,杂质浓度为1.0

×

10

17

cm-3

;嵌于p基区4上表面的n+源区6,结深为0.3μm,杂质浓度为2.0

×

10

18

cm-3

;嵌于p阱区5上表面的n+结区7,结深为0.3μm,杂质浓度为2.0

×

10

18

cm-3

;如图1、图2,嵌于n-漂移区3上表面,位于p基区4与p阱区5之间以及p基区4与p基区4之间的n型电阻调制区8,结深为0.8μm,杂质浓度为1.0

×

10

16

cm-3

;如图2,嵌于n-漂移区3、p基区4上表面,被p基区4、n+源区6包围的p+结区9,结深为1.1μm,杂质浓度为1.0

×

10

18

cm-3

,p+结区9中心向下与凸台状n+缓冲层2上表面的凸台中心呈正对关系。p基区4的上表面、n+源区6靠近电阻调制区8一侧区域的上表面、电阻调制区8的上表面覆盖有栅氧化层10,栅氧化层10的材料为sio2,厚度为80nm;栅氧化层10的上方覆盖有多晶硅栅11,多晶硅栅11的厚度为600nm;n+源区6靠近p+结区9一侧上表面、p+结区9上表面、n+结区7中心区域上表面覆盖有正面欧姆接触金属12,正面欧姆接触金属12与n+源区6、p+结区9、n+结区7之间的电学性质均为欧姆接触性质,正面欧姆接触金属12由ti、ni的组合形成,厚度为100nm;栅氧化层10与多晶硅栅11侧壁、多晶硅栅11上表面、正面欧姆接触金属12侧壁、正面欧姆接触金属12上表面边缘覆盖有隔离氧化层13,隔离氧化层13的材质为sio2,

厚度为1000nm;n+源区6靠近p+结区9一侧上表面、p+结区9上表面覆盖的正面欧姆接触金属12的上表面覆盖有源电极金属14,位于p阱区5上表面边缘的n+结区7上表面覆盖的正面欧姆接触金属12的上表面覆盖有源电极金属14,源电极金属14的材质为al,厚度为20μm;如图3,位于p阱区5上表面中心的n+结区7上表面覆盖的正面欧姆接触金属12的上表面覆盖有栅电极金属15,栅电极金属15的材质为cu,厚度为20μm;n+衬底1的下表面覆盖有背面欧姆接触金属16,背面欧姆接触金属16由ti、ni、w的组合形成,厚度为100nm;背面欧姆接触金属16下表面覆盖有漏电极金属17,漏电极金属17的材质为au,厚度为1.0μm。

110.本发明一种具有栅保护功能的sic mosfet的制备方法,按照以下步骤实施:

111.通过物理气相传输(pvt)法制备厚度为350μm的n+衬底1,温度为2200℃,压强为1.5pa,氩气气体流量为500sccm,如图6所示;

112.通过化学气相淀积(cvd)法在衬底1表面向上外延制备n+缓冲层2,淀积温度为1600℃,如图7所示;

113.通过光刻加干法刻蚀工艺刻蚀n+缓冲层2使n+缓冲层2上表面呈凸台状,干法刻蚀工艺的气氛为sf6,压强范围为10pa,如图8所示;

114.通过cvd法在n+缓冲层2表面向上外延制备n-漂移区3,淀积温度为1600℃,如图9所示;

115.通过铝离子注入在n-漂移区3上表面同时制作p基区4与p阱区5,铝离子注入的最高能量为500kev,如图10所示;

116.通过氮离子注入在p基区4与p阱区5上表面同时制作n+源区6与n+结区7,氮离子注入的最高能量为300kev,如图11所示;

117.通过氮离子注入在p基区4与p阱区5之间的n-漂移区3上表面,以及p基区4与p基区4之间的n-漂移区3上表面制备n型电阻调制区8,氮离子注入的最高能量为450kev,如图12所示;

118.通过铝离子注入在n+源区6之间,n-漂移区3、p基区4的上表面制备p+结区9,铝离子注入的最高能量为550kev,如图13所示;

119.通过1850℃高温退火与牺牲氧化的工艺方法对p基区4,p阱区5,n+源区6,n+结区7,电阻调制区8,p+结区9进行激活;

120.通过1350℃高温氧化加氮钝化的工艺方法在p基区4、p阱区5、n+源区6、n+结区7、电阻调制区8、p+结区9上表面制备栅氧化层10,如图14所示;

121.通过550℃cvd的方法在栅氧化层10上表面淀积多晶硅栅11,如图15所示;

122.通过光刻加干法刻蚀的方法刻蚀多晶硅栅11与栅氧化层10,使p基区4的上表面、n+源区6靠近电阻调制区8一侧区域的上表面、电阻调制区8的上表面保留有多晶硅栅11与栅氧化层10,干法刻蚀气氛为cf4,压强为5.0pa,如图16所示;

123.通过真空蒸镀与1050℃快速热退火的方法在n+源区6靠近p+结区9一侧上表面、p+结区9上表面、n+结区7中心区域上表面制备正面欧姆接触金属12,真空蒸镀的本底真空为5

×

10-4

pa,如图17所示;

124.通过350℃cvd的方法在器件正面上方制作隔离氧化层13,如图18所示;

125.通过光刻与干法刻蚀的方法刻蚀隔离氧化层13,使栅氧化层10与多晶硅栅11侧壁、多晶硅栅11上表面、正面欧姆接触金属12侧壁、正面欧姆接触金属12上表面边缘保留有

隔离氧化层13,干法刻蚀的气氛为cf4,压强为5.0pa,如图19所示;

126.通过真空蒸镀与湿法刻蚀的方法制备源电极金属14与栅电极金属15,真空蒸镀的本底真空为5

×

10-4

pa,如图20所示;

127.通过衬底减薄工艺减薄衬底1的厚度至200μm,通过真空蒸镀与激光退火方法在衬底1下表面制作背面欧姆接触金属16,真空蒸镀的本底真空为5

×

10-4

pa,如图21所示;

128.通过真空蒸镀的方法在背面欧姆接触金属16下表面制作漏电极金属17,真空蒸镀的本底真空为5

×

10-4

pa,如图22所示;

129.通过打点、划片、封装实现具有栅保护功能的sic mosfet的制备;

130.完成制备的具有栅保护功能的sic mosfet的俯视结构示意图如图5所示,俯视角度隔离氧化层13将源电极金属14与栅电极金属15隔开,隔离氧化层13呈倒“中”形状,栅电极金属15填充隔离氧化层13呈倒“中”形状内部区域,源电极金属14包围隔离氧化层13呈倒“中”形状外部。

131.实施例3

132.本发明一种具有栅保护功能的sic mosfet的结构是,包括材料为n+衬底1,厚度为180μm,施主杂质浓度为1.5

×

10

18

cm-3

;n+衬底1表面向上制作有凸台状n+缓冲层2,最高上表面与下表面的厚度为1.2μm,杂质浓度为1.5

×

10

18

cm-3

,凸台高度为0.6μm,凸台宽度为11.0μm;凸台状n+缓冲层2表面向上制作有n-漂移区3,厚度15μm,杂质浓度为8.0

×

10

15

cm-3

。嵌于n-漂移区3上表面的p基区4,结深为0.85μm,杂质浓度为1.2

×

10

17

cm-3

;嵌于n-漂移区3上表面的p阱区5,结深为0.85μm,杂质浓度为1.2

×

10

17

cm-3

;嵌于p基区4上表面的n+源区6,结深为0.22μm,杂质浓度为2.5

×

10

18

cm-3

;嵌于p阱区5上表面的n+结区7,结深为0.22μm,杂质浓度为2.5

×

10

18

cm-3

;嵌于n-漂移区3上表面,位于p基区4与p阱区5之间以及p基区4与p基区4之间的n型电阻调制区8,结深为0.75μm,杂质浓度为7.0

×

10

16

cm-3

;嵌于n-漂移区3、p基区4上表面,被p基区4、n+源区6包围的p+结区9,结深为0.95μm,杂质浓度为2.5

×

10

18

cm-3

,p+结区9中心向下与凸台状n+缓冲层2上表面的凸台中心呈正对关系。p基区4的上表面、n+源区6靠近电阻调制区8一侧区域的上表面、电阻调制区8的上表面覆盖有栅氧化层10,栅氧化层10的材料为sio2,厚度为45nm;栅氧化层10的上方覆盖有多晶硅栅11,多晶硅栅11的厚度为600nm;n+源区6靠近p+结区9一侧上表面、p+结区9上表面、n+结区7中心区域上表面覆盖有正面欧姆接触金属12,正面欧姆接触金属12与n+源区6、p+结区9、n+结区7之间的电学性质均为欧姆接触性质,正面欧姆接触金属12由ti、ni的组合形成,厚度为300nm;栅氧化层10与多晶硅栅11侧壁、多晶硅栅11上表面、正面欧姆接触金属12侧壁、正面欧姆接触金属12上表面边缘覆盖有隔离氧化层13,隔离氧化层13的材质为sio2,厚度为2500nm;n+源区6靠近p+结区9一侧上表面、p+结区9上表面覆盖的正面欧姆接触金属12的上表面覆盖有源电极金属14,位于p阱区5上表面边缘的n+结区7上表面覆盖的正面欧姆接触金属12的上表面覆盖有源电极金属14,源电极金属14的材质为al,厚度为6μm;位于p阱区5上表面中心的n+结区7上表面覆盖的正面欧姆接触金属12的上表面覆盖有栅电极金属15,栅电极金属15的材质为al,厚度为6μm;n+衬底1的下表面覆盖有背面欧姆接触金属16,背面欧姆接触金属16由ti、ni、w的组合形成,厚度为300nm;背面欧姆接触金属16下表面覆盖有漏电极金属17,漏电极金属17的材质为ag,厚度为2.0μm。

133.本发明一种具有栅保护功能的sic mosfet的制备方法,按照以下步骤实施:

134.通过物理气相传输(pvt)法制备的n+衬底1,温度为2100℃,压强为0.8pa,氩气气体流量为150sccm;

135.通过化学气相淀积(cvd)法在衬底1表面向上外延制备n+缓冲层2,温度为1550℃;

136.通过光刻加干法刻蚀工艺刻蚀n+缓冲层2使n+缓冲层2上表面呈凸台状,气氛为cf4,压强为1.5pa;

137.通过cvd法在n+缓冲层2表面向上外延制备n-漂移区3,温度为1550℃;

138.通过铝离子注入在n-漂移区3上表面同时制作p基区4与p阱区5,铝离子注入的最高能量为420kev;

139.通过氮离子注入在p基区4与p阱区5上表面同时制作n+源区6与n+结区7,氮离子注入的最高能量为210kev;

140.通过氮离子注入在p基区4与p阱区5之间的n-漂移区3上表面,以及p基区4与p基区4之间的n-漂移区3上表面制备n型电阻调制区8,氮离子注入的最高能量为360kev;

141.通过铝离子注入在n+源区6之间,n-漂移区3、p基区4的上表面制备p+结区9,铝离子注入的最高能量为470kev;

142.通过1780℃高温退火与牺牲氧化的工艺方法对p基区4,p阱区5,n+源区6,n+结区7,电阻调制区8,p+结区9进行激活;

143.通过1250℃高温氧化加氮钝化的工艺方法在p基区4、p阱区5、n+源区6、n+结区7、电阻调制区8、p+结区9上表面制备栅氧化层10;

144.通过室温cvd的方法在栅氧化层10上表面淀积多晶硅栅11;

145.通过光刻加干法刻蚀的方法刻蚀多晶硅栅11与栅氧化层10,使p基区4的上表面、n+源区6靠近电阻调制区8一侧区域的上表面、电阻调制区8的上表面保留有多晶硅栅11与栅氧化层10,干法刻蚀气氛为cf4,压强为2.0pa;

146.通过真空蒸镀与1000℃快速热退火的方法在n+源区6靠近p+结区9一侧上表面、p+结区9上表面、n+结区7中心区域上表面制备正面欧姆接触金属12,真空蒸镀的本底真空为9

×

10-5

pa;

147.通过室温cvd的方法在器件正面上方制作隔离氧化层13;

148.通过光刻与干法刻蚀的方法刻蚀隔离氧化层13,使栅氧化层10与多晶硅栅11侧壁、多晶硅栅11上表面、正面欧姆接触金属12侧壁、正面欧姆接触金属12上表面边缘保留有隔离氧化层13,干法刻蚀气氛为cf4,压强为2.0pa;

149.通过真空蒸镀与湿法刻蚀的方法制备源电极金属14与栅电极金属15,真空蒸镀的本底真空为9

×

10-5

pa;

150.通过衬底减薄工艺减薄衬底1的厚度至180μm,通过真空蒸镀与激光退火方法在衬底1下表面制作背面欧姆接触金属16,真空蒸镀的本底真空为9

×

10-5

pa;

151.通过真空蒸镀的方法在背面欧姆接触金属16下表面制作漏电极金属17,真空蒸镀的本底真空为9

×

10-5

pa;

152.通过打点、划片、封装实现具有栅保护功能的sic mosfet的制备。

153.为了说明本发明一种具有栅保护功能的sic mosfet的优势,通过sentaurus tcad计算机数值实验平台对上述实施例1的具有栅保护功能的sic mosfet进行验证。

154.图23为本发明实施例1中的一种具有栅保护功能的sic mosfet的栅源击穿特性曲

线,从图23中可以看出,随着加载电压的升高,本发明sic mosfet在栅极电压为55v时就不再上升,而常规sic mosfet的栅极电压达到55v之后仍继续上升,一直增加至60v,使栅氧化层发生击穿损坏。综上,本发明一种具有栅保护功能的sic mosfet具有更优的栅保护功能,改善了现有sic mosfet栅氧化层失效率高的问题。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1