一种增强型氮化镓器件结构及其制备方法

本发明涉及半导体器件,具体涉及一种增强型氮化镓器件结构及其制备方法。

背景技术:

1、半导体器件指利用硅、氮化镓等半导体材料所制成的、用来完成特定功能的电子器件,它们的体积小,集成度高,应用范围极为广泛。在通信、交通、医疗、军事等许多领域中,半导体器件都发挥着关键作用,半导体技术已经深入我们生活中的方方面面。随着我国半导体事业飞速发展,对于各种半导体器件的需求越发旺盛,半导体的应用更是已经遍及各个领域。

2、半导体材料的发展至今已经历了三代:作为第一代半导体材料的代表,硅(si)材料凭借成熟的工艺水平与较低的成本已经占据了半导体市场的大部分份额,但由于硅材料本身特性的限制,例如禁带宽度与载流子迁移率等,导致在高压等领域硅基器件并不能得到广泛应用。之后,以砷化镓(gaas)为代表的第二代半导体材料逐渐开始发展,由于具有高电子迁移率,gaas在高频领域的表现较为出色,之后便携式电子产品的发展更加扩大了gaas的市场份额。目前对器件在环境非常恶劣的情况下(例如强电场、强磁、强辐射等环境)的可靠性提出了较高要求。如今高速发展的第三代半导体很好地满足了这一需求。目前,第三代半导体以氮化镓等宽禁带材料为主,凭借大的禁带宽度与高的击穿电场等优异特性成为研究热点。再加上近年来半导体器件在高压大功率场景的广泛应用,使得实现性能优良的增强型氮化镓半导体器件变得空前重要。

3、传统异质结半导体器件所产生的高浓度载流子主要来源于对异质结中的势垒层进行高浓度n型故意掺杂,杂质电离出的电子被异质结交界面的量子势阱限制,只能进行平面移动,从而形成二维电子气。但对于algan/gan(铝镓氮/氮化镓)异质结来讲,由于材料强烈的极化效应,在异质结交界面处不需故意掺杂即可出现高浓度的二维电子气。因此,普通氮化镓器件的导电沟道是常开的,即耗尽型器件。增强型器件不需要额外栅极负电压来关断器件,能显著降低电路关态下的静态功耗与开关损耗。并且由于氮化镓器件在高频与高功率条件下的性能较为出色,故经常被用于频率与输出功率较高的应用环境中,这些环境出于安全和简化驱动器电路等原因,需要常关操作,所以研究制造性能优良可靠的增强型氮化镓器件是十分重要且有意义的。随着器件设计越来越复杂、集成度越来越高,增强型器件的节能、设计简便等优点越来越突出,而现有的实现增强型器件的手段均具有明显缺陷,例如输出电流过小、栅控能力过低、高温环境下不稳定等,这些问题严重地阻碍了器件的实际应用,亟待得到有效的解决。而解决这些问题的方法,是设计出一种能够兼顾较高输出电流、较高阈值电压、较好栅控能力、高温环境下较强稳定性的新型增强型氮化镓器件结构,此问题的突破,可以大力推动氮化镓器件更快更广泛地进入实际应用阶段,促进我国新材料半导体事业的快速发展。

4、目前可以利用氟离子注入技术制备增强型氮化镓器件结构,氟离子注入技术主要利用f基等离子体对栅极下方区域的algan势垒层进行处理。利用离子注入方法,将带有负电荷的f离子进行加速,使之注入异质结的栅极下方区域。进入algan势垒层后,带有负电荷的f离子对下方沟道的二维电子气起到耗尽作用,导致二维电子气沟道连续性被破坏,增强型性能得以实现。

5、但是,在f离子注入工艺过程中,会有部分f离子进入到gan缓冲层,这部分f离子由于散射作用使得沟道载流子迁移率降低;f离子在algan势垒层中存在温度不稳定性,导致温度升高,器件阈值电压负漂现象明显,器件可靠性不理想。

技术实现思路

1、为了解决现有技术中存在的上述问题,本发明提供了一种增强型氮化镓器件结构及其制备方法。本发明要解决的技术问题通过以下技术方案实现:

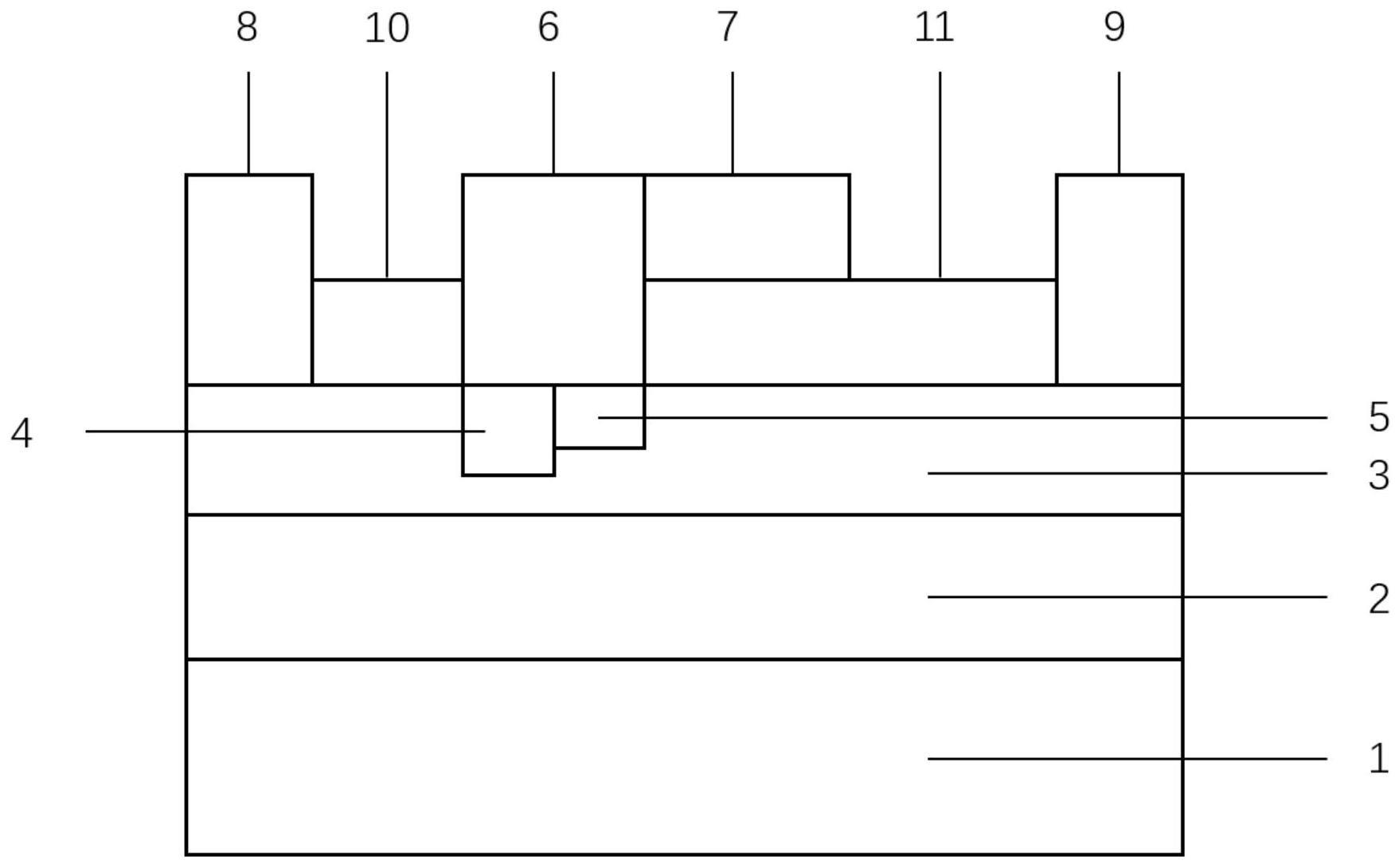

2、本发明的一个实施例提供了一种增强型氮化镓器件结构,所述增强型氮化镓器件结构包括:

3、衬底层;

4、gan缓冲层,位于所述衬底层之上;

5、algan势垒层,位于所述gan缓冲层之上,所述algan势垒层的上表面设置有凹槽结构,所述凹槽结构包括相通的第一凹槽和第二凹槽,且所述第一凹槽的深度大于所述第二凹槽的深度;

6、第一p型氮化镓栅帽层和第二p型氮化镓栅帽层,所述第一p型氮化镓栅帽层设置在所述第一凹槽中,所述第二p型氮化镓栅帽层设置在所述第二凹槽中,且所述第一p型氮化镓栅帽层和所述第二p型氮化镓栅帽层相互接触;

7、栅电极,所述栅电极位于所述第一p型氮化镓栅帽层和所述第二p型氮化镓栅帽层之上;

8、源电极和漏电极,所述源电极和所述漏电极分别位于所述algan势垒层上表面的两端;

9、第一钝化层和第二钝化层,所述第一钝化层和所述第二钝化层位于所述algan势垒层之上,且所述第一钝化层位于所述源电极和所述栅电极之间,所述第二钝化层位于所述漏电极和所述栅电极之间;

10、栅场板,所述栅场板位于所述第二钝化层之上。

11、在本发明的一个实施例中,所述衬底层的材料为硅。

12、在本发明的一个实施例中,所述第一p型氮化镓栅帽层和所述第二p型氮化镓栅帽层的上表面与所述algan势垒层的上表面齐平。

13、在本发明的一个实施例中,所述栅电极、所述源电极、所述漏电极和所述栅场板的上表面齐平,且所述栅电极和所述栅场板相接触,所述栅场板和所述漏电极之间的间距大于零。

14、在本发明的一个实施例中,所述源电极和所述栅电极之间的间距小于所述漏电极和所述栅电极之间的间距。

15、在本发明的一个实施例中,所述第一钝化层的两端分别与所述源电极和所述栅电极接触,所述第二钝化层的两端分别与所述漏电极和所述栅电极接触。

16、在本发明的一个实施例中,所述第一钝化层和所述第二钝化层的材料为sin。

17、在本发明的一个实施例中,所述第一凹槽的宽度等于所述第二凹槽的宽度。

18、在本发明的一个实施例中,所述衬底层的厚度为0.3μm;

19、所述algan势垒层的厚度为0.015μm,所述gan缓冲层的厚度为1.945μm;

20、所述第一凹槽的深度为0.012μm、宽度为0.5μm,所述第二凹槽的深度为0.0095μm、宽度为0.5μm;

21、所述源电极和漏电极之间的间距为4μm,所述漏电极和所述栅电极之间的间距为2μm;

22、所述第一p型氮化镓栅帽层和所述第二p型氮化镓栅帽层的掺杂浓度为1×1018cm-3。

23、本发明一个实施例还提供一种增强型氮化镓器件结构的制备方法,所述制备方法用于制备上述任一项实施例所述的增强型氮化镓器件结构,所述制备方法包括:

24、步骤1、选取衬底层;

25、步骤2、在所述衬底层上生长gan缓冲层;

26、步骤3、在所述gan缓冲层上生长algan势垒层;

27、步骤4、在所述algan势垒层上表面的两端制备源电极和漏电极;

28、步骤5、在所述algan势垒层上表面生长钝化层;

29、步骤6、在栅电极区域对所述钝化层和所述algan势垒层进行刻蚀,形成第一钝化层和第二钝化层、以及包括相通的第一凹槽和第二凹槽的凹槽结构,其中,所述第一凹槽的深度大于所述第二凹槽的深度;

30、步骤7、在所述第一凹槽和所述第二凹槽中同时制备第一p型氮化镓栅帽层和第二p型氮化镓栅帽层;

31、步骤8、在所述第一p型氮化镓栅帽层和所述第二p型氮化镓栅帽层上方制备栅电极,并在所述第二钝化层上方形成栅场板,完成增强型氮化镓器件结构的制备。

32、与现有技术相比,本发明的有益效果在于:

33、本发明通过将p型氮化镓栅帽层处于algan势垒层内部,使栅电极金属与algan势垒层直接接触,显著缩小栅电极金属与二维电子气沟道之间的距离,避免了削弱器件栅控能力的问题。

34、本发明将algan势垒层上的凹槽刻蚀为深浅不一的两部分,从而避免由于刻蚀过度导致的输出电流过小,或由于刻蚀深度不足导致的阈值电压提升不明显的问题,兼顾了器件的优秀输出特性与较高的阈值电压,从而避免在采用凹槽栅技术时,难以控制刻蚀深度,不得不在较高的阈值电压与较可观的输出电流之间进行选择而不能二者同时实现的缺点。

35、本发明仅通过改变器件物理结构来实现增强型器件,较好地保留了氮化镓器件高温稳定性好、载流子迁移率高的特点,避免了采用f离子注入技术时对器件载流子迁移率与热稳定性造成的影响。

36、以下将结合附图及实施例对本发明做进一步详细说明。

- 还没有人留言评论。精彩留言会获得点赞!