高耐量浮游型超结MOS场效应晶体管元胞结构及晶体管的制作方法

本技术涉及mosfet器件,尤其涉及一种高耐量浮游型超结mos场效应晶体管元胞结构及其晶体管。

背景技术:

1、 近年来,节能和减排成为电子信息技术领域的重要发展方向,引领了对高能效和高可靠性的mosfet(metal oxide semiconductor field effect transistor,金属-氧化物半导体场效应管)功率器件的大量需求。

2、 功率mos场效应晶体管器件,即mosfet,其原意是:mos(metal oxidesemiconductor金属氧化物半导体),fet(field effect transistor场效应晶体管),即以金属层(m)的栅极隔着氧化层(o)利用电场的效应来控制半导体(s)的场效应晶体管。

3、为了打破传统功率mos场效应晶体管器件的导通电阻的降低受击穿电压的限制,现有技术中已提出了一种具有超结结构的半导体单元,该超结结构通过连续外延生长的方式来实现减小导通状态电阻并同时保持高击穿电压,发明人对传统的超结mosfet的应用及测试过程中,器件在非嵌位感性负载开关(uis)测试电流路径,传统的超结mosfet的电流路径为:n漂移区→p型基区→n+源极→接触区→表面电极;发明人在实现本实用新型的过程中发现这样的电流路径容易触发器件内部的寄生bjt(寄生晶体管导通),无法有效提高器件的eas耐压(雪崩击穿能量)。

4、有鉴于此,如何解决传统的超结mosfet存在的容易触发器件内部的寄生bjt、无法有效提高器件的eas耐压等问题,便成为本实用新型所要研究解决的课题。

技术实现思路

1、本实用新型的目的是提供一种高耐量浮游型超结mos场效应晶体管元胞结构及其晶体管,其目的是用于解决传统的超结mosfet存在的容易触发器件内部的寄生bjt、无法有效提高器件的eas耐压等问题,该超结mos场效应晶体管有效地避免了器件内部的寄生bjt的触发,提高器件的eas耐压。

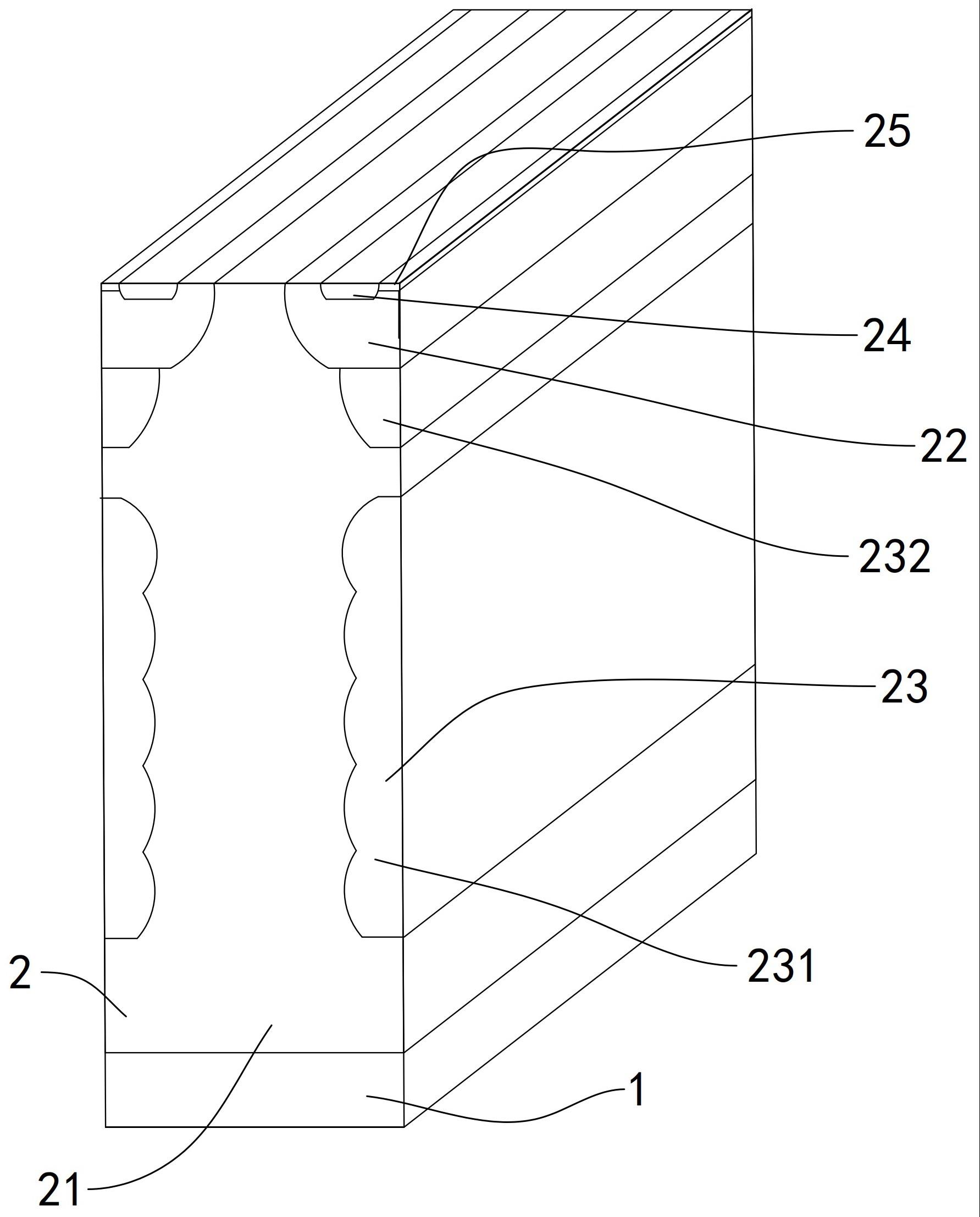

2、 为达到上述目的,在第一方面,本实用新型采用的技术方案是:一种高耐量浮游型超结mos场效应晶体管元胞结构,所述元胞结构包括n型衬底及设于n型衬底上方的多次外延结构;所述多次外延结构包括设于n型衬底上方的n型外延层和设置在所述n型外延层内的p型基区;所述p型基区下方设有多次外延p型柱,所述多次外延p型柱具有位于上段的上外延p型柱以及位于下段的下外延p型柱,所述上外延p型柱浮游于所述下外延p型柱的上方,两者间填充n型外延层,所述上外延p型柱向上延伸入所述p型基区中,从下到上延伸设置的多次外延p型柱的总层数为n层,其中n>3,所述下外延p型柱的层数为x层,其中n>x,其中第y层至第n层为所述上外延p型柱,其中n>=y,y满足公式y= n-x;所述上外延p型柱与所述下外延p型柱之间存在有间隔尺寸d,间隔尺寸d与所述多次外延p型柱中各层的厚度比为7~13:10;所述p型基区的顶部设置有并列的n型源区和p型源区。

3、为达到上述目的,在第二方面,本实用新型采用的技术方案是:所述超结mos场效应晶体管使用如本实用新型第一方面所述的元胞结构。

4、本实用新型的有关内容解释如下:

5、1.本实用新型的上述技术方案的实施,针对传统的超结mosfet的应用及测试中器件在非嵌位感性负载开关(uis)测试的电流路径比较,所发现的传统的超结mosfet存在的容易触发器件内部的寄生bjt、无法有效提高器件的eas耐压等问题,提出了一种高耐量浮游型超结mos场效应晶体管元胞结构及其晶体管,该方案中,所述元胞结构中的所述多次外延p型柱具有位于上段的上外延p型柱以及位于下段的下外延p型柱,所述上外延p型柱浮游于所述下外延p型柱的上方,两者间填充n型外延层,所述上外延p型柱向上延伸入所述p型基区中,从下到上延伸设置的多次外延p型柱的总层数为n层(n>3),所述下外延p型柱的层数为x层(n>x),其中第y层至第n层为所述上外延p型柱(n>=y),y满足公式y= n-x;所述上外延p型柱与所述下外延p型柱之间存在有间隔尺寸d。本实用新型中通过将所述上外延p型柱浮游于所述下外延p型柱的上方,来改变雪崩时的电流路径,该新型超结mos场效应晶体管的最强电场分布在所述上外延p型柱外延的下方,这将有效吸附空穴,进而改变雪崩时的电流路径,电流主要通过p柱流出器件,从而有效地避免了器件内部的寄生bjt的触发,提高器件的eas耐压。同时,所设置的所述上外延p型柱浮游于所述下外延p型柱上方后,两者间存在有间隔尺寸d,间隔尺寸d与所述多次外延p型柱中各层的厚度比为7~13:10,通过该有效尺寸的设置,使得吸附空穴效果更加突出,进而进一步提高器件的eas耐压。

6、 2. 在上述技术方案中,所述多次外延p型柱的总层数为6层(n>6层),所述下外延p型柱的层数为5层(n-1层),所述上外延p型柱位于第6层,以便于生产工艺的实现,提高生产效率、提高良品率。

7、 3. 在上述技术方案中,所述n型源区的底部深度超出所述p型源区的底部深度。

8、 4. 在上述技术方案中,所述p型源区与所述n型源区的深度比为5~6:10,p型源区与n型源区的有效深度比有利于器件导通时,减少电子的有效路径。

9、 5. 在上述技术方案中,所述n型源区与所述p型基区的深度比为2~4:10,n型源区与p型基区的有效深度比有利于器件导通时,减少电子的有效路径。

10、 6. 在上述技术方案中,所述n型衬底与所述n型外延层的深度比为1~3:10,n型衬底与n型外延层的有效深度比有利于器件导通时,减少电子的有效路径。

11、 7. 在上述技术方案中,所述多次外延结构与所述n型外延层的深度比为7~9:10,多次外延结构与n型外延层的有效深度比有利于器件导通时,减少电子的有效路径。

12、 8.在本实用新型中,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”、“固定”等术语应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或成一体;可以是机械连接,可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通或两个元件的相互作用关系,除非另有明确的限定。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本技术中的具体含义。

13、 9.此外,术语“第一”、“第二”等仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括至少一个该特征。在本技术的描述中,“多个”的含义是至少两个,例如两个,三个等,除非另有明确具体的限定。

14、由于上述技术方案的运用,本实用新型与现有技术相比具有下列优点:

15、本实用新型的一种高耐量浮游型超结mos场效应晶体管元胞结构及其晶体管,针对传统的超结mosfet的应用及测试中器件在非嵌位感性负载开关(uis)测试的电流路径比较,所发现的传统的超结mosfet存在的容易触发器件内部的寄生bjt、无法有效提高器件的eas耐压等问题,提出了一种高耐量浮游型超结mos场效应晶体管元胞结构及其晶体管,该方案中,所述元胞结构中的所述多次外延p型柱具有位于上段的上外延p型柱以及位于下段的下外延p型柱,所述上外延p型柱浮游于所述下外延p型柱的上方,两者间填充n型外延层,所述上外延p型柱向上延伸入所述p型基区中,从下到上延伸设置的多次外延p型柱的总层数为n层(n>3),所述下外延p型柱的层数为x层(n>x),其中第y层至第n层为所述上外延p型柱(n>=y),y满足公式y= n-x;所述上外延p型柱与所述下外延p型柱之间存在有间隔尺寸d。本实用新型中通过将所述上外延p型柱浮游于所述下外延p型柱的上方,来改变雪崩时的电流路径,该新型超结mos场效应晶体管的最强电场分布在所述上外延p型柱外延的下方,这将有效吸附空穴,进而改变雪崩时的电流路径,电流主要通过p柱流出器件,从而有效地避免了器件内部的寄生bjt的触发,提高器件的eas耐压。同时,所设置的所述上外延p型柱浮游于所述下外延p型柱上方后,两者间存在有间隔尺寸d,间隔尺寸d与所述多次外延p型柱中各层的厚度比为7~13:10,通过该有效尺寸的设置,使得吸附空穴效果更加突出,进而进一步提高器件的eas耐压。

- 还没有人留言评论。精彩留言会获得点赞!