一种贴片二极管的制作方法

本技术涉及一种贴片二极管,属于二极管领域。

背景技术:

1、贴片二极管又称晶体二极管,它是一种具有单向传导电流的电子器件,在半导体二极管内部有一个pn结两个引线端子,这种电子器件按照外加电压的方向,具备单向电流的转导性,由于二极管安全、高效、环保和寿命长的特点广泛用于电子产品和光纤通信等方面。

2、申请号为cn201320491351.8的实用新型专利公开了一种贴片二极管,其包括第一引脚片、第二引脚片、密封绝缘层和芯片;所述第一引脚片与芯片的底面和左侧面焊接在一起,第二引脚片与芯片的顶面和右侧面焊接在一起;所述第一引脚片和第二引脚片位于密封绝缘层内部分与第一引脚片和第二引脚片位于密封绝缘层外部分均呈z字形。第一引脚片和第二引脚片位于密封绝缘层外的部分设置成z字形,使第一引脚片和第二引脚片的下端与密封绝缘层之间保持一定的距离,使二极管工作时产生的热量向外界传递,从而提高了贴片二极管的使用寿命。但是,在后序加工中,需要对引脚片进行切割,即切筋,而切筋过程中,引脚片受到应力并作用到芯片上,易导致芯片偏位而损坏。

3、因此,需要有一种贴片二极管,避免切筋过程中导致芯片损坏。

技术实现思路

1、本实用新型要解决的技术问题是:为了克服现有技术的不足,提供避免切筋过程中导致芯片损坏的一种贴片二极管。

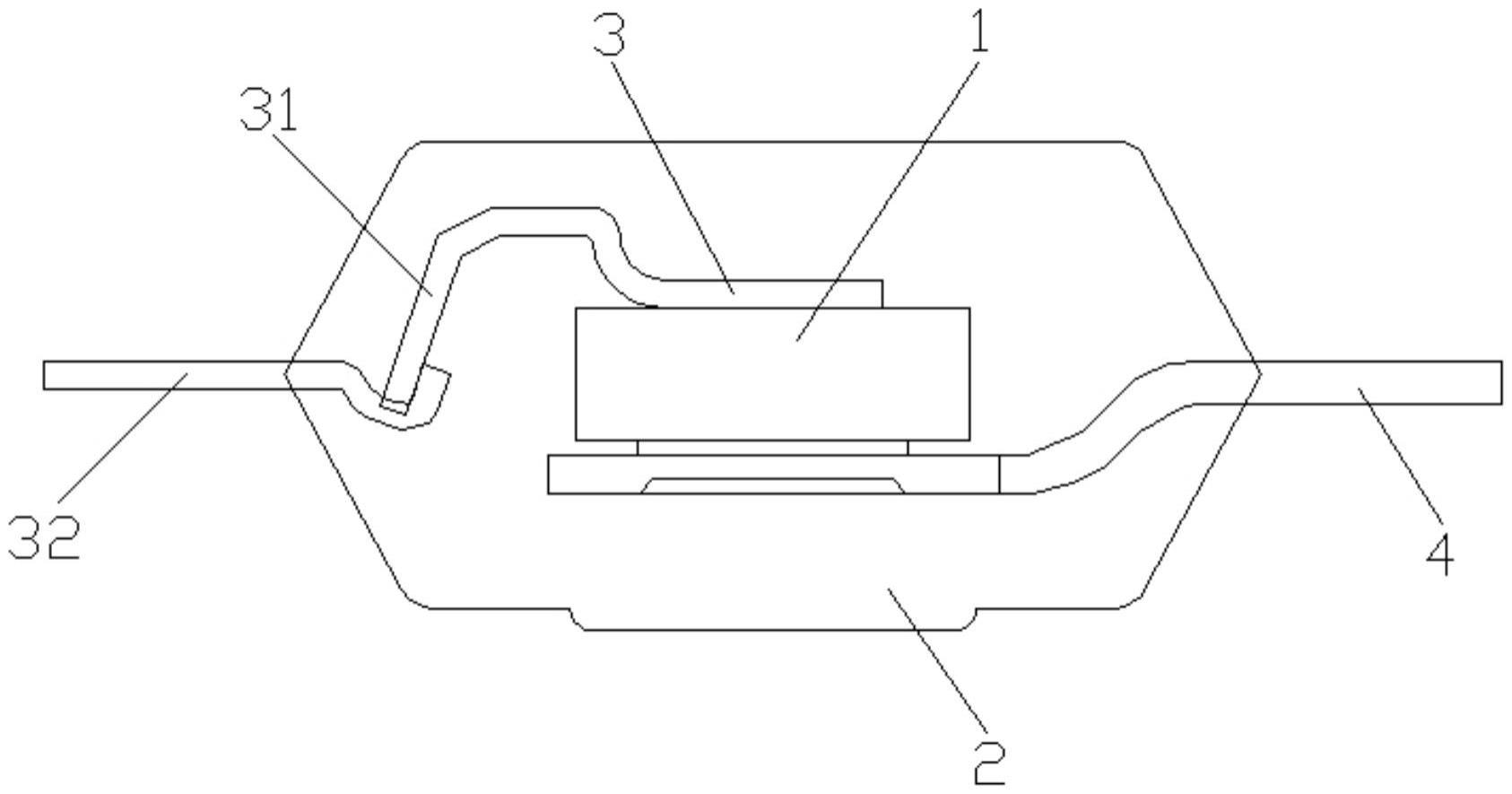

2、本实用新型解决上述问题所采用的技术方案为:一种贴片二极管,包括芯片,所述芯片外部包裹有塑封体,所述芯片的电气面连接有第一引脚,所述芯片的贴装面连接有第二引脚,所述第一引脚和第二引脚分别从芯片两侧延伸至塑封体的外部;

3、所述第一引脚包括内接引脚和外接引脚,所述外接引脚的内端设置有折弯,所述折弯上表面设置有连接槽,所述内接引脚的一端插入连接槽,所述内接引脚的另一端与芯片的电气面连接,所述内接引脚与连接槽焊接。

4、作为优选,所述塑封体呈扁平状。

5、作为优选,所述第一引脚和第二引脚均为扁平状。

6、作为优选,所述塑封体的长度为3.5mm~5.2mm。

7、作为优选,所述塑封体的厚度为1.98mm~2.3mm。

8、作为优选,所述折弯和内接引脚均位于塑封体内。

9、作为优选,所述连接槽与内接引脚匹配。

10、作为优选,所述内接引脚与连接槽通过锡膏焊接。

11、作为优选,所述第二引脚通过装片胶与芯片的贴装面连接。

12、作为优选,所述内接引脚的插入连接槽内的一端设置有倒角。

13、与现有技术相比,本实用新型的优点在于:

14、本实用新型一种贴片二极管,通过将内接引脚和外接引脚通过锡膏焊接形成第一引脚,可以通过锡膏吸收第一引脚在切筋过程中产生的应力,从而可以避免芯片因应力而损坏。

技术特征:

1.一种贴片二极管,其特征在于:包括芯片(1),所述芯片(1)外部包裹有塑封体(2),所述芯片(1)的电气面连接有第一引脚(3),所述芯片(1)的贴装面连接有第二引脚(4),所述第一引脚(3)和第二引脚(4)分别从芯片(1)两侧延伸至塑封体(2)的外部;

2.根据权利要求1所述的一种贴片二极管,其特征在于:所述塑封体(2)呈扁平状。

3.根据权利要求2所述的一种贴片二极管,其特征在于:所述第一引脚(3)和第二引脚(4)均为扁平状。

4.根据权利要求1所述的一种贴片二极管,其特征在于:所述塑封体(2)的长度为3.5mm~5.2mm。

5.根据权利要求1所述的一种贴片二极管,其特征在于:所述塑封体(2)的厚度为1.98mm~2.3mm。

6.根据权利要求1所述的一种贴片二极管,其特征在于:所述折弯(33)和内接引脚(31)均位于塑封体(2)内。

7.根据权利要求1所述的一种贴片二极管,其特征在于:所述连接槽(34)与内接引脚(31)匹配。

8.根据权利要求1所述的一种贴片二极管,其特征在于:所述内接引脚(31)与连接槽(34)通过锡膏焊接。

9.根据权利要求1所述的一种贴片二极管,其特征在于:所述第二引脚(4)通过装片胶与芯片(1)的贴装面连接。

10.根据权利要求1所述的一种贴片二极管,其特征在于:所述内接引脚(31)的插入连接槽(34)内的一端设置有倒角。

技术总结

本技术涉及一种贴片二极管,包括芯片,所述芯片外部包裹有塑封体,所述芯片的电气面连接有第一引脚,所述芯片的贴装面连接有第二引脚,所述第一引脚和第二引脚分别从芯片两侧延伸至塑封体的外部;所述第一引脚包括内接引脚和外接引脚,所述外接引脚的内端设置有折弯,所述折弯上表面设置有连接槽,所述内接引脚的一端插入连接槽,所述内接引脚的另一端与芯片的电气面连接,所述内接引脚与连接槽焊接。该贴片二极管,通过将内接引脚和外接引脚通过锡膏焊接形成第一引脚,可以通过锡膏吸收第一引脚在切筋过程中产生的应力,从而可以避免芯片因应力而损坏。

技术研发人员:潘宜虎,杨吉明,安国星,戴亮,周琦

受保护的技术使用者:江苏海德半导体有限公司

技术研发日:20221223

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!