多个芯粒的双密封环和电连接的制作方法

本发明总体上涉及电子设备,并且具体地涉及由多个芯粒(chiplet,也可称为“芯片组”)制造的高性能电子设备的改进方法和系统。

背景技术:

1、本领域已知各种技术可以用于从多个芯片和/或芯粒制造高性能电子设备、以及用于制造其中在制造期间在硅晶片上的芯片和/或芯粒的不同组合周围形成有密封环的设备。这种技术为晶片划片提供了不同选择,其方式使得能够生产具有不同倍数的电路系统部件的芯片,这些电路系统组件备选地可以是独立或组合部件,而不必专门设计不同芯片。

2、例如,美国专利9,865,503(其公开内容通过引用并入本文)描述了在芯片制造期间使用掩模组的下层和上层掩模在半导体晶片上形成电路结构的多个模块化单元。该方法包括在集成电路(ic)制造期间利用不同上层掩模在ic的金属层中形成将下层ic结构完全耦合在半导体晶片的单个管芯内的嵌入式上层ic结构、或者耦合管芯中的下层结构并且延伸跨过密封环状边界以耦合相邻管芯的形成在半导体ic中的嵌入式上层ic结构。

3、以上描述被呈现作为对该领域相关技术的总体概述,而不应当被解释为承认其包含的任何信息构成针对本专利申请的现有技术。

技术实现思路

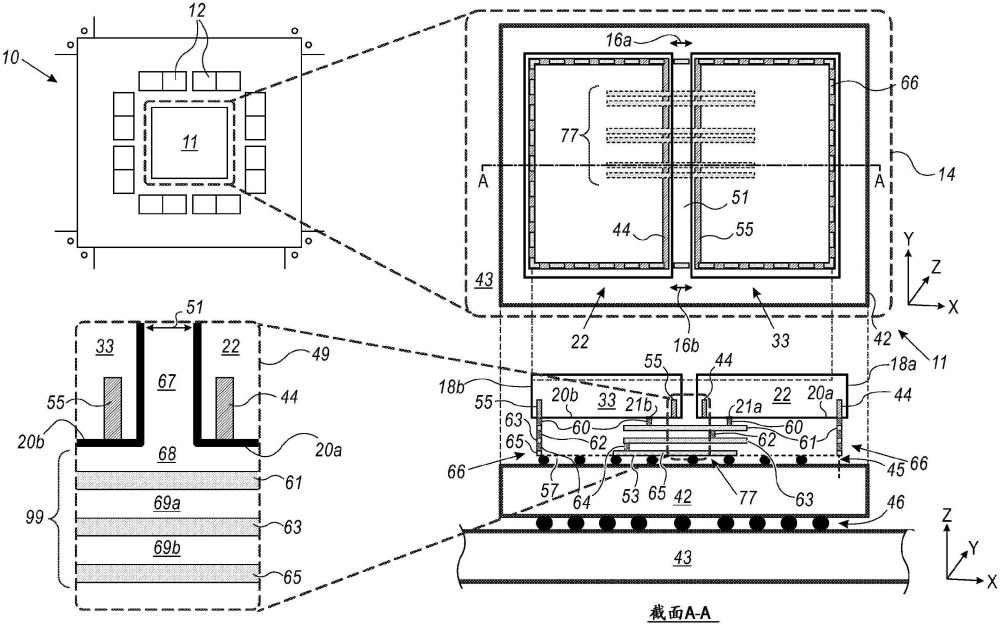

1、本文中描述的一个实施例提供了一种电子设备,该电子设备包括:(i)包括第一密封环的第一芯粒,第一密封环被设置在嵌入在第一芯粒的第一表面与第一芯粒的第一衬底之间的金属层中,(ii)包括第二密封环的第二芯粒,第二密封环被设置在嵌入在第二芯粒的第二表面与第二芯粒的第二衬底之间的金属层中,以及(iii)第三密封环,该第三密封环围绕第一芯粒和第二芯粒,并且被设置在金属层外部的介电衬底中,并且覆盖第一芯粒的第一表面和第二芯粒的第二表面。

2、在一些实施例中,第三密封环的至少第三部分被分别设置在第一密封环的第一部分和第二密封环的第二部分之上。在其他实施例中,第一芯粒包括设置在第一表面上的第一电端子,第二芯粒包括设置在第二表面上的第二电端子,电子设备包括电连接,电连接被设置在第一电端子和第二电端子之上并且被配置为在第一电端子与第二电端子之间传导电信号。在其他实施例中,电子设备包括至少导电层,并且电连接和第三密封环的至少一部分被实现在导电层中。

3、在一些实施例中,电连接被形成在使用一个或多个导电过孔电连接的层堆叠中的至少第一层和第二层中,层堆叠包括:(a)第一介电层,第一介电层被形成在(i)第一表面和第二表面与(ii)第一层之间,并且具有第一介电常数;以及(b)第二介电层,第二介电层被形成在第一层与第二层之间,并且具有不同于第一介电常数的第二介电常数。在其他实施例中,层堆叠包括在设置在第一表面和第二表面之上的至少第一层和第二层中实现的第三密封环,第一芯粒和第二芯粒以及层堆叠被翻转并且被设置在公共衬底上,电子设备包括在第一芯粒与第二芯粒之间的间隙,间隙被填充有具有不同于第二介电常数的第三介电常数的第三介电层,并且第三密封环的第四部分被设置在第一介电层的表面上。在其他实施例中,第一介电常数和第二介电常数中的至少一者小于第三介电常数。

4、在一些实施例中,公共衬底包括中介层或电路板,并且包括附加电连接,附加电连接被设置在公共衬底与层堆叠中的第一层和第二层中的至少一者之间,附加电连接被配置为在公共衬底与第一层和第二层中的至少一者之间传导信号。在其他实施例中,第一层和第二层包括铜,第一介电层包括具有大于3.2的第一介电常数的碳掺杂的二氧化硅或光敏聚酰亚胺,并且第二介电层包括多孔的ch3掺杂的二氧化硅或聚苯并恶唑(pbo),并且第二介电常数小于2.7。在其他实施例中,第三密封环包围的区域大于858平方毫米。

5、根据本发明的一个实施例,还提供了一种用于生产电子设备的方法,该方法包括在公共衬底上设置第一芯粒,第一芯粒包括形成在第一芯粒的金属层中的第一密封环,第一密封环被设置在第一芯粒的第一表面与第一芯粒的第一衬底之间。在公共衬底上设置第二芯粒,第二芯粒包括形成在第二芯粒的金属层中的第二密封环,第二密封环被设置在第二芯粒的第二表面与第二芯粒的第二衬底之间。设置金属层外部的介电衬底以覆盖第一芯粒的第一表面和第二芯粒的第二表面,并且在介电衬底中形成第三密封环以围绕第一芯粒和第二芯粒。

6、通过以下结合附图对本公开的实施例的详细描述,将能够更充分地理解本公开,在附图中:

技术特征:

1.一种电子设备,包括:

2.根据权利要求1所述的电子设备,其中所述第三密封环的至少第三部分被分别设置在所述第一密封环的第一部分和所述第二密封环的第二部分之上。

3.根据权利要求1至2中任一项所述的电子设备,其中所述第一芯粒包括设置在所述第一表面上的第一电端子,所述第二芯粒包括设置在所述第二表面上的第二电端子,所述电子设备包括电连接,所述电连接被设置在所述第一电端子和所述第二电端子之上并且被配置为在所述第一电端子与所述第二电端子之间传导电信号。

4.根据权利要求3所述的电子设备,其中所述电子设备包括至少导电层,并且其中所述电连接和所述第三密封环的至少一部分被实现在所述导电层中。

5.根据权利要求4所述的电子设备,其中所述电连接被形成在使用一个或多个导电过孔电连接的层堆叠中的至少第一层和第二层中,所述层堆叠包括:(a)第一介电层,所述第一介电层被形成在(i)所述第一表面和所述第二表面与(ii)所述第一层之间,并且具有第一介电常数;以及(b)第二介电层,所述第二介电层被形成在所述第一层与所述第二层之间,并且具有不同于所述第一介电常数的第二介电常数。

6.根据权利要求5所述的电子设备,其中所述层堆叠包括在设置在所述第一表面和所述第二表面之上的至少所述第一层和所述第二层中实现的所述第三密封环,其中所述第一芯粒和所述第二芯粒以及所述层堆叠被翻转并且被设置在公共衬底上,其中所述电子设备包括所述第一芯粒与所述第二芯粒之间的间隙,其中所述间隙被填充有具有不同于所述第二介电常数的第三介电常数的第三介电层,并且其中所述第三密封环的第四部分被设置在所述第一介电层的表面上。

7.根据权利要求6所述的电子设备,其中所述第一介电常数和所述第二介电常数中的至少一者小于所述第三介电常数。

8.根据权利要求6所述的电子设备,其中所述公共衬底包括中介层或电路板,并且包括附加电连接,所述附加电连接被设置在所述公共衬底与所述层堆叠中的所述第一层和所述第二层中的至少一者之间,所述附加电连接被配置为在所述公共衬底与所述第一层和所述第二层中的至少一者之间传导信号。

9.根据权利要求5所述的电子设备,其中所述第一层和所述第二层包括铜,所述第一介电层包括具有大于3.2的所述第一介电常数的碳掺杂的二氧化硅或光敏聚酰亚胺,并且其中所述第二介电层包括多孔的ch3掺杂的二氧化硅或聚苯并恶唑(pbo),其中所述第二介电常数小于2.7。

10.根据权利要求1至2中任一项所述的电子设备,其中所述第三密封环包围的区域大于858平方毫米。

11.一种用于生产电子设备的方法,所述方法包括:

12.根据权利要求11所述的方法,其中设置所述第三密封环包括将所述第三密封环的至少第三部分分别设置在所述第一密封环的第一部分和所述第二密封环的第二部分之上。

13.根据权利要求11至12中任一项所述的方法,其中所述第一芯粒包括设置在所述第一表面上的第一电端子,并且所述第二芯粒包括设置在所述第二表面上的第二电端子,并且其中生产所述电子设备包括在所述第一电端子和所述第二电端子之上设置用于在所述第一电端子与所述第二电端子之间传导电信号的电连接。

14.根据权利要求13所述的方法,其中设置所述第三密封环和所述电连接包括形成至少导电层,并且其中所述电连接和所述第三密封环的至少一部分被实现在所述导电层中。

15.根据权利要求14所述的方法,其中设置所述电连接包括形成层堆叠,所述层堆叠包括至少第一层和第二层以及用于在所述第一层与所述第二层之间进行电连接的一个或多个导电过孔,并且其中形成所述层堆叠包括:(a)在(i)所述第一表面和所述第二表面与(ii)所述第一层之间形成第一介电层,所述第一介电层具有第一介电常数;以及(b)在所述第一层与所述第二层之间形成第二介电层,所述第二介电层具有不同于所述第一介电常数的第二介电常数。

16.根据权利要求15所述的方法,其中形成所述层堆叠包括:形成在设置在所述第一表面和所述第二表面之上的至少所述第一层和所述第二层中实现的所述第三密封环,并且翻转所述第一芯粒和所述第二芯粒以及所述层堆叠,并且将所述层堆叠设置在公共衬底上,其中所述电子设备包括所述第一芯粒与所述第二芯粒之间的间隙,并且所述方法包括:用具有不同于所述第二介电常数的第三介电常数的第三介电层来填充所述间隙,以及将所述第三密封环的第四部分设置在所述第一介电层的表面上。

17.根据权利要求16所述的方法,其中所述第一介电常数和所述第二介电常数中的至少一者小于所述第三介电常数。

18.根据权利要求16所述的方法,其中所述公共衬底包括中介层或电路板,并且所述方法包括:在所述公共衬底与所述层堆叠的所述第一层和所述第二层中的至少一者之间设置用于在所述公共衬底与所述第一层和所述第二层中的至少一者之间传导信号的附加电连接。

19.根据权利要求15所述的方法,其中所述第一层和所述第二层包括铜,所述第一介电层包括具有大于3.2的所述第一介电常数的碳掺杂的二氧化硅或光敏聚酰亚胺,并且其中所述第二介电层包括多孔的ch3掺杂的二氧化硅或聚苯并恶唑(pbo),其中所述第二介电常数小于2.7。

20.根据权利要求11至12中任一项所述的方法,其中所述第三密封环包围的区域大于858平方毫米。

技术总结

一种电子设备(11)包括:(i)包括第一密封环(44)的第一芯粒(22),第一密封环被设置在嵌入在第一芯粒(22)的第一表面(20a)与第一芯粒(22)的第一衬底(18a)之间的金属层中,(ii)包括第二密封环(55)的第二芯粒(33),第二密封环被设置在嵌入在第二芯粒(33)的第二表面(20b)与第二芯粒(33)的第二衬底(18b)之间的金属层中,以及(iii)第三密封环(66),第三密封环围绕第一芯粒和第二芯粒(22,33),并且被设置在介电衬底(67,68,69a,69b)中,介电衬底位于金属层外部并且覆盖第一芯粒和第二芯粒(22,33)的第一表面和第二表面(20a,20b)。

技术研发人员:张丽娟,常润滋

受保护的技术使用者:马维尔亚洲私人有限公司

技术研发日:

技术公布日:2024/3/4

- 还没有人留言评论。精彩留言会获得点赞!