半导体器件的制造方法与流程

本发明涉及半导体制造,特别涉及一种半导体器件的制造方法。

背景技术:

1、在现有的半导体器件如金属氧化物半导体场效应晶体管(metal oxidesemiconductor field-effect transistor,mosfet)的制造方法中,通常先在衬底上形成硬掩膜层,然后以硬掩膜层为掩膜刻蚀衬底以形成浅沟槽(sti),相邻的浅沟槽之间的区域为有源区。在形成浅沟槽之后,需对衬底上的硬掩膜层进行刻蚀,从而暴露出衬底靠近浅沟槽的部分区域。然而,由于受刻蚀的负载效应的影响,衬底的暴露区域的顶面宽度往往达不到工艺所需的目标宽度,由此影响器件的稳定性,甚至影响器件的电性性能,例如影响器件的阈值电压。

技术实现思路

1、本发明的目的在于提供一种半导体器件的制造方法,以使刻蚀硬掩膜层之后的衬底的暴露区域的顶面宽度与目标宽度相符合。

2、为实现上述目的,本发明提供一种半导体器件的制造方法,包括:

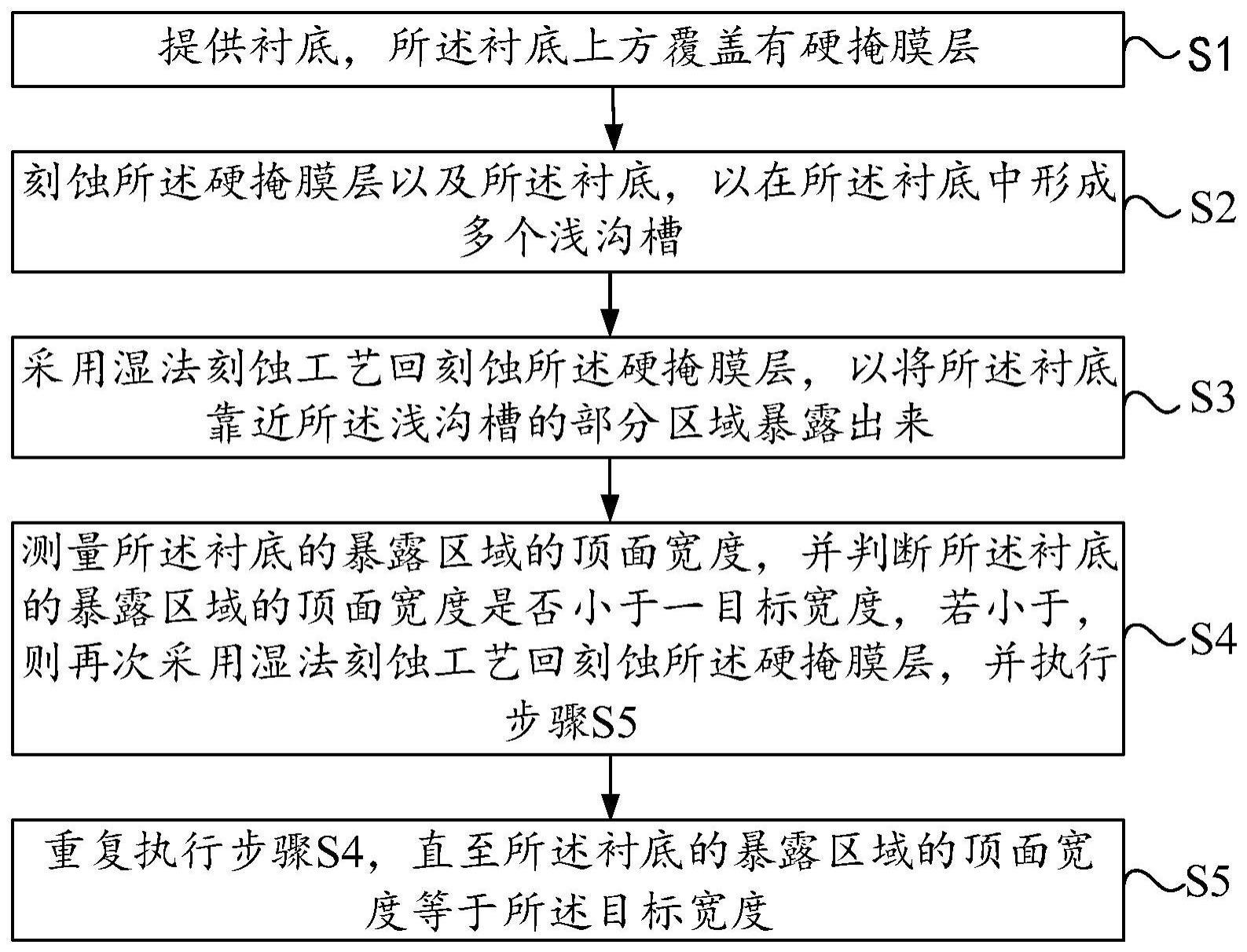

3、步骤s1:提供衬底,所述衬底上方覆盖有硬掩膜层;

4、步骤s2:刻蚀所述硬掩膜层以及所述衬底,以在所述衬底中形成多个浅沟槽;

5、步骤s3:采用湿法刻蚀工艺回刻蚀所述硬掩膜层,以将所述衬底靠近所述浅沟槽的部分区域暴露出来;

6、步骤s4:测量所述衬底的暴露区域的顶面宽度,并判断所述衬底的暴露区域的顶面宽度是否小于一目标宽度,若小于,则再次采用湿法刻蚀工艺回刻蚀所述硬掩膜层,并执行步骤s5;

7、步骤s5:重复执行步骤s4,直至所述衬底的暴露区域的顶面宽度等于所述目标宽度。

8、可选的,在所述的半导体器件的制造方法中,所述目标宽度为20nm~30nm。

9、可选的,在所述的半导体器件的制造方法中,通过自动反馈系统判断所述衬底的暴露区域的顶面宽度是否小于目标宽度。

10、可选的,在所述的半导体器件的制造方法中,采用湿法刻蚀工艺回刻蚀所述硬掩膜层时,采用的溶液包括磷酸和氢氟酸。

11、可选的,在所述的半导体器件的制造方法中,通过光学关键尺寸测量系统测量所述衬底的暴露区域的顶面宽度。

12、可选的,在所述的半导体器件的制造方法中,所述衬底的暴露区域的顶面宽度等于所述目标宽度之后,还包括:

13、对所述衬底靠近所述浅沟槽的部分区域进行圆角处理;以及,

14、在所述浅沟槽中填充隔离层,以形成浅沟槽隔离结构。

15、可选的,在所述的半导体器件的制造方法中,通过热氧化工艺对所述衬底靠近所述浅沟槽的部分区域进行圆角处理。

16、可选的,在所述的半导体器件的制造方法中,所述硬掩膜层包括氧化硅层和形成于所述氧化硅层上的氮化硅层。

17、可选的,在所述的半导体器件的制造方法中,相邻的所述浅沟槽之间的衬底为有源区,所述半导体器件包括第一有源区和第二有源区,所述第一有源区的顶面宽度小于所述第二有源区的顶面宽度。

18、可选的,在所述的半导体器件的制造方法中,在刻蚀所述硬掩膜层以及所述衬底之后,所述硬掩膜层覆盖所述第一有源区和所述第二有源区;

19、以及,在采用湿法刻蚀工艺回刻蚀所述硬掩膜层时,回刻蚀所述第一有源区和所述第二有源区的所述硬掩膜层。

20、在本发明提供的半导体器件的制造方法中,在刻蚀硬掩膜层以及衬底,以在衬底中形成浅沟槽之后,先采用湿法刻蚀工艺回刻蚀硬掩膜层,以将所述衬底靠近所述浅沟槽的部分区域暴露出来,采用湿法刻蚀工艺回刻蚀硬掩膜层可以使硬掩膜层的各个方向的刻蚀量较为均匀,由此避免产生刻蚀负载效应。然后,测量衬底的暴露区域的顶面宽度,并判断衬底的暴露区域的顶面宽度是否小于一目标宽度,若小于,则再次采用湿法刻蚀工艺回刻蚀硬掩膜层,重复执行该步骤,直至衬底的暴露区域的顶面宽度等于目标宽度。如此,可以使衬底的暴露区域的顶面宽度达到目标宽度,从而使衬底的暴露区域的顶面宽度与目标宽度相符合,提高器件的稳定性以及电性性能。

技术特征:

1.一种半导体器件的制造方法,其特征在于,包括:

2.如权利要求1所述的半导体器件的制造方法,其特征在于,所述目标宽度为20nm~30nm。

3.如权利要求1所述的半导体器件的制造方法,其特征在于,通过自动反馈系统判断所述衬底的暴露区域的顶面宽度是否小于目标宽度。

4.如权利要求1所述的半导体器件的制造方法,其特征在于,采用湿法刻蚀工艺回刻蚀所述硬掩膜层时,采用的溶液包括磷酸和氢氟酸。

5.如权利要求1所述的半导体器件的制造方法,其特征在于,通过光学关键尺寸测量系统测量所述衬底的暴露区域的顶面宽度。

6.如权利要求1所述的半导体器件的制造方法,其特征在于,所述衬底的暴露区域的顶面宽度等于所述目标宽度之后,还包括:

7.如权利要求6所述的半导体器件的制造方法,其特征在于,通过热氧化工艺对所述衬底靠近所述浅沟槽的部分区域进行圆角处理。

8.如权利要求1所述的半导体器件的制造方法,其特征在于,所述硬掩膜层包括氧化硅层和形成于所述氧化硅层上的氮化硅层。

9.如权利要求1所述的半导体器件的制造方法,其特征在于,相邻的所述浅沟槽之间的衬底为有源区,所述半导体器件包括第一有源区和第二有源区,所述第一有源区的顶面宽度小于所述第二有源区的顶面宽度。

10.如权利要求9所述的半导体器件的制造方法,其特征在于,在刻蚀所述硬掩膜层以及所述衬底之后,所述硬掩膜层覆盖所述第一有源区和所述第二有源区;

技术总结

本发明提供一种半导体器件的制造方法,在刻蚀硬掩膜层以及衬底,以在衬底中形成浅沟槽之后,先采用湿法刻蚀工艺回刻蚀硬掩膜层,以将衬底靠近浅沟槽的部分区域暴露出来,采用湿法刻蚀工艺回刻蚀硬掩膜层可以使硬掩膜层的各个方向的刻蚀量较为均匀,由此避免产生刻蚀负载效应。然后,测量衬底的暴露区域的顶面宽度,并判断衬底的暴露区域的顶面宽度是否小于一目标宽度,若小于,则再次采用湿法刻蚀工艺回刻蚀硬掩膜层,重复执行该步骤,直至衬底的暴露区域的顶面宽度等于目标宽度。如此,可以使衬底的暴露区域的顶面宽度达到目标宽度,从而使衬底的暴露区域的顶面宽度与目标宽度相符合,提高器件的稳定性以及电性性能。

技术研发人员:张静

受保护的技术使用者:合肥晶合集成电路股份有限公司

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!