一种SiCMOSFET闩锁鲁棒性加固结构及方法与流程

本发明属于半导体,具体涉及一种静电浪涌诱发的sic mosfet闩锁鲁棒性加固结构及方法。

背景技术:

1、第三代宽禁带半导体如碳化硅(sic)、氮化镓(gan)等因其禁带宽度大(sic3.26ev、gan 3.4ev),击穿电场高,功率密度大。碳化硅mosfet是一种具有绝缘栅结构的单极性器件、开关速度较快、开关频率较高,可以减小电路装置中电感和电容的体积,有利于实现电力电子装置的小型化。

2、相较于需要电流持续驱动栅极结型场效应管(jfet)和双极性晶体管(bjt),更易于控制。而相较于绝缘栅双极型晶体管(igbt),由于不存在关断时的拖尾电流,其开关频率较高,且在高频应用中开关损耗低于相同等级的igbt器件。上述对比表明sic mosfet器件的潜在优势明显。

3、因静电浪涌诱发的闩锁问题是sic mosfet非常重要的可靠性问题,极大地影响sic mosfet工作的稳定性。

4、静电在人体或者机器之间在接触时会相互转移,在短时间内产生数千甚至上万伏特的静电冲击。根据应用领域不同,sic mosfet的耐压设计值在1.6kv~3kv之间,特殊条件下可达10kv。在sic mosfet正常工作时,工作电压均小于器件耐压,mosfet寄生的bjt并不开启。但是,一旦遇到静电冲击,数千甚至上万的静电电压会使得sic mosfet瞬间击穿,寄生bjt开启。寄生bjt如果被静电冲击触发开启而不能重新进入关断状态,则发生静电诱发的闩锁可靠性问题。

5、同样的,在电力电子系统运行期间,功率因数校正(pfc)的启动过程或故障运行会引起数倍的电流涌入设备。巨大的电流从sic mosfet内部流过的时候,也会使得内部寄生bjt开启,进而产生浪涌诱发的闩锁可靠性问题。

6、包括静电诱发和浪涌诱发在内的闩锁可靠性问题,轻则使得sic mosfet失效,无法正常关断而需要重新启动整个系统;重则使得sic mosfet烧毁,令整个功率模块或者高压功率系统瘫痪,造成严重的经济损失。

技术实现思路

1、针对静电浪涌诱发的闩锁可靠性问题,本发明公开了一种sic mosfet闩锁鲁棒性加固结构及方法,与将其应用在平面栅以及埋栅sic mosfet器件中的典型结构,以及其制备该结构的一种实施方法。

2、为实现上述目的,本发明提供如下技术方案:

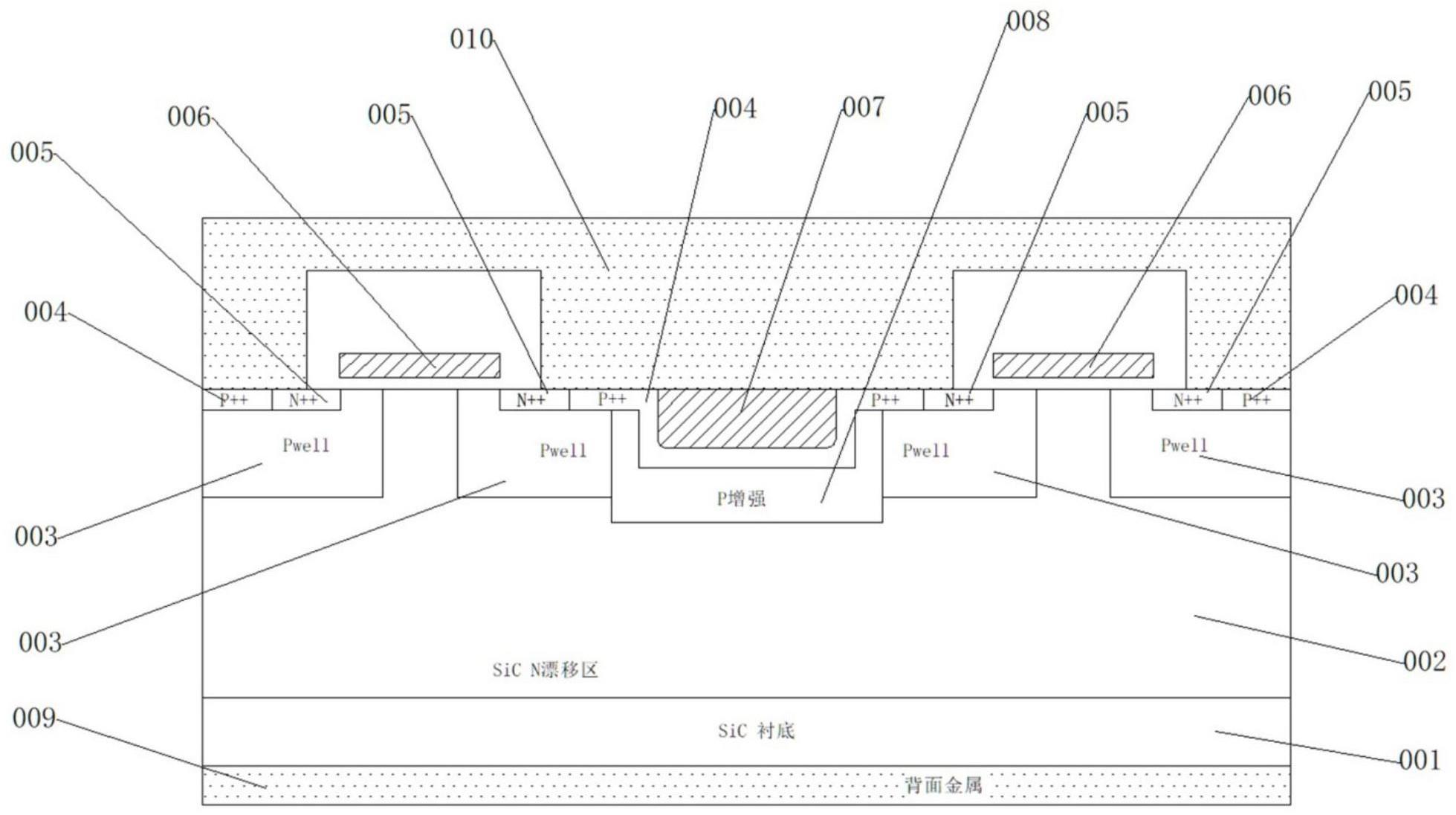

3、一种sic mosfet闩锁鲁棒性加固结构,所述sic mosfet包括半导体衬底、sic n漂移区、pwell注入区、p++注入区、n++注入区,pwell注入区作为寄生bjt基区,sic n漂移区作为寄生bjt集电极。所述加固结构包括填充接触区、p++注入区、p增强注入区;所述填充接触区为开槽并回填多晶硅的结构,所述多晶硅与p++注入区电学连接,用以填充开槽和提供机械支撑,并用以将p++注入区引出;所述p增强注入区为p类型的注入区域,绝对深度上,p增强注入区的深度叠加填充接触区的开槽深度等于或者大于pwell注入区的深度,p增强注入区的掺杂浓度较pwell注入区更高,但满足在达到整个sic mosfet设计耐压值之前不会在p++注入区、p增强注入区、sic n漂移区、半导体衬底通路上发生击穿。

4、进一步的,所述p增强注入区遮断寄生bjt基区至寄生bjt集电极的扩散电流通路面积,使得在p增强注入区一侧形成的耗尽区内部电场将注入基区的载流子扫出至p增强注入区、p++注入区通路而不进入发射区。

5、进一步的,所述p增强注入区的注入深度为5至15微米,采用7度以上的高倾斜角注入。

6、进一步的,所述半导体衬底的厚度为90至130微米,所述sic n漂移区为在半导体衬底之上外延生长低缺陷的sic外延得到,sic n漂移区的厚度在数十到数百微米量级。

7、进一步的,所述pwell注入区为p类型的注入区域,采用7度以下的低倾斜角注入,注入深度为5至15微米,掺杂浓度为5e16-3至2.5e18-3。

8、进一步的,所述p++注入区为p类型的注入区域,采用7度以上的高倾斜角注入,所述p++注入区起到欧姆接触的作用。

9、进一步的,所述n++注入区为n类型的注入区域,形成sic mosfet的源区。

10、进一步的,

11、所述sic mosfet还包括平面型控制栅,所述平面型控制栅与sic n漂移区、pwell注入区之间存在电绝缘介质,通过平面型控制栅控制pwell注入区中沟道的形成和消失,使sic mosfet导通或关闭;所述平面型控制栅分两次定义pwell注入区和n++注入区的注入图形,第一次通过淀积和图形化刻蚀定义pwell注入的注入图形,第二次通过侧强淀积或者氧化生长的方式定义n++注入区的注入图形;或者,

12、所述sic mosfet还包括埋栅型控制栅,所述埋栅型控制栅为采用埋栅工艺制备的埋栅,与表面硅和埋栅槽之间存在电绝缘介质,通过在埋栅型控制栅上施加电压控制pwell注入区中沟道的形成和消失,使sic mosfet导通或关闭。

13、进一步的,所述sic mosfet还包括背面金属、正面金属,所述背面金属为位于半导体衬底底部的背面金属结构,形成sic mosfet的漏端端口;所述正面金属为表面金属,与p++注入区、n++注入区之间电学连接,形成sic mosfet的源端端口。

14、一种基于上述加固结构的sic mosfet闩锁鲁棒性加固方法,包括如下步骤:

15、s1:在半导体衬底上生长sic n漂移区,或者直接在半导体外延片上进行对准标记的制作;

16、s2:在所需位置开槽,得到半导体衬底中的开槽;

17、s3:对半导体外延片中sic n漂移区进行选区掺杂;

18、以小于或等于7度的低倾斜角,预定环境温度下,al离子旋转注入,注入能量220kev~400kev,注入剂量5e11cm-2~7.5e13cm-2,在整个选区掺杂之后进行高温退火激活,形成pwell注入区;以大于7度的高倾斜角,预定环境温度下,al离子旋转注入,注入能量200kev~450kev,注入剂量1e14cm-2~1e14cm-2,在整个选区掺杂之后进行高温退火激活,形成p增强注入区;低倾斜角pwell注入和高倾斜角p增强注入的顺序不分先后;

19、s4:以大于7度的高倾斜角注入,注入能量30kev~400kev,注入剂量1e14cm-2~7.5e14cm-2,进行多次al离子注入形成p++注入区,直接使用sio2材料作为离子注入掩膜;同时,通过侧墙或者氧化生长的方式使得平面型控制栅向外延展,定义出沟道宽度,为之后的自对准注入做准备;

20、s5:以小于或等于7度的低倾斜角注入,进行多次氮离子注入形成n++注入区,注入图形由栅自对准工艺定义,注入能量30kev~330kev,注入剂量2e14cm-2~7.5e14cm-2,然后在开槽中填充多晶硅,经过回流填充形成填充接触区,该工艺可以提前,但不应晚于选区掺杂之后的高温激活退火;

21、s6:进行高温激活退火以修复晶格损伤;在器件表面进行后道金属工艺,引出表面电极;

22、s7:在完成硅片减薄、背面金属之后,形成完整的器件结构。

23、与现有技术相比,本发明的有益效果是:

24、1、本发明通过三个方面的改进,能够有效提高器件闩锁时的最小维持电压,使得器件能够在浪涌或者静电诱发闩锁之后,从闩锁状态恢复,进入正常工作状态,不发生闩锁锁死或者器件损毁。

25、2、本发明独特的增强注入区域浓度由注入剂量决定稳定可控,并且通过开槽并控制槽深这一可行有效的制备方式来控制增强注入区域的深度,大大降低了实现该结构的制备难度。

26、3、本发明对平面栅或者埋栅型这两种主流的sic mosfet都能够很好地兼容,通过增加少量版图以及工艺步骤,而不需要改变主要版图以及工艺流程,即可达到预期目的,灵活有效地满足了各类sic mosfet的加固需求。

- 还没有人留言评论。精彩留言会获得点赞!