一种易于集成的耗尽型MOSFET器件结构的制作方法

本发明涉及mosfet集成电路制造,特别涉及一种易于集成的耗尽型mosfet器件结构。

背景技术:

1、mos集成电路技术中,mosfet(metal-oxide-semiconductor field-effecttransistor,场效应晶体管)是主要元器件。根据导电方式的不同,mosfet可以分为增强型和耗尽型。耗尽型是指,当栅源电压为零伏时,沟道已经存在,只要加上源漏电压,就有电流流通。尽管增强型mosfet用于当今绝大多数集成电路中,耗尽型mosfet也可作为电阻元件或者电流源元件等应用于一些特定电路中,具有简化电路设计的优势。

2、阈值电压可以作为区分增强型和耗尽型mosfet的一个指标。阈值电压的调整可以通过栅电极功函数、栅介质厚度以及栅电极下方沟道区掺杂分布等几方面调整。要实现耗尽型mosfet的阈值电压,一般可以通过调整栅电极功函数、栅介质厚度以及栅电极下方沟道区掺杂分布等几方面,但是这些调整方式通常与增强型mosfet集成工艺不兼容,需要针对耗尽型mosfet要求额外增加一步或多步工艺步骤,增加了以增强型mosfet为主的集成电路成本。

3、沟道注入是调整mosfet阈值的常用方式。现代mosfet工艺技术中,沟道的形成是通过离子注入形成的,通过离子注入形成所需的沟道杂质分布,可以降低对热过程的需求,并形成浅的沟道区域。耗尽型mosfet可以通过在栅极下方布置一层浅的“耗尽型”沟道区域连接源极和漏极。这种耗尽型沟道区域的扩散深度(距离硅表面的深度)不能太深,否则,沟道区域不容易受栅极控制,影响晶体管的特性,因此后续工艺步骤不能采用过高的热过程。因此这种增加一步耗尽型沟道注入的常规耗尽型mosfet可集成性也是有限制的,特别是对于热过程比较多的功率mosfet集成电路。

技术实现思路

1、本发明的目的在于提供一种易于集成的耗尽型mosfet器件结构,以解决背景技术中的问题。

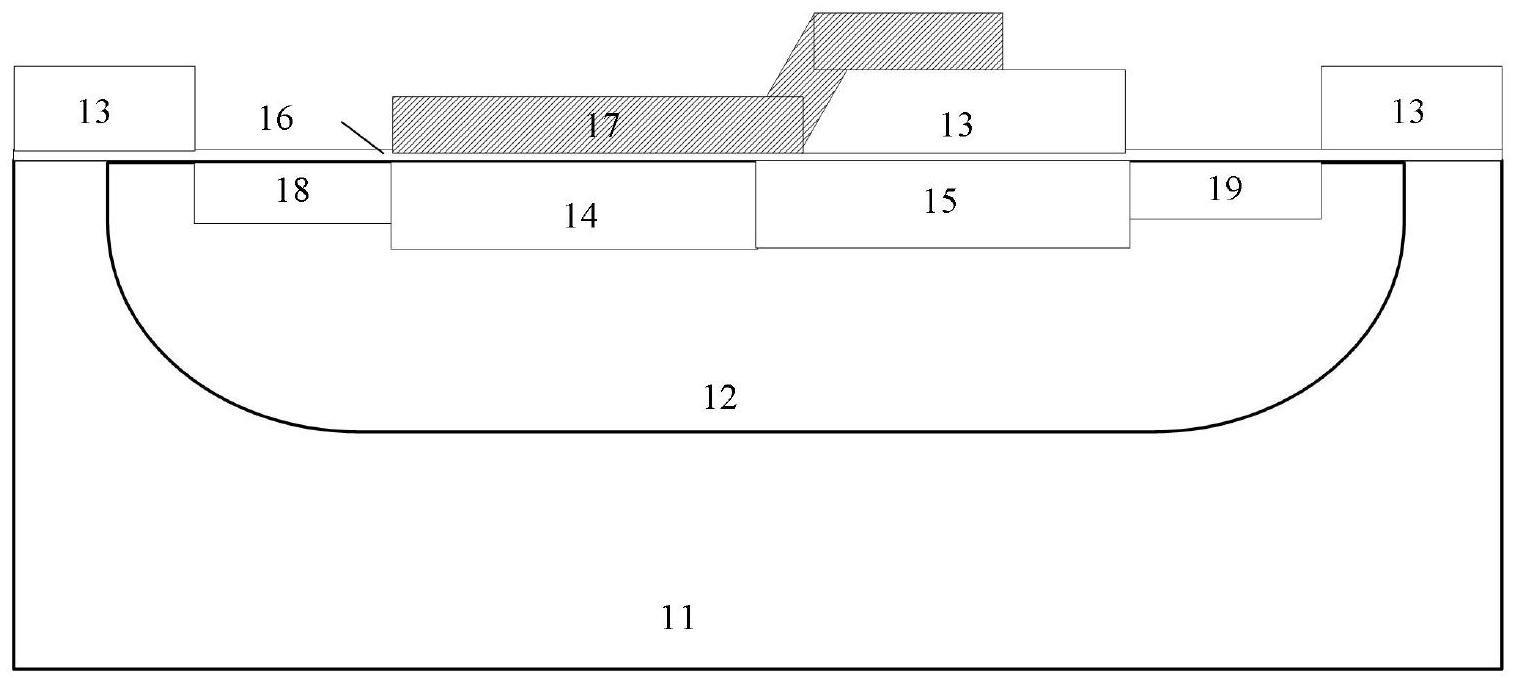

2、为解决上述技术问题,本发明提供了一种易于集成的耗尽型mosfet器件结构,包括半导体衬底,还包括第一导电型阱区和第二导电型沟道区;

3、所述第一导电型阱区形成于所述半导体衬底上,所述第二导电型沟道区形成于所述第一导电型阱区上;

4、所述第二导电型沟道区上形成有栅极绝缘膜;在所述栅极绝缘膜上形成有栅电极;所述栅电极的两侧分别形成有第二导电型源极区和第二导电型漏极区;

5、所述第二导电型源极区和所述第二导电型漏极区的宽度要分别大于所述第二导电型沟道区的宽度,所述第二导电型沟道区宽度方向上的两侧第一导电型阱区也被所述栅极绝缘膜覆盖,通过调整所述栅极绝缘膜所覆盖的第二导电型沟道区的宽度与所述栅极绝缘膜所覆盖的第一导电型阱区的宽度比,调整耗尽型mosfet的开态饱和特性和关态漏电特性。

6、在一种实施方式中,根据器件电流要求,所述栅极绝缘膜的下方能够按照该宽度比布置多条第二导电型沟道区。

7、在一种实施方式中,对于高压耗尽型mosfet,所述易于集成的耗尽型mosfet器件结构还包括第二导电型连接区,与所述第二导电型沟道区相邻接;其作用类比于高压器件的漂移区。

8、在一种实施方式中,所述第二导电型沟道区的导电类型与所述第一导电型阱区的导电类型相反。

9、在一种实施方式中,所述第二导电型沟道区采用集成工艺中高压增强型mosfet的漂移区掺杂结构,无需单独增加耗尽型沟道注入工序;所述第二导电型沟道区用于使耗尽型mosfet导通操作,且于耗尽状态下使耗尽型mosfet不导通操作。

10、在一种实施方式中,所述第二导电型连接区的掺杂结构与所述第二导电型沟道区相同,采用同一步工序完成,所述第二导电型连接区邻接于所述第二导电型沟道区和所述第二导电型漏极区。

11、在一种实施方式中,所述栅极绝缘膜和栅电极采用集成工艺中增强型mosfet的常规结构和工艺,提高耗尽型mosfet的可集成性。

12、本发明提供的一种易于集成的耗尽型mosfet器件结构,具有以下有益效果:

13、(1)耗尽型mosfet的沟道区工艺限制较少,可以采用集成工艺中其他中高压增强型mosfet的漂移区掺杂结构,不需要单独增加耗尽型沟道注入工序,简化了工艺步骤,提高了可集成性,特别适用于集成器件种类较多的bcd功率集成工艺;

14、(2)耗尽型mosfet的沟道区宽度小于源漏区宽度,沟道区被栅电极覆盖,沟道区宽度方向上的两侧阱区也被栅电极覆盖,沟道区的导电类型与阱区的导电类型是相反的,通过版图调整栅电极所覆盖的沟道区宽度与栅电极所覆盖的阱区宽度之比,可以调整耗尽型mosfet的开态饱和特性和关态漏电特性,不需要额外的工艺步骤;另外,根据器件电流要求,栅电极下方可以按照该宽度比布置多条沟道区;

15、(3)耗尽型mosfet不需要针对耗尽mosfet的栅极绝缘膜及栅电极做特殊结构和工艺调整,可以采用集成工艺中增强型mosfet的常规结构和工艺,提高了耗尽型mosfet的可集成性。

技术特征:

1.一种易于集成的耗尽型mosfet器件结构,包括半导体衬底,其特征在于,还包括第一导电型阱区和第二导电型沟道区;

2.如权利要求1所述的易于集成的耗尽型mosfet器件结构,其特征在于,根据器件电流要求,所述栅极绝缘膜的下方能够按照该宽度比布置多条第二导电型沟道区。

3.如权利要求2所述的易于集成的耗尽型mosfet器件结构,其特征在于,对于高压耗尽型mosfet,所述易于集成的耗尽型mosfet器件结构还包括第二导电型连接区,与所述第二导电型沟道区相邻接;其作用类比于高压器件的漂移区。

4.如权利要求3所述的易于集成的耗尽型mosfet器件结构,其特征在于,所述第二导电型沟道区的导电类型与所述第一导电型阱区的导电类型相反。

5.如权利要求3所述的易于集成的耗尽型mosfet器件结构,其特征在于,所述第二导电型沟道区采用集成工艺中高压增强型mosfet的漂移区掺杂结构,无需单独增加耗尽型沟道注入工序;所述第二导电型沟道区用于使耗尽型mosfet导通操作,且于耗尽状态下使耗尽型mosfet不导通操作。

6.如权利要求3所述的易于集成的耗尽型mosfet器件结构,其特征在于,所述第二导电型连接区的掺杂结构与所述第二导电型沟道区相同,采用同一步工序完成,所述第二导电型连接区邻接于所述第二导电型沟道区和所述第二导电型漏极区。

7.如权利要求3所述的易于集成的耗尽型mosfet器件结构,其特征在于,所述栅极绝缘膜和栅电极采用集成工艺中增强型mosfet的常规结构和工艺,提高耗尽型mosfet的可集成性。

技术总结

本发明公开一种易于集成的耗尽型MOSFET器件结构,属于MOSFET集成电路制造领域,第一导电型阱区形成于半导体衬底上,第二导电型沟道区形成于第一导电型阱区上;第二导电型沟道区上形成有栅极绝缘膜;在栅极绝缘膜上形成有栅电极;栅电极的两侧分别形成有第二导电型源极区和第二导电型漏极区;第二导电型源极区和第二导电型漏极区的宽度要分别大于第二导电型沟道区,第二导电型沟道区宽度方向上的两侧第一导电型阱区也被栅极绝缘膜覆盖,通过调整栅极绝缘膜所覆盖的第二导电型沟道区的宽度与所覆盖的第一导电型阱区的宽度比,调整耗尽型MOSFET的开态饱和特性和关态漏电特性。本发明与常规增强型MOSFET兼容、工艺流程简单,能够提高耗尽型MOSFET器件的可集成性。

技术研发人员:吴素贞,洪根深,徐政,徐海铭,郑若成,谢儒彬,张庆东

受保护的技术使用者:中国电子科技集团公司第五十八研究所

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!