重叠测量方法及使用该方法制造的半导体器件与流程

本公开涉及一种重叠测量方法和包括重叠键结构的半导体器件。

背景技术:

1、由于半导体器件的小型、多功能和/或低成本特性,半导体器件被认为是电子工业中的重要元件。半导体器件被分类为用于存储数据的半导体存储器件、用于处理数据的半导体逻辑器件、以及包括存储器和逻辑元件二者的混合半导体器件。随着电子工业的发展,对具有改进特性的半导体器件的需求不断增加。例如,对具有高可靠性、高性能、和/或多功能的半导体器件的需求不断增加。为了满足这种需求,可以增加半导体器件的结构复杂性和/或集成密度。

2、随着半导体器件的集成密度增加,形成在衬底的单位面积上的图案的密度增加。另外,由于需要具有多功能和高性能的半导体器件,在衬底上形成的层的数量增加。因此,应当执行半导体器件的制造工艺以在期望的位置处准确地形成图案。对准键或重叠键用于实现在衬底上堆叠的层之间的准确对准。

3、执行重叠测量工艺以检查在衬底上堆叠的下图案和上图案之间的失配程度。执行重叠测量工艺以从衬底的若干位置获得重叠测量值。在这种情况下,重叠测量值可能取决于测量位置。

技术实现思路

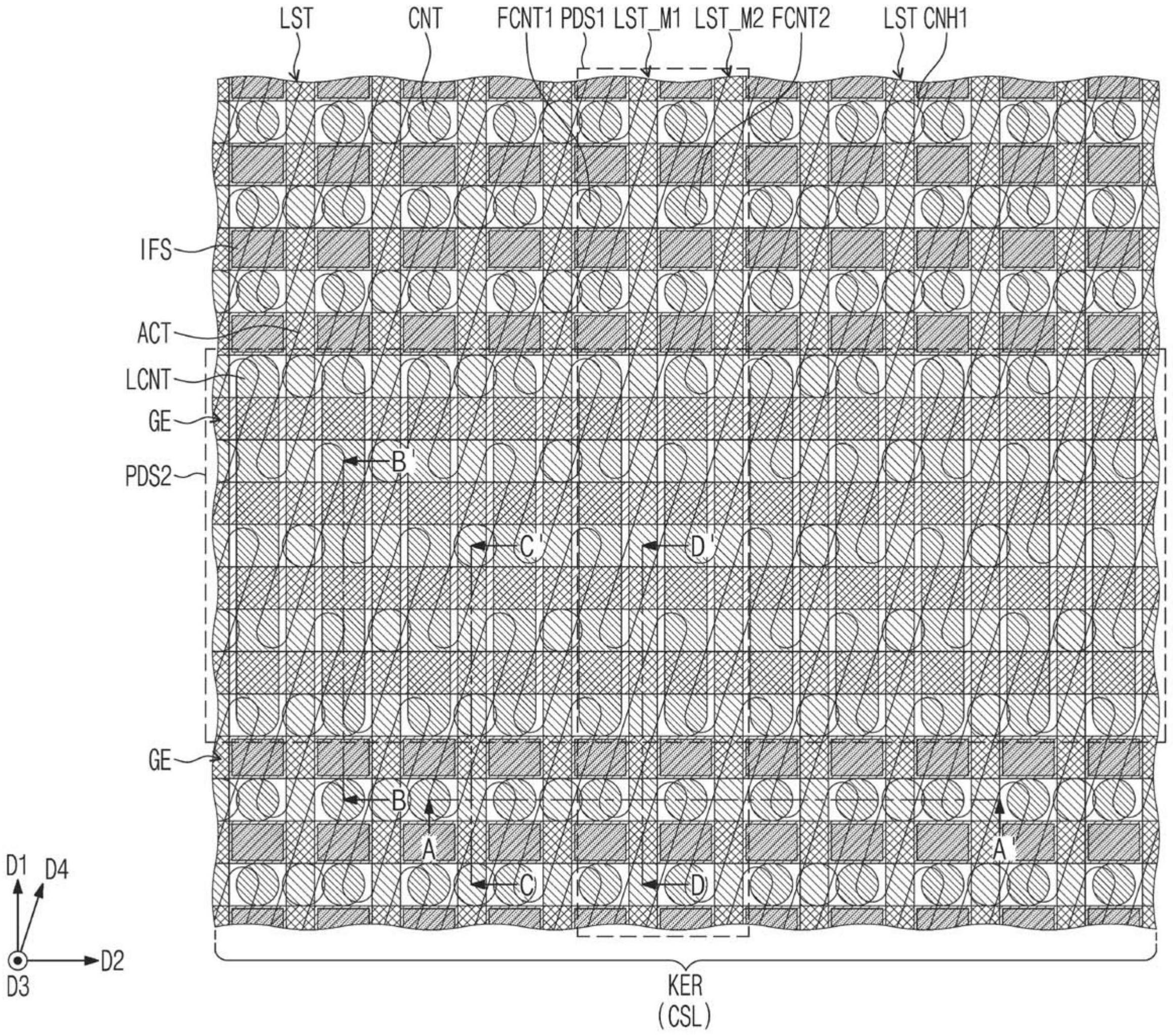

1、根据实施例,一种半导体器件可以包括:衬底,包括键区域;在键区域上的虚设有源图案,该虚设有源图案包括第一杂质区域和第二杂质区域;线结构,设置在第一杂质区域上并在第一方向上延伸;虚设栅电极,设置在第一杂质区域和第二杂质区域之间并在与第一方向交叉的第二方向上延伸;以及虚设接触部,被设置为与线结构的一侧相邻并连接到第二杂质区域。虚设接触部可以包括在第二方向上布置的多个长接触部。

2、根据实施例,一种半导体器件可以包括:衬底,包括键区域;下导电图案,在键区域上;以及上导电图案,与下导电图案相邻。上导电图案可以包括沿第一方向布置、并构成在第一方向上延伸的第一标记结构的第一编程(programmed)导电图案。上导电图案可以包括沿第二方向布置、并构成在第二方向上延伸的第二标记结构的第二编程导电图案。第一标记结构和第二标记结构可以被设置为彼此交叉,并且第一标记结构和第二标记结构中的每一个可以具有电压衬度(vc,voltage contrast)信号,当对其执行电子束检查时,该电压衬度(vc)信号总是被显示为亮或暗。

3、根据实施例,一种半导体器件可以包括:衬底,包括键区域;下导电图案,在键区域上;以及上导电图案,与下导电图案相邻。上导电图案可以包括虚设导电图案和第一编程导电图案,该虚设导电图案电连接到下导电图案中的对应下导电图案或与对应下导电图案电断开,该第一编程导电图案电连接到下导电图案中的对应下导电图案。第一编程导电图案可以包括沿第一方向布置的多个第一编程导电图案,并且第一编程导电图案可以构成在第一方向上延伸的第一标记结构。

4、根据实施例,一种重叠测量方法可以包括:在布局中放置下图案和上图案;通过编程失配(misalignment)来偏移下图案和上图案中的至少一个;在布局中添加编程标记;基于布局,在衬底的键区域上形成下导电图案、上导电图案和标记结构,该标记结构通过编程标记来形成;对键区域执行电子束检查以获得电压衬度(vc)图像,该vc图像包括作为标记结构的信号的参考标记;使用参考标记将vc图像的实际测量区域与布局进行匹配;以及获得键区域中的重叠值。

技术特征:

1.一种半导体器件,包括:

2.根据权利要求1所述的半导体器件,其中,所述至少一个线结构包括在所述第二方向上布置的多个线结构,所述多个长接触部和所述多个线结构在所述第二方向上交替布置。

3.根据权利要求2所述的半导体器件,其中,所述多个长接触部中的每一个长接触部电连接到所述多个线结构中的与该长接触部相邻的线结构。

4.根据权利要求1所述的半导体器件,其中:

5.根据权利要求1所述的半导体器件,其中,所述至少一个线结构包括电连接到所述第一杂质区域的接触部分,所述接触部分位于暴露所述第一杂质区域的接触孔中,并且所述接触孔在所述第二方向上从所述第一杂质区域偏移。

6.根据权利要求1所述的半导体器件,其中:

7.根据权利要求1所述的半导体器件,其中,所述多个长接触部在对其执行电子束检查时具有显示为常亮的电压衬度信号。

8.根据权利要求1所述的半导体器件,其中:

9.根据权利要求8所述的半导体器件,其中,所述多个编程接触部在对其执行电子束检查时具有显示为常暗的电压衬度信号。

10.根据权利要求8所述的半导体器件,其中:

11.一种半导体器件,包括:

12.根据权利要求11所述的半导体器件,其中,所有第一编程导电图案分别电连接到所述下导电图案中的对应下导电图案。

13.根据权利要求11所述的半导体器件,其中,所有第一编程导电图案分别与所述下导电图案中的对应下导电图案电断开。

14.根据权利要求11所述的半导体器件,其中,所有第二编程导电图案分别电连接到所述下导电图案中的对应下导电图案。

15.根据权利要求11所述的半导体器件,其中,所有第二编程导电图案分别与所述下导电图案中的对应下导电图案电断开。

16.一种半导体器件,包括:

17.根据权利要求16所述的半导体器件,其中,所述多个第一编程导电图案中的每一个具有大于所述虚设导电图案的延伸长度。

18.根据权利要求16所述的半导体器件,其中:

19.根据权利要求18所述的半导体器件,其中:

20.根据权利要求19所述的半导体器件,其中,所述第一标记结构和所述第二标记结构用作所述vc信号的参考标记。

技术总结

一种半导体器件包括:衬底,具有键区域;在键区域上的虚设有源图案,该虚设有源图案包括第一杂质区域和第二杂质区域;线结构,设置在第一杂质区域上并在第一方向上延伸;虚设栅电极,设置在第一杂质区域和第二杂质区域之间并在与第一方向交叉的第二方向上延伸;以及虚设接触部,被设置为与线结构的一侧相邻并连接到第二杂质区域。虚设接触部包括在第二方向上布置的多个长接触部。

技术研发人员:李茂松,金真善,郭仁浩,朴道炫,韩睿恩,尹详皓,李承润,金暖莹

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!