封装结构及形成方法与流程

本发明涉及芯片封装,特别是封装结构及形成方法。

背景技术:

1、随着先进封装技术的不断演进,chiplet(芯粒)封装越来越得到广泛的应用。通过chiplet技术,可以把异质或者同质芯片进行组合,最终实现功能叠加或者微系统集成。

2、在chiplet封装时,电感类器件一般作为分立器件贴附在基板或印刷电路板上,这种电感类器件的安装方式浪费封装面积,使封装后的封装结构的尺寸增大。

技术实现思路

1、本发明的目的是提供一种封装结构,以解决现有技术中的不足,它能够在不影响电感线圈性能的前提下将电感线圈与芯片的再布线工艺进行结合,从而提升了芯片封装结构的集成度,减少了封装结构的整体尺寸。

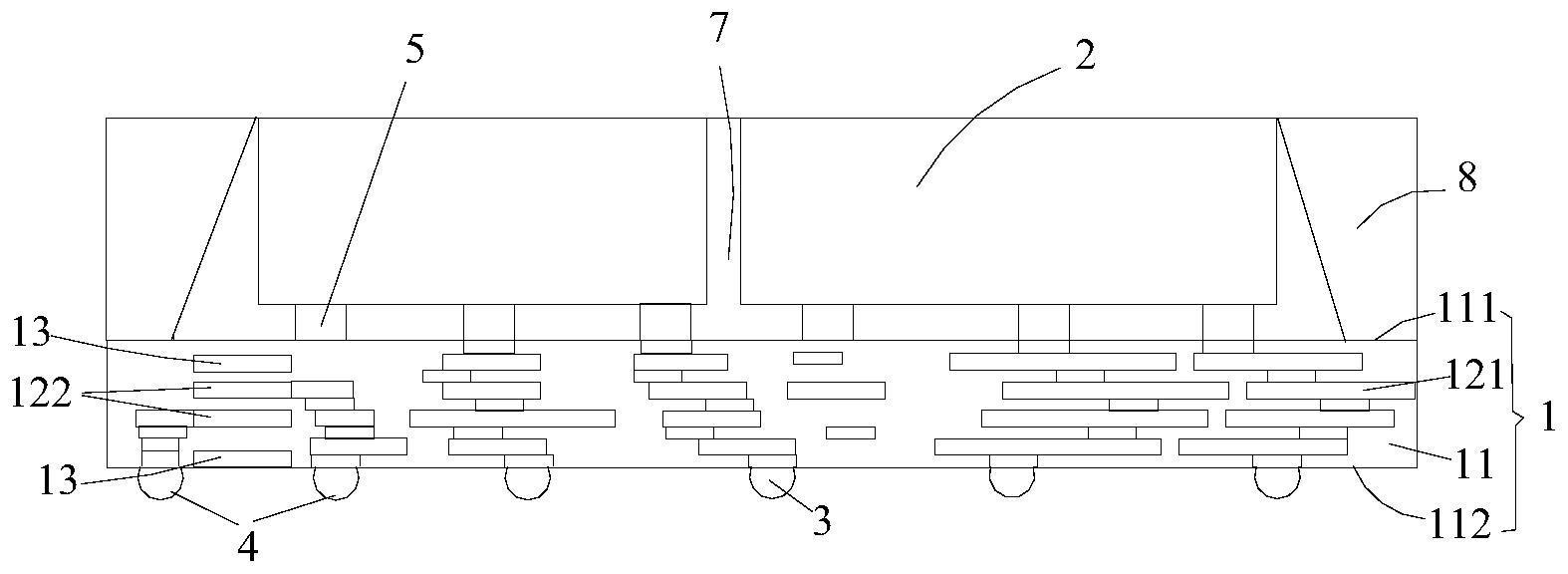

2、本发明提供的封装结构,包括:再布线结构,具有绝缘体和嵌设于绝缘体内的若干图案化金属层,至少一所述图案化金属层具有布线线路和形成电感线圈的电感线路;所述再布线结构还包括磁性薄膜层,在再布线结构厚度方向上,所述磁性薄膜层设置于电感线圈的至少一侧;

3、芯片,设置于所述再布线结构沿厚度方向的一侧并与所述布线线路电性连接。

4、进一步的,在再布线结构的厚度方向上,所述电感线圈的位置与所述磁性薄膜层位置相对。

5、进一步的,所述磁性薄膜层嵌设于所述绝缘体内,所述磁性薄膜层与所述电感线圈之间通过部分所述绝缘体分隔。

6、进一步的,所述绝缘体具有背向设置的第一表面和第二表面;所述磁性薄膜层设置于所述第一表面、所述第二表面中的至少一个。

7、进一步的,所述磁性薄膜层设置有至少两层,所述电感线圈设置在两层所述磁性薄膜层之间。

8、进一步的,所述电感线圈也设置有至少两层;

9、在再布线结构厚度方向上,所述电感线圈与所述磁性薄膜层交替设置。

10、进一步的,所述磁性薄膜层为含铁金属薄膜层、或含镍金属薄膜层、或含钴金属薄膜层、或含铁镍合金薄膜层、或含铁钴合金薄膜层、或含镍钴合金薄膜层、或含铁镍钴合金薄膜层中的一种或多种的叠加。

11、进一步的,所述封装结构还具有金属凸块,所述金属凸块设置在所述再布线结构背离所述芯片的一侧,所述金属凸块与所述布线线路电性连接;

12、所述封装结构还具有电感凸块,所述电感凸块设置在所述再布线结构背离所述芯片的一侧,所述电感凸块与所述电感线圈电性连接;所述电感线圈与所述布线线路之间通过部分所述绝缘体分隔。

13、进一步的,所述芯片包括并列设置在所述再布线结构一侧的第一芯片和第二芯片;

14、所述封装结构还包括:

15、桥接芯片,设置在所述再布线结构背离所述芯片的一侧并分别与所述第一芯片、所述第二芯片电性连接;

16、桥接芯片保护层,设置在所述绝缘体的第二表面并覆盖所述桥接芯片,所述桥接芯片保护层上设置有贯穿所述桥接芯片保护层的保护层通孔;

17、导电凸块,设置在所述保护层通孔内并电性连接所述布线线路。

18、进一步的,所述封装结构还具有金属凸块,所述金属凸块设置在所述桥接芯片保护层背离所述绝缘体的一侧,所述金属凸块与所述导电凸块电性连接。

19、进一步的,所述封装结构还包括:

20、底部再布线层,设置在所述桥接芯片保护层背离所述绝缘体的一侧,并具有底绝缘层和设置在底绝缘层内的底金属层;

21、所述金属凸块与所述导电凸块相对设置在所述底部再布线层的两侧并通过所述底金属层电性连接。

22、本发明另一实施例还公开了一种所述的封装结构的形成方法,包括如下步骤:

23、提供承载基板,并在所述承载基板的一侧设置结合层;

24、在所述结合层背离所述承载基板的一侧形成所述再布线结构,其中,所述再布线结构具有绝缘体和嵌设于绝缘体内的若干图案化金属层,至少一所述图案化金属层包括布线线路和形成电感线圈的电感线路;

25、将芯片与所述布线线路电性连接;

26、去除所述承载基板及所述结合层。

技术特征:

1.一种封装结构,其特征在于,包括:

2.根据权利要求1所述的封装结构,其特征在于,在再布线结构的厚度方向上,所述电感线圈的位置与所述磁性薄膜层位置相对。

3.根据权利要求1所述的封装结构,其特征在于,所述磁性薄膜层嵌设于所述绝缘体内,所述磁性薄膜层与所述电感线圈之间通过部分所述绝缘体分隔。

4.根据权利要求1所述的封装结构,其特征在于,所述绝缘体具有背向设置的第一表面和第二表面;所述磁性薄膜层设置于所述第一表面、所述第二表面中的至少一个。

5.根据权利要求1至4任一项所述的封装结构,其特征在于,所述磁性薄膜层设置有至少两层,所述电感线圈设置在两层所述磁性薄膜层之间。

6.根据权利要求5所述的封装结构,其特征在于,所述电感线圈也设置有至少两层;

7.根据权利要求1至4任一项所述的封装结构,其特征在于,所述磁性薄膜层为含铁金属薄膜层、或含镍金属薄膜层、或含钴金属薄膜层、或含铁镍合金薄膜层、或含铁钴合金薄膜层、或含镍钴合金薄膜层、或含铁镍钴合金薄膜层中的一种或多种的叠加。

8.根据权利要求1所述的封装结构,其特征在于,所述封装结构还具有金属凸块,所述金属凸块设置在所述再布线结构背离所述芯片的一侧,所述金属凸块与所述布线线路电性连接;

9.根据权利要求1所述的封装结构,其特征在于,所述芯片包括并列设置在所述再布线结构一侧的第一芯片和第二芯片;

10.根据权利要求9所述的封装结构,其特征在于,所述封装结构还具有金属凸块,所述金属凸块设置在所述桥接芯片保护层背离所述绝缘体的一侧,所述金属凸块与所述导电凸块电性连接。

11.根据权利要求10所述的封装结构,其特征在于,所述封装结构还包括:

12.一种如权利要求1至11任一项所述的封装结构的形成方法,其特征在于,包括如下步骤:

技术总结

本发明公开了封装结构及形成方法,其中,封装结构包括:再布线结构和芯片,再布线结构具有绝缘体和嵌设于绝缘体内的若干图案化金属层,至少一图案化金属层具有布线线路和形成电感线圈的电感线路;再布线结构还包括磁性薄膜层,在再布线结构厚度方向上,磁性薄膜层设置于电感线圈的至少一侧;芯片设置于再布线结构沿厚度方向的一侧并与布线线路电性连接。本发明的实施例将电感线圈与再布线工艺结合,使电感线圈封装在再布线结构的绝缘体内,从而实现了电感线圈与芯片封装结构的集成,通过磁性薄膜层的设置消除了电感线圈在集成设置后性能的减弱,提高了封装结构的集成度,减少了封装后封装结构的尺寸。

技术研发人员:陈海杰,刘涛,王长文

受保护的技术使用者:江阴长电先进封装有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!