形成基于3C-SiC的电子器件以及3C-SiC电子器件的制作方法

本公开涉及至少部分地以3c-sic形成的电子器件以及用于制造3c-sic电子器件的方法。

背景技术:

1、如已知的,具有宽带隙,特别是具有大于1.1ev的带隙能量值eg,低导通状态电阻(ron)、高热导率值、高工作频率和高电荷载流子饱和速度的半导体材料对于生产电子元件,例如二极管或晶体管,特别是用于功率应用是理想的。具有所述特性并设计用于制造电子元件的材料是碳化硅(sic)。碳化硅具有不同的晶体形式,也称为多型。最常见的多型是立方多型(多型3c-sic),六方多型(多型4h-sic和6h-sic)和菱形多型(多型15r-sic)。

2、与设置在硅衬底上的类似器件相比,设置在碳化硅衬底上的电子器件具有许多优点,例如传导中的低输出电阻、低泄漏电流、高工作温度和高工作频率。特别地,sic肖特基二极管已经表现出更高的开关性能,使得sic电子器件特别有利于高频应用。当前的应用对器件的电性能以及长期可靠性提出了要求。

3、由于相对于其它多型更容易制造,4h-sic通常用作衬底。然而,相对于3c-sic(2.3ev)或硅(1.12ev)的相应带隙,4h-sic的带隙较大(3.2ev),使得4h-sic相对于3c-sic或相对于硅对一些电子应用的吸引力较小。例如,在肖特基势垒二极管的情况下,控制肖特基势垒高度(sbh)值的可能性是重要的方面,以便降低能耗并使传导损耗最小化。为此,相对于金属/4h-sic接触的sbh值,金属/3c-sic或金属/si接触的实施导致更低的sbh值,使得能够制造更有效的肖特基二极管。

4、此外,sic的击穿电压也大于硅的击穿电压。这是由于碳化硅的临界电场大约是硅的十倍。通常,与在4h-sic的衬底(体)上制造器件相关的另一优点是保持击穿电压的优点,但在表面上具有较低带隙的材料(例如,硅或3c-sic),使得例如肖特基接触的势垒高度降低。换句话说,期望保持反向偏置的优点并优化正向偏置的电压降。

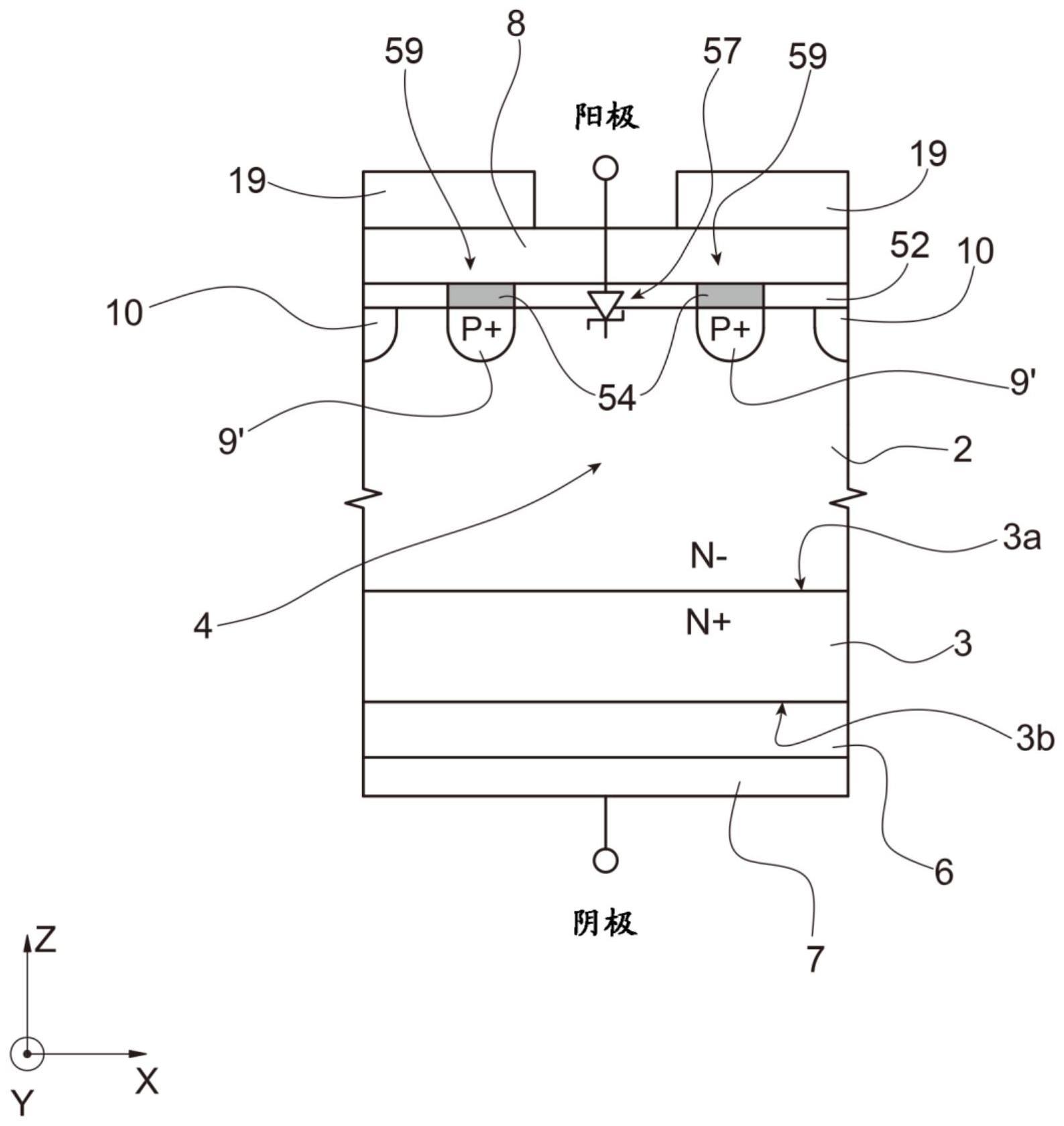

5、图1示出了在x,y,z轴的笛卡尔(三轴)参考系中的横向截面图,结势垒肖特基(jbs)器件,或类似的合并pn肖特基(mps)二极管,用附图标记1表示。图1的器件不一定是现有技术,并且在下文中将参考jbs器件1而不因此失去一般性。

6、jbs器件1包括:n型掺杂的4h-sic的衬底3,具有第一掺杂剂浓度(例如,包括在1·1019和1·1022原子/cm3之间),包括例如在2mω〃cm和40mω〃cm之间的电阻率,具有与表面3b相对的表面3a,以及包括在50μm和350μm之间,更特别地在160μm和200μm之间,例如等于180μm的厚度;漂移层(外延生长)2,由n型4h-sic制成,具有低于第一掺杂剂浓度的第二掺杂剂浓度(例如包括在1014和1016原子/cm3之间),其在衬底3的表面3a上延伸,并且厚度包括在5μm和15μm之间;欧姆接触区域6(例如硅化镍),其在衬底3的表面3b上延伸;阴极金属化7,例如ti/niv/ag或ti/niv/au,其在欧姆接触区域6上延伸;阳极金属化8,例如ti/alsicu或ni/alsicu,其在漂移层2的顶表面2a上延伸;阳极金属化8上的钝化层19,以保护阳极金属化;漂移层2中的多个结势垒(jb)元件9,面向漂移层2的顶表面2a,并且每个结势垒元件9包括相应的p型注入区域9'和欧姆接触9";以及边缘终结区域或保护环10(可选),特别是p型注入区域,其围绕(完全或部分地,取决于设计选择)jb元件9。

7、肖特基二极管12形成在漂移层2和阳极金属化8之间的界面处。特别地,肖特基(半导体-金属)结由漂移层2的与阳极金属化8的相应部分直接电接触的部分形成。

8、包括jb元件9和肖特基二极管12的jbs器件1的区域(即,包含在保护环10内的区域)是jbs器件1的激活区4。

9、参考图2a和2b,图1的jbs器件1的制造步骤(图2a)提供了在漂移层2中掩模注入具有第二导电类型(p)的掺杂物质(例如硼或铝)的步骤。图2a中的箭头18示出了注入。掩模11用于注入,特别是氧化硅或teos的硬掩模。在示例性实施例中,注入步骤包括具有第二导电类型的掺杂物质的一个或多个注入,注入能量在30kev和400kev之间,剂量在1〃1012原子/cm2和1〃1015原子/cm2之间。

10、由此形成注入区域9'和边缘终结区域10。注入区域9'和边缘终结区域10具有从表面2a测量的包括在0.2μm和1μm之间的深度。

11、然后,在图2b中,去除掩模11,并执行热退火步骤以激活在图2a的步骤中注入的掺杂物质。热退火例如在高于1600℃(例如,1700-1900℃,在一些情况下甚至更高)的温度下在炉中执行。

12、参考图3a-3c,然后执行另外的步骤以形成欧姆接触9"。参考图3a,形成氧化硅或teos的沉积掩模13,以覆盖漂移层2的除了注入区域9'之外的表面区域(以及边缘终端10的表面区域,如果有的话)。换句话说,掩模13在注入区域9'处(并且可选地在边缘终端10的至少一部分处)具有贯通开口13a。然后,在图3b中,在掩模13上和贯通开口13a(图3b中的金属层14)内执行镍沉积。这样沉积的镍通过贯通开口13a到达并接触注入区域9'和边缘终结区域10。

13、参考图3c,随后的高温热退火(在700℃和1200℃之间,时间间隔从1分钟到120分钟)允许通过在贯通开口13a处沉积的镍和漂移层2的碳化硅(4h-sic)之间的化学反应形成硅化镍的欧姆接触9"。实际上,沉积的镍在与漂移层2的表面材料接触的地方反应,形成ni2si(即欧姆接触)。随后,执行去除在掩模13上方延伸的金属的步骤和掩模13的去除。

14、在形成欧姆接触之后,该方法继续在漂移层2的顶表面2a上并与欧姆接触9"直接电接触地形成(例如通过沉积)阳极金属化8,例如ti/alsicu或ni/alsicu。然后,在阳极金属化层8上形成钝化层19,以保护阳极金属化。因此,相应的肖特基二极管12形成在漂移层2和阳极金属化8之间的界面处,横向于注入区域9'。特别地,肖特基(半导体-金属)结由漂移层2的在jb元件9之间的与阳极金属化8的相应部分直接电接触的部分形成。

技术实现思路

1、本公开的目的是提供至少部分地以3c-sic形成的电子器件和用于制造3c-sic电子器件的方法,以克服现有技术的缺点。

2、根据本公开,提供了一种如所附权利要求中限定的用于制造电子器件的方法和电子器件。

3、在一个实施例中,用于制造电子器件的方法包括在具有第一电导性的4h-sic固态主体的前侧形成具有与第一电导性相对的第二电导性的至少一个注入区域。该方法包括在前侧上形成3c-sic层,以及在3c-sic层中形成延伸穿过3c-sic层的整个厚度直到到达注入区域的欧姆接触区域。

4、在一个实施例中,电子器件包括具有第一电导性的4h-sic固态主体。该电子器件包括至少一个注入区域,该注入区域具有在固态主体的前侧延伸的与第一电导性相对的第二电导性。该电子器件包括在前侧上的3c-sic层和穿过3c-sic层的整个厚度直到到达注入区域的欧姆接触区域。

- 还没有人留言评论。精彩留言会获得点赞!