半导体器件及其制备方法与流程

本申请涉及集成电路,特别是涉及一种半导体器件及其制备方法。

背景技术:

1、随着半导体技术的发展,电子设备向着体积逐渐减小而效率相应提高的方向发展,沟槽金属氧化物半导体场效应晶体管(metal-oxide-semiconductor field-effecttransistor, 简称mosfet或mos)技术正是在这样的背景下发展起来的。沟槽mos管因其具有垂直结构,具备开关速度快、温度特性好、频率性能好、输入阻抗高、驱动功率小、无二次击穿问题等优点,可广泛应用在电源管理模块、稳压器、机电控制、显示控制和汽车电子等领域。

2、然而,在沟槽mos管的沟槽内中填入栅极时,容易出现空洞或缝隙,此缺陷将造成后续工艺制作上的异常进而造成产品电性或良率异常。

技术实现思路

1、基于此,有必要针对现有技术中栅极容易出现空洞或缝隙的问题,提供一种半导体器件及其制备方法,以避免栅极出现空洞或缝隙,保证半导体器件的电性参数和产品良率。

2、为了实现上述目的,一方面,本申请提供了一种半导体器件,包括:

3、衬底,所述衬底中开设有沟槽;

4、非共形衬垫应用层,位于所述衬底上表层和所述沟槽的第一槽壁上,其中,所述第一槽壁为靠近所述衬底上表层的部分槽壁;

5、栅氧化层,位于所述非共形衬垫应用层上和所述沟槽的第二槽壁以及槽底,其中,所述第一槽壁与所述第二槽壁相邻接;

6、栅极,位于所述栅氧化层上,并填充于所述沟槽内。

7、在其中一个实施例中,所述栅氧化层包括第一子氧化层和第二子氧化层,其中,所述第一子氧化层位于所述非共形衬垫应用层上,所述第二子氧化层位于所述沟槽的槽底以及第二槽壁,所述第一子氧化层的厚度小于所述第二子氧化层的厚度。

8、在其中一个实施例中,所述第二子氧化层的厚度为50埃至700埃。

9、在其中一个实施例中,位于所述第一槽壁的所述非共形衬垫应用层的深度与所述沟槽总深度的比值小于或等于80%。

10、在其中一个实施例中,位于所述第一槽壁的所述非共形衬垫应用层的深度为1纳米至800纳米。

11、在其中一个实施例中,所述非共形衬垫应用层的厚度为50埃至700埃。

12、在其中一个实施例中,所述沟槽的开口宽度为5纳米至200纳米。

13、在其中一个实施例中,所述非共形衬垫应用层的材料包括硅氮化物、硅氮氧化物和硅氧化物中的至少一种。

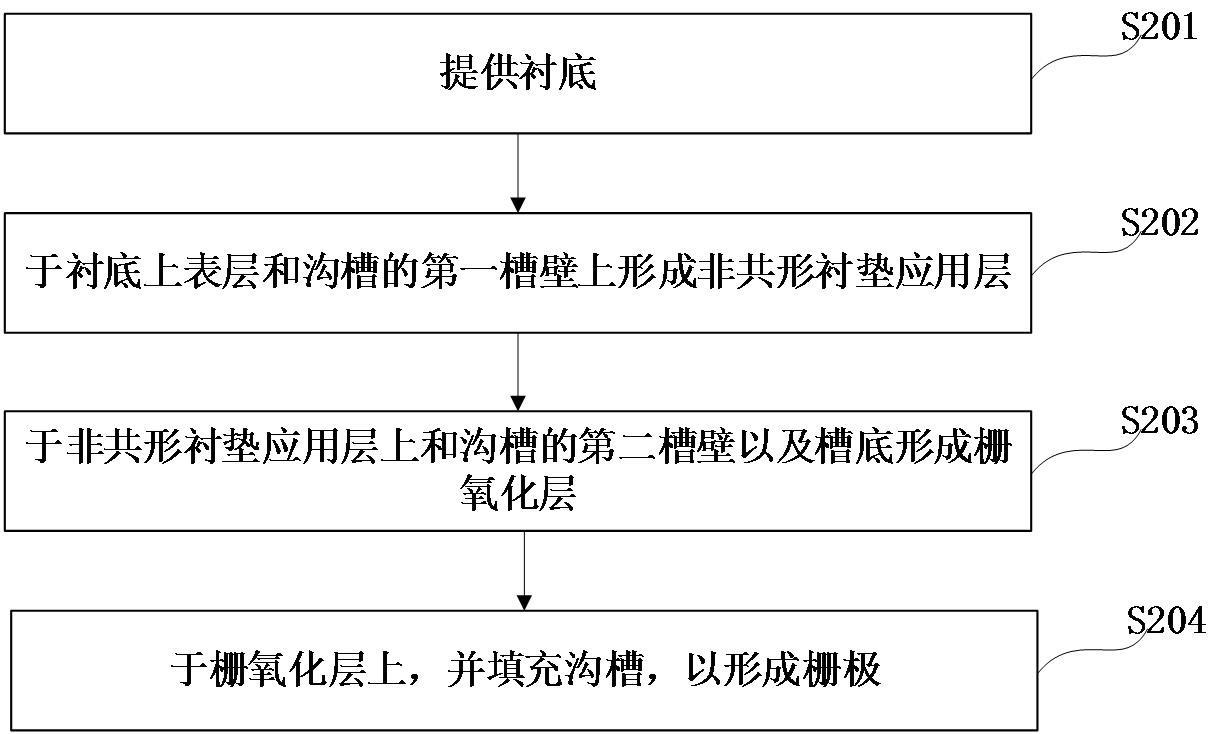

14、另一方面,本申请还提供了一种半导体器件的制备方法,包括:

15、提供衬底,所述衬底中开设有沟槽;

16、于所述衬底上表层和所述沟槽的第一槽壁上形成非共形衬垫应用层,其中,所述第一槽壁为靠近所述衬底上表层的部分槽壁;

17、于所述非共形衬垫应用层上和所述沟槽的第二槽壁以及槽底形成栅氧化层,其中,所述第一槽壁与所述第二槽壁相邻接;

18、于所述栅氧化层上,并填充所述沟槽,以形成栅极。

19、在其中一个实施例中,所述于所述衬底上表层和所述沟槽的第一槽壁上形成非共形衬垫应用层,包括:

20、采用至少一次原子层沉积,于所述衬底上表层和所述沟槽的第一槽壁上形成非共形衬垫应用层;其中,位于所述第一槽壁上的所述非共形衬垫应用层的深度与所述原子层沉积的脉冲时间和流量正相关。

21、上述半导体器件及其制备方法,在形成栅氧化层前,于衬底上表层和沟槽的第一槽壁上形成非共形衬垫应用层。由于非共形衬垫应用层与衬底材质不同,因此,两者对于栅氧化层的长膜速率存在差异。具体而言,相对于在衬底上生长栅氧化层,非共形衬垫应用层能够抑制栅氧化层的生长,因此,位于非共形衬垫应用层上的栅氧化层厚度要小于位于衬底上的栅氧化层厚度,由此在沟槽内填入栅极时不会提早封口造成空洞或缝隙,从而能够保证半导体器件的电性参数和产品良率。

技术特征:

1.一种半导体器件,其特征在于,包括:

2.根据权利要求1所述的半导体器件,其特征在于,所述栅氧化层包括第一子氧化层和第二子氧化层,其中,所述第一子氧化层位于所述非共形衬垫应用层上,所述第二子氧化层位于所述沟槽的槽底以及第二槽壁,所述第一子氧化层的厚度小于所述第二子氧化层的厚度。

3.根据权利要求2所述的半导体器件,其特征在于,所述第二子氧化层的厚度为50埃至700埃。

4.根据权利要求1所述的半导体器件,其特征在于,位于所述第一槽壁的所述非共形衬垫应用层的深度与所述沟槽总深度的比值小于或等于80%。

5.根据权利要求4所述的半导体器件,其特征在于,位于所述第一槽壁的所述非共形衬垫应用层的深度为1纳米至800纳米。

6.根据权利要求1所述的半导体器件,其特征在于,所述非共形衬垫应用层的厚度为50埃至700埃。

7.根据权利要求1所述的半导体器件,其特征在于,所述沟槽的开口宽度为5纳米至200纳米。

8.根据权利要求1所述的半导体器件,其特征在于,所述非共形衬垫应用层的材料包括硅氮化物、硅氮氧化物和硅氧化物中的至少一种。

9.一种半导体器件的制备方法,其特征在于,包括:

10.根据权利要求9所述的半导体器件的制备方法,其特征在于,所述于所述衬底上表层和所述沟槽的第一槽壁上形成非共形衬垫应用层,包括:

技术总结

本发明涉及一种半导体器件及其制备方法,其中,半导体器件包括设有沟槽的衬底、非共形衬垫应用层、栅氧化层和栅极。在形成栅氧化层前,于衬底上表层和沟槽的第一槽壁上形成非共形衬垫应用层。由于非共形衬垫应用层与衬底材质不同,因此,两者对于栅氧化层的长膜速率存在差异。具体而言,相对于在衬底上生长栅氧化层,非共形衬垫应用层能够抑制栅氧化层的生长,因此,位于非共形衬垫应用层上的栅氧化层厚度要小于位于衬底上的栅氧化层厚度,由此在沟槽内填入栅极时不会提早封口造成空洞或缝隙,从而能够保证半导体器件的电性参数和产品良率。

技术研发人员:李昇聪,陈宣宇

受保护的技术使用者:合肥新晶集成电路有限公司

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!