一种半导体器件、半导体阵列和电子设备的制作方法

本技术涉及半导体领域,并且更具体地,涉及一种半导体器件、半导体阵列和电子设备。

背景技术:

1、随着技术发展,电子产品朝着小型化、高速率和大容量持续演进,对在电子产品中应用的半导体器件的要求也越来越高。沟槽型半导体场效应晶体管(metal-oxide-semiconductor field-effect transistor,mosfet)具有高击穿电压、低导通压降等特性得到了广泛的运行。

2、当半导体器件工作在阻断模式时,半导体器件的栅极电介质层处存在较高的栅氧电场。半导体器件长期在较高的栅氧电场的情况下进行工作,会使得半导体器件无法正常工作的风险增大,降低半导体器件工作的可靠性。

3、因此,亟需一种半导体器件、半导体阵列和电子设备,能够降低半导体器件工作时的栅氧电场,提高半导体器件工作的可靠性。

技术实现思路

1、本技术提供一种半导体器件、半导体阵列和电子设备,能够降低半导体器件工作时的栅氧电场,提高半导体器件工作的可靠性。

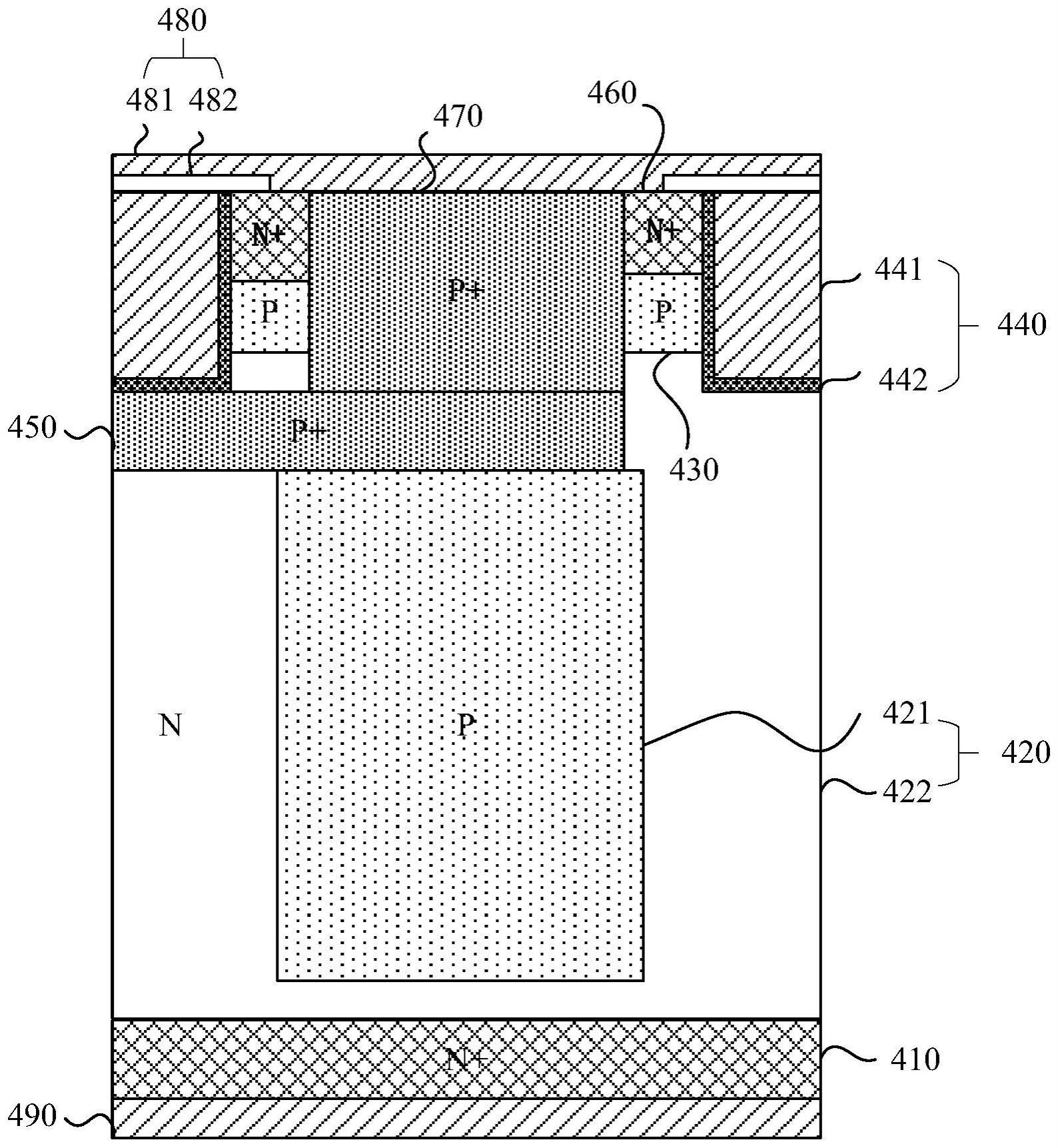

2、第一方面,提供了一种半导体器件,该半导体器件可以包括衬底410、外延层420、第一掺杂区430、多个沟槽结构440和第二掺杂区450。其中,外延层420设置于衬底410上。第一掺杂区430设置于外延层420远离衬底410的一面。多个沟槽结构440,位于半导体器件的边缘,贯穿第一掺杂区430和部分外延层420。每一个沟槽结构440包括栅极电介质层442和栅极441,栅极电介质层442覆盖沟槽结构440的槽底和槽壁,栅极441设置于栅极电介质层442远离槽底的一面。第二掺杂区450设置于外延层420的内部,第二掺杂区450的侧面露出于外延层420的侧面,第二掺杂区450与栅极电介质层442位于槽底的一面接触。其中,衬底410的掺杂类型为第一类型。第一掺杂区430和第二掺杂区450的掺杂类型为第二类型,外延层420包含掺杂类型为第一类型的纵向掺杂区,纵向掺杂区连接第一掺杂区430和衬底410。

3、基于本技术方案,通过设置与栅极电介质层442相接触的第二掺杂区450,可以减小栅极电介质层442的电场,能够提高半导体器件工作的可靠性。并且,第二掺杂区450露出于半导体器件的侧面,当半导体器件应用于半导体阵列时,能够减小相邻半导体器接触位置的栅极电介质层442的电场,提高半导体器件工作的可靠性。

4、结合第一方面,在第一方面的某些实现方式中,第二掺杂区450在水平方向上从外延层420的中心向外延层420的边缘延伸。

5、基于本技术方案,从中心向边缘发散的第二掺杂区450结构能够有效降低栅极电介质层442处的电场,进一步提高半导体器件工作的可靠性。

6、结合第一方面,在第一方面的某些实现方式中,外延层420的水平截面呈多边形,第二掺杂区450的水平截面包含中心区域和至少一个放射区域,每一个放射区域连接第二掺杂区450的水平截面的中心区域和外延层420的水平截面的一个边,放射区域的数量小于多边形的边数。

7、基于本技术方案,部分栅极电介质层442与第二掺杂区450接触,部分栅极电介质层442直接与外延层420接触,能够既减小栅极电介质层442处的电场,也支持半导体器件中源极481与漏极490之间的导通。

8、结合第一方面,在第一方面的某些实现方式中,至少一个放射区域中每两个放射区域连接的外延层420的水平截面的两个边不相邻。

9、基于本技术方案,这种设计能够提高半导体器件的对称性,使得半导体周围的栅极电介质层442均匀的与第二掺杂区450接触,能够提高半导体器件工作的可靠性。

10、结合第一方面,在第一方面的某些实现方式中,多边行的每一条边设置有沟槽结构440。

11、结合第一方面,在第一方面的某些实现方式中,第二掺杂区450中第二类型的掺杂浓度高于外延层420中第二类型的掺杂浓度。

12、结合第一方面,在第一方面的某些实现方式中,外延层420包含多个纵向掺杂区,多个纵向掺杂区沿水平方向排列,多个纵向掺杂区中的相邻两个纵向掺杂区的掺杂类型不同。

13、基于本技术方案,外延层420可以呈多个纵向掺杂区交替排列的超结结构,能够利用电荷耦合原理突破半导体器件导通电阻与击穿电压之间的理论极限,降低半导体器件的导通电阻,提高半导体器件的性能。

14、结合第一方面,在第一方面的某些实现方式中,外延层420包含第一纵向掺杂区421和第二纵向掺杂区422,第二纵向掺杂区422围绕第一纵向掺杂区421设置,第一纵向掺杂区421的掺杂类型为第二类型,第二纵向掺杂区422的掺杂类型为第一类型。

15、结合第一方面,在第一方面的某些实现方式中,半导体器件还包括第三掺杂区460、第四掺杂区470和顶部结构480。第三掺杂区460设置于第一掺杂区430远离外延层420的一面,第三掺杂区460的掺杂类型为第一类型。第四掺杂区470位于第三掺杂区460上的中心区域,贯穿第三掺杂区460、第一掺杂区430和部分外延层420,第四掺杂区470的掺杂类型为第二类型。顶部结构480设置于多个沟槽结构440、第三掺杂区460和第四掺杂区470远离外延层420的一面。顶部结构480包括源极481和多个层间介质层482,多个层间介质层482分别用于隔离多个栅极441和源极481。

16、结合第一方面,在第一方面的某些实现方式中,半导体器件还包括漏极490。漏极490设置于衬底410远离外延层420的一面。

17、第二方面,提供了一种半导体阵列,该半导体阵列包括多个第一半导体器件,每一个第一半导体器件为如第一方面或第一方面任一实现方式的半导体器件。多个第一半导体器件沿水平方向排列。

18、关于第二方面技术效果的描述可以参考第一方面的描述,不予赘述。

19、结合第二方面,在第二方面的某些实现方式中,多个第一半导体器件中一组相邻的半导体器件包括具有第一接触面的两个第一半导体器件,两个第一半导体器件的第二掺杂区不通过第一接触面接触。

20、结合第二方面,在第二方面的某些实现方式中,半导体阵列还包括多个第二半导体器件,每一个第二半导体器件包括衬底、外延层、第一掺杂区和多个沟槽结构。外延层设置于衬底上。第一掺杂区设置于外延层远离衬底的一面。多个沟槽结构位于第一半导体器件的边缘,贯穿第一掺杂区和部分外延层。每一个沟槽结构包括栅极电介质层和栅极,栅极电介质层覆盖沟槽结构的槽底和槽壁,栅极位于栅极电介质层远离槽底的一面。其中,衬底和第二掺杂区的掺杂类型为第一类型。第一掺杂区的掺杂类型为第二类型,外延层包含掺杂类型为第一类型的纵向掺杂区,该纵向掺杂区连接第一掺杂区和衬底。其中,一组相邻的半导体器件包括至少一个所述第一半导体器件和至少一个所述第二半导体器件。

21、第三方面,提供了一种电子设备,包括电路板和如第一方面或第一方面任一实现方式的半导体器件,半导体器件设置于电路板上。

22、第四方面,提供了一种电子设备,包括电路板和如第二方面或第二方面任一实现方式的半导体阵列,半导体阵列设置于电路板上。

- 还没有人留言评论。精彩留言会获得点赞!